ADC – SCHEMA GENERALE I convertitori AD sono disponibili come circuiti integrati in diversi modelli, che differiscono fra loro per prezzo, prestazioni e utilizzi. Al loro interno essi contengono sempre: un campionatore un quantizzatore un codificatore A seconda dei casi i convertitori AD commerciali possono comprendere anche: un blocco di sample & hold un filtro anti-alias un multiplexer 1 ADC – SCHEMA GENERALE 2 ADC – SCHEMA GENERALE Vin - segnale analogico da convertire. In alcuni convertitori sono presenti due piedini separati, Vin+ e Vin-: in questo caso il segnale viene applicato in modo differenziale, cioè senza riferimento a massa; digital outputs sono le uscite digitali, in numero pari al numero di bit del convertitore; alcuni convertitori presentano un'uscita seriale e dunque hanno un solo piedino di uscita; SOC (start of conversion) è un segnale logico di ingresso mediante il quale è possibile avviare una conversione - in alcuni convertitori il nome usato è WR (write); EOC (end of conversion) è un segnale logico di uscita che segnala il termine di una conversione - in alcuni convertitori viene usato il nome INTR (interrupt), perché questo segnale viene usato per richiedere un interrupt al microprocessore alla fine di ogni 3 conversione; ADC – SCHEMA GENERALE CS (chip select) è un segnale logico che abilita il funzionamento dell'integrato; RD è un segnale logico che abilita le uscite digitali (digital inputs) se disattivato, le uscite si portano in uno stato di alta impedenza; in alcuni convertitori viene chiamato Output Enable (OE). Vref+ e Vref- servono per regolare la tensione superiore e la tensione inferiore di fondo scala; clock è un segnale logico di clock che serve in alcuni convertitori per temporizzare le operazioni interne; Vcc e -Vcc sono rispettivamente la doppia alimentazione, positiva e negativa. In alcuni ADC è presente una singola alimentazione e un pin di massa (GROUND). 4 ADC – PARAMETRI FONDAMENTALI RISOLUZIONE La risoluzione è la minima variazione di tensione che il convertitore è in grado di convertire, coincide con il quanto Q. Q = VFSR / 2n La risoluzione di un convertitore è tanto migliore quanto maggiore è il suo numero di bit. 5 ADC – PARAMETRI FONDAMENTALI TEMPO DI CONVERSIONE Il tempo di conversione è una misura di quanto tempo impiega il convertitore ad effettuare una singola conversione. Si va da convertitori "lenti", con tempo di conversione intorno a qualche millesimo di secondo, a convertitori ultra veloci che arrivano ad alcuni nanosecondi di tempo di conversione. Il tempo di conversione limita la massima frequenza di campionamento. Tcampionamento > Tconversione 6 ADC – PARAMETRI FONDAMENTALI TEMPO DI CONVERSIONE la conversione avviene senza errore apprezzabile se: fmax ≤ 1/(π * 2n * Tconversione) fmax - massima frequenza del segnale da convertire n - risoluzione (numero di bit) del convertitore Tconversione - tempo di conversione del convertitore fmax si riduce: all'aumentare di Tconversione; all'aumentare del numero di bit n del convertitore. 7 SAMPLE & HOLD Quando la diseguaglianza fmax ≤ 1/(π * 2n * Tconversione) non è verificata, si utilizza un circuito, posto a monte del convertitore ADC, con lo scopo di mantenere costante la tensione da convertire per tutta la durata della conversione stessa. Il S&H "congela" la tensione da convertire per tutta la durata del periodo di campionamento, in modo tale che l'ADC abbia il tempo di effettuare una conversione corretta. 8 SAMPLE & HOLD 9 DAC – SCHEMA GENERALE 10 DAC – SCHEMA GENERALE digital inputs sono gli ingressi digitali, in numero pari al numero di bit del convertitore; Vref+ e Vref- servono per impostare la tensione superiore e la tensione inferiore di fondo scala; Vcc e -Vcc sono rispettivamente la doppia alimentazione, positiva e negativa. In alcuni ADC è presente una singola alimentazione e un pin di massa (GROUND). Vout è la tensione analogica in uscita; a seconda dei convertitori l'uscita prodotta potrebbe essere una corrente (Iout). 11 DAC – SCHEMA GENERALE LE (Latch Enable) è un segnale logico presente in alcuni DAC e che serve per congelare (latchare) i segnali digitali di ingresso: in pratica quando LE è attivo, il DAC legge il valore digitale in ingresso; disattivando LE, l'ultimo codice digitale rimane memorizzato nel DAC. A differenza degli ADC, in un DAC non ci sono segnali di temporizzazione: le conversioni sono attivate dal cambiamento dei valori binari in ingresso. 12 DAC CON USCITA IN CORRENTE 13 DAC – PARAMETRI PRINCIPALI resolution (risoluzione) - numero di bit del convertitore settling time (tempo di assestamento) - tempo impiegato dal DAC per effettuare una conversione. I valori tipici vanno da alcuni nanosecondi fino ad alcuni microsecondi. full scale range (intervallo di fondo scala) - massimo intervallo di valori per la grandezza analogica in uscita al DAC Codifica - tipo di codice usato per rappresentare il dato in ingresso. 14 DAC – GLITCH Quando vi è una variazione del dato binario in ingresso al DAC, si dovrebbe avere il cambiamento simultaneo di uno o più bit. Poiché i bit di ingresso non potranno mai commutare tutti contemporaneamente, durante la transizione si generano delle combinazioni binarie non desiderate (spurie) che il DAC traduce in impulsi di tensione (glitch) di breve durata. Tali impulsi producono andamenti non desiderati nella tensione di uscita al DAC. 15 DAC – GLITCH Il problema dei glitch può essere risolto collegando in uscita al DAC un blocco di Sample & Hold il quale "congela" la tensione analogica fra una commutazione e l'altra dei codici di ingresso: in pratica la tensione di uscita viene acquisita dal S&H solo dopo che gli eventuali glitch si sono esauriti. 16

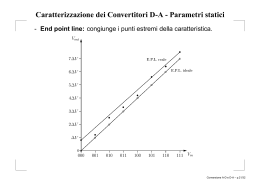

Scaricare