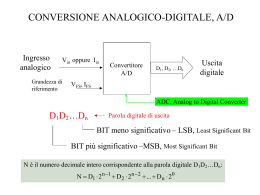

Cosa è un DAC? Digital-to-Analog converter dispositivo “mixed signal”: o Input digitale (parola a n bit) o Output analogico: tensione o corrente Vcc D[n-1] D[n-2] Vref output analogico (Vout) .. Convertitore D/A D[0] gnd Vcc D[n-1] D[n-2] Vref output analogico (Vout) Convertitore D/A .. D[0] gnd La tensione di output è Vout D[n 1..0] Vref n 2 Cosa fa esattamente un DAC? Per un DAC a 3 bit ci sono 8 possibili codici di input Vcc Vref (8V) D[2..0] D[2] D[1] D[0] output analogico (Vout) Convertitore D/A gnd 000 001 010 011 100 101 110 111 Vout 0V 1V 2V 3V 4V 5V 6V 7V Il DAC sulla scheda di laboratorio 4 DAC in un singolo chip: REFA, REFB, REFC, REFD Tensioni di riferimento fissate a 2.5 V GND REFA REFB REFC REFD DATA DCLK 1 2 3 4 5 6 7 14 13 12 11 10 9 8 VDD LDAC DACA DACB DACC DACD LOAD DACA, DACB, DACC, DACD Tensioni di output configurazione GND REFA REFB REFC REFD DATA DCLK 1 2 3 4 5 6 7 14 13 12 11 10 9 8 DATA, LDAC, LOAD, DCLK Segnali di Input per programmare il DAC VDD LDAC DACA DACB DACC DACD LOAD Sono controllati dalla FPGA FPGA Protocollo di configurazione (circuito da implementare nella FPGA) Il codice digitale a 8 bit viene trasmesso dalla FPGA al DAC in modo seriale tramite la linea DATA assieme a un treno di impulsi di sincronizzazione lungo la linea DCLK 11 impulsi DCLK DATA A1 A0 Identificatore del DAC: A1A0 = 00 DAC0 A1A0 = 01 DAC1 A1A0 = 10 DAC2 A1A0 = 11 DAC3 RNG D7 D6 D5 D4 D3 D2 D1 D0 Codice digitale (è trasmesso prima il MSB) La tensione di output è Vout D[7..0] Vref 1 RNG n 2 Il codice digitale a 8 bit viene trasmesso dalla FPGA al DAC in modo seriale tramite la linea DATA assieme a un treno di impulsi di sincronizzazione lungo la linea DCLK DCLK DATA LDAC A1 A0 RNG D7 D6 D5 D4 D3 D2 D1 D0 Sempre basso LOAD Le linee LDAC e LOAD sono usate dal DAC per caricare i bit ricevuti lungo la linea DATA in un registro interno e per aggiornare la tensione di output La tensione di output viene aggiornata con questo impulso DAC_interface clk res SW0 D[7..0] A[1..0] DAC_interface DCLK DATA LDAC LOAD Una macchina a stati parte quanto SW0 viene premuto (segnale di inizio configurazione) oGenera un treno di 11 impulsi DCLK oSuccessivamente genera un impulso LOAD La linea LDAC è tenuta sempre bassa La parola in ingresso D[7..0] deve essere serializzata: su ogni fronte di salita di DCLK viene messo un nuovo bit (il primo trasmesso è il MSB) False partenze: 1. non va bene generare un segnale largo 11 cicli di clock e usarlo in AND col segnale di clock della FPGA Questo si chiama “gating” del clock e in generale è meglio evitarlo Diagramma degli stati corretto ed “elegante” che genera un treno di impulsi attraverso un loop o ciclo Il numero di cicli è controllato da un contatore che genera un segnale Cout quando ha raggiunto il giusto numero di conteggi (cicli) Se l’enable del contatore (CNT_EN) è asserito nello stato S0, a quale valore del conteggio il contatore deve generare Cout? Cambiamo i nomi degli input: DAC[7..0] corrisponde a D[7..0] DAC[8] corrisponde a RNG DAC[10..9] corrisponde a A[1..0] Esternamente (nel foglio dove posizioniamo il simbolo DAC_INTERFACE) possiamo fare questi collegamenti Abbiamo ancora il problema che DAC[10..0] deve essere serializzata Su ogni fronte di salita di DCLK deve essere messo un bit lungo la linea DATA Convertitore parallelo/seriale DCLK DATA A1 A0 RNG D7 D6 D5 D4 D3 D2 D1 D0 DAC[10] DAC[9] DAC[8] DAC[7] DAC[6] DAC[5] DAC[4] DAC[3] DAC[2] DAC[1] DAC[0] Stesso contatore usato dalla Macchina a stati I bit cambiano sul fronte di discesa di DCLK anzichè su quello si salita II soluzione: Il clock del contatore che incrementa SEL è DCLK Qui i bit cambiano su ogni fronte di salita di DCLK Il problema è che sul primo fronte SEL diventa 1 e appare quindi DAC[9] mentre DAC[9] dovrebbe apparire sul secondo III soluzione: Cerchiamo di usare uno shift register e facciamo scorrere i bit con DCLK Questo potrebbe funzionare se i bit DAC[10..0] sono preventivamente caricati nei Flip-Flop prima che arrivi il treno di impulsi DCLK Quanti FF ci vogliono? Problema: come faccio a caricare i FF con i bit? Devo mettere davanti a ogni FF dello shift register un blocco di logica combinatoria con un input LOAD_SHREG che serve a caricare il FF LOAD_SHREG potrebbe essere generato modificando la macchina a stati. Come? Per caricare il FF è necessario anche un impulso sull’input di clock del FF? Come posso fare? Caricamento dei FF tramite l’input PRES dei FF Un inconveniente è che PRES (come RES) è un input asincrono attivo indipendentemente dal segnale di clock Vediamo che problemi si potrebbero verificare con input asincroni (N.B. questo è illustrato per i segnali CNT_RES e LOAD, non per il caricamento dei FF) Assegnamo a ciascuno dei 4 stati il codice indicato nelle bolle La macchina a stati parte con START_DAC. Nel diagramma temporale sono indicati i due bit dello stato Nella transizione da STATE[1..0]=01 (S0) a STATE[1..0]=10 (S1) entrambi i bit cambiano, ma non simultaneamente Per un breve transiente lo stato è STATE[1..0]=11 (S2) e CNT_RES e LOAD vengono asseriti (creando problemi) Possibile soluzione: facciamo passare CNT_RES e LOAD attraverso un FF. Poichè il FF campiona il suo input solo sul fronte di salita del clock, il glitch non viene campionato (è filtrato) Ma N.B. L’impulso generato dopo è ritardato così di un ciclo di clock Altra soluzione: usiamo un codice per gli stati in modo tale che da una transizione all’altra cambi solo un bit per volta In questo modo non è possibile generare glitch Codice Gray a 2 bit 00 0111 10 In ogni caso potrebbe essere sempre preferibile cercare dei codici in cui cambi un solo bit per volta il più possibile Tornando al caricamento dei FF è preferibile un caricamento sincrono Serve un MUX in cui la linea di selezione è LOAD_SHREG Cosa è un ADC? Analog-to-Digital Converter dispositivo “mixed signal”: o Input analogico (tensione o corrente) o Output digitale: parola a n bit Vcc Input analogico (Vin) Vref Convertitore A/D .. Out[n-1] Out[n-2] Out[0] gnd Vcc Input analogico (Vin) Vref Convertitore A/D .. Out[n-1] Out[n-2] Out[0] gnd Può essere considerato un partitore o L’output ci dice: che frazione di Vref è l’input Vin? o Output: Out [n 1..0] 2n Vin Vref Cosa fa esattamente un ADC? Per un ADC a 3 bit ci sono 8 possibili codici di output Vcc Input analogico (Vin) Vref(8V) Out[2] Convertitore A/D gnd Esempio: se Vin=5.5 V e Vref=8 V Out[2..0] = 101 Out[1] Out[0] Vin Out[2..0] 0-1 1-2 2-3 3-4 4-5 5-6 6-7 7-8 000 001 010 011 100 101 110 111 Risoluzione L’ADC risolve due tensioni diverse se differiscono per più di 1 V producendo due codici diversi La risoluzione dell’ADC è 1 V (Vref/23) Vcc Input analogico (Vin) Vref(8V) Out[2] Convertitore A/D gnd Il bit meno significatico (LSB) rappresenta 1 V Out[1] Out[0] Vin Out[2..0] 0-1 1-2 2-3 3-4 4-5 5-6 6-7 7-8 000 001 010 011 100 101 110 111 Risoluzione e range dinamico La risoluzione di un ADC dipende dal numero di bit e da Vref: Vref 2n Fissata Vref, maggiore è il numero di bit, migliore è la risoluzione. Se n=8 (anzichè n=3) la risoluzione sarebbe 8/28~31 mV formulazione alternativa: (fissata Vref) la risoluzione di un ADC è il numero di bit. La tensione Vref determina il range dinamico dell’ADC A parità di bit, minore è la tensione Vref, più fine è la suddivisione dell’intervallo Vref(=Vin max)-0 per cui la risoluzione migliora. Ad esempio, se Vref=0.8 (anzichè 8 V) la risoluzione sarebbe 100 mV. Il miglioramento va però a scapito del range dinamico. ADC tracking Descrizione a grandi linee: il codice a 8 bit di un contatore viene convertito da un DAC in una tensione analogica che viene quindi confrontata con la tensione di input. Il contatore viene incrementato fino a quando la tensione del DAC raggiunge quella in input. A questo punto il conteggio raggiunto dal contatore è il codice richiesto. ADC tracking: implementazione FPGA DAC interface DCLK DATA Vanno ai DAC LDAC LOAD DAC Vanalog count[7..0] CNT_EN Contatore a 8 bit comparatore Vanalog comp CNT_EN Start_conv Vin sm_ADC comp Tensione in ingresso da convertire Il comparatore (analogico) confronta due tensioni e produce in output un segnale logico: Se Vin > Vanalog comp = 0 Se Vin < Vanalog comp = 1 Collegamento comparatoreADC Soluzione alternativa: aspetta che l’interfaccia del DAC asserisca il segnale LOAD che va al DAC si ripete il ciclo ADC[7..0] è collegato a due cifre del display Per un’eventuale nuova conversione Le macchine a stati vanno disegnate usando verilog Altri dettagli Si deve impiegare il terzo DAC (CMREF) corrispondente ad A[1..0]=10 Vref dei DAC fissa Vref dell’ADC. Nella scheda Vref = 2.5 V Il comparatore è un amplificatore operazionale (più dettagli in seguito) Vin (COM_IN) può provenire da un generatore di tensione tramite un connettore LEMO Limitazioni dell’ADC tracking La limitazione principale è che è lento: Poichè il contatore parte sempre da zero, Il tempo di conversione è variabile Maggiore è Vin maggiore è il tempo di conversione: se Vin = Vref è necessario ripetere il ciclo di incremento del contatore 256 volte! ADC ad approssimazioni successive START_CONV: inizio conversione. Nel SAR viene caricata la parola 10000000 (solo il MSB = 1) Se Vin >VD il controllore mantiene MSB a 1 e carica un altro 1 nel bit immediatamente successivo. Se, invece Vin < VD il controllore pone MSB a 0 e carica un 1 nel bit immediatamente successivo. La nuova parola viene caricata nel SAR e l'uscita del DAC viene aggiornata. L’algoritmo descritto per il bit MSB viene ripetuto in modo identico per tutti gli altri bit. Visualizzazione della conversione sul display Visualizzazione della tensione in decimale Può essere implementata con una ROM: Input a 8 bit (256 righe di memoria) Output a 12 bit La variabile temporale In generale i segnali del mondo reale hanno una qualche dipendenza dal tempo Nel processo di conversione A/D ci interessa ricostruire questa dipendenza dal tempo Campionamento del segnale Input analogico Output digitale Sample and Hold L’input analogico non va direttamente all’ADC. Entra prima in un circuito che campiona il segnale a un certo istante e quindi lo tiene congelato per tutto il tempo richiesto dalla conversione ADC L’ADC trasforma il segnale analogico quantizzato nel tempo in un codice digitale (segnale quantizzato) Il campionamento trasforma il tempo da continuo a discreto Nei sistemi più semplici l’input analogico è collegato direttamente all’ADC Input analogico Output digitale ADC Questo va bene se il segnale varia nel tempo molto più lentamente del tempo richiesto dall’ADC per effettuare la conversione In ogni caso, è il tempo di conversione che quantizza il tempo Errore di quantizzazione della tensione Al crescere della tensione di input cresce anche l’errore fino a quando cambia il codice Aggiungiamo un offset pari a 1/2LSB all’input Abbiamo un errore pari a ±1/2LSB Errore di quantizzazione in un segnale variabile Segnale dopo il S/H Output digitale _ Errore di quantizzatione L’errore di quantizzazione appare come un rumore casuale. La quantizzazione aumenta l’errore casuale del segnale Caratteristiche di questo rumore: oDistribuito uniformemente nell’intervallo ±1/2LSB oDeviazione standard 1/sqrt(12)LSB=0.29LSB Esempio: Segnale analogico di ampiezza massima 1 V con rumore casuale di 1.0 mV Conversione A/D a 8 bit 1mV = 0.255 LSB Rumore di quantizzazione = 0.29 LSB Rumore totale dell’output digitale 0.2552 0.292 0.386LSB Aumento del 50% del rumore già presente nel segnale L’errore di quantizzazione diminuisce aumentando il numero di bit La conversione di un segnale anaogico con un ADC a o8 bit aggiunge un errore rms 0.29/256 ~ 1/900 del valore di fondo scala o12 bit aggiunge un errore rms 0.29/4096 ~ 1/14000 del valore di fondo scala o16 bit aggiunge un errore rms 0.29/65536 ~ 1/227000 del valore di fondo scala Il numero di bit determina la precisione dei dati. La decisione sul numero di bit necessari dipende da: oQuanto rumore è già presente nei dati oQuanto rumore può essere tollerato nel segnale digitale

Scaricare