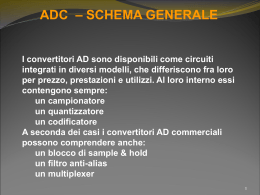

SAMPLE & HOLD In elettronica ,l’esigenza di effettuare operazioni di conversione dovrebbero essere gia noti attraverso circuiti radrizzatori che permettono la realizzazione di convertitori AC/DC, convertitori A/D e D/A,convertitori V/f e f/V. IL TEOREMA DI SHANNON dice: Un segnale limitato in banda è ricostruibile univocamente dai suoi campioni purché essi siano presi con una frequenza almeno doppia di quella massima presente nel segnale: f c 2 f MAX Dove f MAX rappresenta la frequenza massima dello spettro del segnale. Se il teorema non è verificato,il segnale non è univocamente ricostruibile dai suoi campioni. Il teorema dice con quale frequenza campionare un segnale per non perdere informazioni sul suo andamento,esiste tuttavia il problema relativo alla conversione in digitale dei singoli campioni:se la grandezza varia durante il tempo di conversione,qual è il valore su cui l’ADC si deve agganciare? Il limite massimo in frequenza del segnale affinché l’errore dell’ADC non sia maggiore di 1LSB. Per risolvere questo problema si utilizza la tecnica del S & H che consiste sostanzialmente nel”CONGELARE” attraverso un condensatore il valore istantaneo della tensione di ingresso per un tempo sufficiente alla conversione. Si tratta di un sistema di campionamento reale,realizzabile con dispositivi elettronici convenzionali. Il segnale x(t) viene campionato(SAMPLE) ad ogni Tc e il suo valore viene mantenuto costante(HOLD) per un intervallo di tempo Л<=Tc. Schema del SAMPLE & HOLD L'UTILIZZO DEL SAMPLE-HOLD • In un generico schema di acquisizione dati, spesso è presente il modulo sample-hold. Esso è un dispositivo avente in ingresso una tensione V e in uscita una tensione V Il suo funzionamento è comandato da un segnale, S/H, che può identificare le due modalità di funzionamento del dispositivo: • Fase di sample (o campionamento); in questa fase il segnale V è uguale al segnale V ; • Fase di hold (o mantenimento); in questa fase il segnale V è sempre costante ed è uguale al segnale V nell’istante in cui il segnale S/H commuta da S (sample) ad H (hold); i u u i u i Nella figura sottostante è raffigurato il diagramma di tempificazione di un modulo sample-hold. Il suo utilizzo è spesso fondamentale in un sistema di acquisizione dati: infatti un segnale analogico (come quello fornito da un trasduttore che analizza una variabile continua) deve essere discretizzato in modo da poter essere "processato" dal sistema di controllo, che è un sistema prettamente discreto. La fase di conversione avviene tramite l’uso di un dispositivo, il convertitore Analogico-Digitale (ADC) che è in grado di trasformare un segnale analogico in un segnale digitale a n bit (valori industriali tipici sono 8 o 10 ). Il procedimento di conversione è però un procedimento piuttosto lento (dell’ordine delle decine di microsecondi, anche se esistono convertitori ADC che convertono un segnale in alcune decine di nanosecondi ) ed è pertanto necessario che per tutto il tempo di conversione il valore in ingresso resti all’incirca costante. Per l’esattezza, il segnale Vi deve variare al di sotto della metà del valore più piccolo discriminabile dal convertitore (che è anche l’errore massimo che questi può commettere): al di là di questa soglia il convertitore "scarterebbe" inesorabilmente fornendo un valore che non coincide con quello effettivamente presente nell’istante in cui inizia la conversione, poiché sono successivamente intervenute variazioni nel segnale in ingresso che lo hanno portato ad avere un valore differente.Per evitare questo si utilizza il dispositivo sample-hold, che ha il compito di mantenere, per tutta la durata della conversione, il valore del segnale in ingresso al convertitore costante. Occorre però porsi una domanda: è sempre necessario utilizzare il sample-hold? Per esempio, nel caso in cui i segnali in ingresso abbiano una lenta variazione nel tempo (è il caso, per esempio, di segnali provenienti da un trasduttore di temperatura) è possibile che questa variazione in un tempo Tc (tempo di conversione) resti sempre al di sotto dell’errore massimo del convertitore. Per determinare il limite massimo che la variazione del segnale in ingresso può presentare affinché si riesca comunque ad ottenere un valore digitale corretto a meno dell’errore, uguale, come già detto, alla metà del valore minimo discriminabile ( il che coincide anche con il bit meno significativo o LSB, least significant bit, del codice in uscita dall’ADC) occorre impostare una equazione che tenga conto della velocità della variazione, dell’errore e del tempo di conversione. La velocità di variazione è espressa, matematicamente, attraverso la derivata di Vi rispetto al tempo, ossia : .

Scaricare