Flash scaling and charge trap memories Daniele Ielmini DEI - Politecnico di Milano, Milano, Italy [email protected] ITRS 2009 • Main challenges: high-k/metal WL/CT at node 25 nm, 4 bits per cell Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 2 1 Outline • Flash reliability • Cycling endurance • Data retention • Intrinsic data loss • SILC • Detrapping and RTN • Flash scaling • Active area scaling • Pitch scaling • Charge-trap memory • SONOS/MANOS • NROM • Conclusions Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 3 Flash reliability • Non volatile 1. 105 P/E cycles endurance 2. 10 years data retention NOR Endurance Over-erase X NAND Mechanism X Oxide and interface traps, charge trapping X Over-program X Data retention X X Read disturb X X Feb. 23, 2010 T=-40÷85°C Charge trapping, trap assisted tunneling, extrinsic defects Charge trapping/detrapping, direct tunneling, trap assisted tunneling, RTN D. Ielmini, "Non volatile memories" – 2 4 2 NOR endurance 8 Vt P/E [V] 7 PROGRAM 6 5 4 3 ERASE 2 1 1.E+00 1.E+01 1.E+02 1.E+03 1.E+04 1.E+05 Number of cycles P/E at constant voltage/time (no PV/EV loops) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 5 NAND endurance 1. Both P/E VT increase due to subthreshold slope and gain degradation 2. Stronger degradation for erased cells Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 6 3 Bulk trap generation 1. Bulk trap generation decreased FN/CHE injection decrease of programmed VT, increase of erased VT Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 7 Charge trapping 2. Bulk trap generation trapped negative charge itself contributes to VT increase of VT Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 8 4 Data retention VG = 0V a) VS = 0V VD = 0V • Data retention from programmed state (10 years) VD = 0V • Gate disturb (program, read) on erased state VG = 4V b) VS = 0V 1. NOR typical application: 106 read (109 disturbs) in 2 years total gate disturb time of 200s in 10Y! 2. NAND non official spec. = 105 read operation, about 16s (=10µs*16WL*105) Feb. 23, 2010 9 D. Ielmini, "Non volatile memories" – 2 Intrinsic data-loss prediction 14 tox 10 VTP=VT0+2V 12 Gate FG Substrate Retention time [s] 10 30Kyears VTfail=VT0+1V 10 10 97years 10years 8 10 120days 6 10 9.5hours 4 10 2 10 0 10 3 3.5 4 4.3 4.5 5 tox [nm] 1. Failure estimate depends on programmed VT, neutral VT0 2. Intrinsic tunneling is not a concern for data retention down to tunnel-oxide thickness tox=4.3nm Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 10 5 Barrier engineering • Barrier engineering can improve the trade-off between scaling VDD and maintaining data retention • crested barrier (B) behaves as • thick dielectric at small voltage (retention) • thin dielectric at large voltage (programming) • SiO2 • SiN/AlN/SiN Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 11 Single-electron (SE) effects N=21 N=346 G. Molas et al., IEEE T-ED 53, 2006 Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 12 6 SE effects vs. scaling • Spread of retention time increases for decreasing N increasing concern along the scaling roadmap G. Molas et al., IEEE T-ED 53, 2006 • Same problem occur during program/erase • Impact on nitride/nanocrystal is even larger (smaller N) • Solutions: finFET structure, error correction code (ECC), etc. Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 13 Outline • Flash reliability • Cycling endurance • Data retention • Intrinsic data loss • SILC • Detrapping and RTN • Flash scaling • Active area scaling • Pitch scaling • Charge-trap memory • SONOS/MANOS • NROM • Conclusions Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 14 7 Theory vs. roadmap •Intrinsic tunneling is NOT the real concern •Stress-induced leakage current (SILC) after P/E cycling leads to anomalous data retention Feb. 23, 2010 15 D. Ielmini, "Non volatile memories" – 2 -2 Current Density [A cm ] SILC characteristic -6 10 -7 10 -8 10 1V -9 10 -10 2TAT 10 -11 10 TAT -12 10 1 2 3 4 5 6 Floating Gate Voltage [V] D. Ielmini et al., IRPS 2001 • Trap-assisted tunneling (TAT = Shockley Hall Read + tunneling) • Generalized to account for trap cooperation (2TAT, 3TAT, etc.) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 3.5 V 16 8 Outline • Flash reliability • Cycling endurance • Data retention • Intrinsic data loss • SILC • Detrapping and RTN • Flash scaling • Active area scaling • Pitch scaling • Charge-trap memory • SONOS/MANOS • NROM • Conclusions Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 17 Measured ∆VT N. Mielke et al., IEEE T-DMR 4, 2004 Intel-0.13µm (channel erase) Intel-0.18µm (source erase) 1. Stronger impact on NAND cells (FN P/E) and multilevel 2. Very large spread and positive/negative ∆VT, which cannot be explained by Poisson statistics alone 3. Positive/negative ∆VT ? Additional RTN contribution Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 18 9 Detrapping and Dit annealing (3) (2) (1) (5) (4) (1)Interface trap annealing (2)e- emission toward substrate (4) h+ capture from substrate (3)e- capture from FG (5) h+ emission toward FG Feb. 23, 2010 19 D. Ielmini, "Non volatile memories" – 2 VT shift calculation (1) Interface trap annealing (spiega ∆VT sul neutro) ∆VT = − (2) (4) x q Cx 1 1 x = + Cx C2 ε ox (3) (2) (1) (5) (4) (3) (5) Feb. 23, 2010 ∆VT = − q q qx + =+ C2 C x ε ox D. Ielmini, "Non volatile memories" – 2 20 10 T acceleration of VT shift EA=1.1eV EA=1.2eV N. Mielke et al., IEEE T-DMR 4, 2004 Feb. 23, 2010 21 D. Ielmini, "Non volatile memories" – 2 Random telegraph signal capture τC emission τE Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 22 11 Impact on MLC programming H. Kurata et al., Symp. VLSI Circ. Dig., 2006 • VT distribution spread control by ISPP step ∆VGP is no more effective due to RTN ∆VT • Extrapolations indicate ∆VT > 100 mV at 45 nm Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 23 ‘Complex’ and ‘giant’ RTN N. Tega et al., IEDM Tech. Dig., 2006 P. Fantini et al., IEEE EDL 28, 2007 • Multitrap (‘complex’) RTN similar to multitrap SILC, it may critically affect VT distribution in the array • ‘Giant’ RTN how can one trap provide such a large VT? Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 24 12 Random dopant fluctuations A. Asenov et al., IEEE T-ED 50, 2003 A. Ghetti, et al., IEDM Tech. Dig. 2008 Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 25 Reliability – Conclusions • Reliability issues: • ∆VT after cycling due to charge trapping: worsen with scaling (spread) • ∆VT after programming due to charge detrapping: worsen with scaling (spread) • ∆VT due to RTN: worsen with scaling (larger variability of trap position and number) • SILC worsen with scaling (oxide thickness) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 26 13 • Flash reliability • Cycling endurance • Data retention • Intrinsic data loss • SILC • Detrapping and RTN • Flash scaling • Active area scaling • Pitch scaling • Charge-trap memory • SONOS/MANOS • NROM • Conclusions Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 27 NOR scaling (Intel) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 28 14 Physical scaling issues NOR NAND • Active area scaling active device elements: WG and LG y-pitch L L y-pitch W W x-pitch x-pitch • Pitch scaling Passive elements: isolation (NAND, NOR), drain contact (only NOR) Feb. 23, 2010 29 D. Ielmini, "Non volatile memories" – 2 NOR structure and scalability L gate Tecnologia 250nm 180nm 150nm 130nm 90nm 65nm 0.81µm² 0.46µm² 0.32µm² 0.16µm² 0.076µm² 0.046µm² Area/F2 13 14.1 14.2 9.5 9.4 10.9 L gate 375nm 300nm 295nm 235nm 175nm 125nm Area 1. 2. 3. Need for BL contact WL/BL isolation for reliability purpose Inherently hard scalable LG Ever growing aspect ratio, difficult scaling Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 30 15 NOR cell Along W Feb. 23, 2010 Along L D. Ielmini, "Non volatile memories" – 2 31 NOR physical scaling 2F 5F G. Atwood, IEEE T-DMR 2004 Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 32 16 Leff scaling Source FG Li Drain • Potential barrier of 3.1eV (hence CHE VD) does not scale! • LG must sustain the high VD=4.5V during CHE programming can hardly be scaled below 70nm, due to short channel effect (SCE: punch-through, DIBL) Feb. 23, 2010 33 D. Ielmini, "Non volatile memories" – 2 Punch through and DIBL SiO2 CB S D • D Punch through effects enhanced for short channel (depletion region of S and D overlap to decrease φS) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 34 17 Solutions to LG limitations • FinFET: • better control of SCE and maximum read current, thus enhancing operation speed and sensing margin • FinFET + FG is hard, CT implementation most practical reliability issues • 3D cell structures: LG aligned to the vertical axis, again FG is hard • t1 scaling down improves SCE, but conflicts with reliability (data retention) G. Atwood, IEEE T-DMR 2004 Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 35 WG scaling WG Weff • WG – Weff = isolation beak + ONO sidewalls for improved αG • Weff scaling lowers sensing current (Leff not scaling), but main limitation is lithography • VT instability becomes worse as single traps can switch on and off ID (percolation effects) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 36 18 Common NOR/NAND issues • • • • NAND has FG space, isolation issues, too NAND has no drain contact no Cont-gate issues NAND has no source resistance issues, no LG issues NAND has higher density smaller pitch, physical limit approaching Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 37 NAND LG scaling – 1 • ION/IOFF>10 is sufficient to distinguish between “0” and “1” easily scalable LG • No punchthrough issues (FN programming, low VD) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 38 19 • Flash reliability • Cycling endurance • Data retention • Intrinsic data loss • SILC • Detrapping and RTN • Flash scaling • Active area scaling • Pitch scaling • Charge-trap memory • SONOS/MANOS • NROM • Conclusions Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 39 Pitch scaling 1. Cell-cell capacitive interference (NOR, NAND) 2. Dielectric breakdown at the WL-BL spacer (NOR) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 40 20 Solution #1: reducing tFG • Capacitive coupling can be decreased reducing tFG dij tFG LG CG CG FG FG Sub Sub VT ,i = VT 0,i − Qi Cij Q ε t t − V j = VT 0,i − i − diel FG 2 V j C2 C2 C2 ε 2 LG d ij Feb. 23, 2010 41 D. Ielmini, "Non volatile memories" – 2 Drawback: reduced αG • Unfortunately, this also reduces C2 and αG=C2/CTOT inhibits VDD scaling ( VFG = αGVG + Qi ) CTOT Feb. 23, 2010 CG CG FG FG Sub Sub CG CG FG FG Sub Sub D. Ielmini, "Non volatile memories" – 2 42 21 NAND scaling limitation ∆VT<0.2V • Samsung predicts difficulties in NAND scaling beyond 30 nm (K. Kim, IEDM 2005) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 43 Improving αG αG = C2 C2 ε 2 A2 / t 2 = = CTOT C1 + C2 ε1A1 / t1 + ε 2 A2 / t 2 Coupling ratio can be improved by: • Reducing t2 (limited by retention) • Increasing ε2 high-k IPD (HfO2, Al2O3, etc.) • Increasing A2 U-shaped FG (not viable for ultrascaled WG, Kim, IEDM2005) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 44 22 Solution #2: low-k/air spacers • Air (ε=1) spacer proposed by Samsung • Air gap also provides immunity against trap-up between WLs for NAND Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 45 Solution #3: recessed FG • Recessed field oxide: • CG effectively shields adjacent FGs • Improved αG Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 46 23 Limitations to recess • Along the WL, space will eventually become comparable to 2t2 + minimum poly-CG thickness reduced αG Planar structures with high-k IPD and/or CT are likely solutions Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 47 Solution #4: algorithms Change the programming algorithm by taking into account the status of neighboring cells (or bits, see Eitan et al., IEDM 2005) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 48 24 Solution #5: discrete storage • Replacing a continuous FG with Si nanocrystals or atomic-size traps charge-trap (CT) memory • Advantages: • suppress capacitive coupling between neighboring cells • Geometrical improvement of αG not possible anymore high-k IPD CG CG Sub FG Sub CG SiN Sub Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 49 CT vs. FG Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 50 25 Scaling – Conclusions • Many technical challenges for continuing FG memories • NOR are most affected by LG and t1 scaling issues • Aggressively scaled NAND cells will have increasing cellcell interference, small capacitive coupling and small number of stored electrons • Most aggressive extrapolations see FG scaling down to 15 nm node • Further scaling: • Barrier engineering (high-k, metal gate) • Planar CT memories • 3D CT memories Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 51 • Flash reliability • Cycling endurance • Data retention • Intrinsic data loss • SILC • Detrapping and RTN • Flash scaling • Active area scaling • Pitch scaling • Charge-trap memory • SONOS/MANOS • NROM • Conclusions Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 52 26 Charge-trap memories • SONOS memory (t1 < 3 nm) • Program: FN tunneling of electrons • Erase: DT of holes • NAND replacement • NROM (t1 > 5 nm) • Program: channel hot electron (CHE) injection • Erase: hot-hole injection (HHI) • NOR replacement Feb. 23, 2010 CG SiN Sub CG SiN 1 2 Sub D. Ielmini, "Non volatile memories" – 2 53 Nitride vs. Flash cells • Easy to fabricate • Single poly process • CMOS compatible • No FG for charge storage • Free of drain turn on • Free of FG interference • No need for wrapped geometry with high coupling ratio • No erratic/fast erase bits • Immunity to SILC t1 smaller than in Flash lower P/E voltages, faster P/E • 2 b-c available (NROM) • Compatible with 3D architectures Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 54 27 Disadvantages • SONOS: • 2 b-c only with multilevel reduced margins • Erase saturation (need for barrier engineering, high-k blocking oxide, metal or P+ poly gate, …) • Poor reliability (thin oxide, leaky CT layer) • NROM: • Second-bit effect • Erase issues (hard-to-erase, overerase) • Program state VT shift (vertical charge loss, lateral redistribution, Dit annealing) Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 55 VT [V] Erase saturation High VT state Low VT state Time [s] •NAND application negative VT in erase state needed •Positive erased VT : final steady-state is for equal injection/emission E-fields zero stored charge •Need to differentiate injection/emission barriers Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 56 28 Improvement: thin bottom SiO2 B. De Salvo et al.,IEEE T-DMR 4, 2004 1. t1 reduction (< 3 nm) enhances hole injection (high tunneling barrier of 4.5 eV) to improve erase characteristics 2. Poor data retention! Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 57 TaN gate + Al2O3 C. H. Lee et al., IEDM Tech. Dig. 2003 Feb. 23, 2010 O/N/Al2O3=2.5/12/10nm D. Ielmini, "Non volatile memories" – 2 58 29 Lateral redistribution in SONOS C. Kang, et al., IRPS 2007 Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 59 WL and BL patterning 1. WL + BL SiN patterning shows best reliability 2. Silicon-rich nitride (SRN) with presumably large carrier mobility was used in the cell J. S. Sim et al., NVSMW 2007 Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 60 30 Band-engineered (BE) SONOS H. T. Lue et al., IEDM Tech. Dig. 2005 Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 61 BE-SONOS vs. SONOS S. Y. Wang et al., IRPS 2007 BE-SONOS erase characteristics are comparable to SONOS with t1 = 2 nm, but reliability is much better Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 62 31 Scaling perspective tN = 7 nm 3.5 nm 2 nm H. T. Lue et al., IRPS 2007 S.-H. Gu, et al., IEEE T-ED 54, 2007 Trapping decreases as tN is reduced, retention time strongly impacted by t1 downscaling Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 63 Percolation effects Drain Bottleneck Source D. Ielmini, et al., Proc. IRPS 2004 Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 64 32 MANOS roadmap Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 65 • Flash reliability • Cycling endurance • Data retention • Intrinsic data loss • SILC • Detrapping and RTN • Flash scaling • Active area scaling • Pitch scaling • Charge-trap memory • SONOS/MANOS • NROM • Conclusions Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 66 33 NROM: P/E operations Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 67 NROM: read operation • VD = 0.1 V ohmic channel, read current depends on both bits • VD = 1.6 V saturated channel, only bit2 is read • Reverse read only bit1 is read Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 68 34 Data retention A. Shappir, et al., IEEE T-DMR 4, 2004 time Data loss appears as a rigid shift of the VT distribution, without tails apparently no SILC effects Feb. 23, 2010 69 D. Ielmini, "Non volatile memories" – 2 Cycling and T dependence of VT VT [V] M. Janai, et al., IEEE T-DMR 4, 2004 10 cycles T VT [V] 30K cycles Feb. 23, 2010 VT features saturation above neutral level D. Ielmini, "Non volatile memories" – 2 70 35 Charge-loss mechanisms Mechanism 1 : lateral redistribution (LR) of trapped carriers Mechanism 2 : vertical loss of trapped carriers Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 71 Limiting lateral redistribution • Avoid mismatch between electron and hole injection (doping profile, program/erase pulse) • Improve energy depth of traps in the nitride layer by trap engineering • Sub-monolayer Ti results in atomic-size traps with good P/E window, 2-bit operation and suppressed LR H. Sunamura et al., IEDM Tech. Dig., 2006. Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 72 36 Refill method Sort of ‘electrical shaking’ to stabilize the electron distribution after programming 1. CHE programming (with verify) 2. -FN soft erase to re-emit shallow trapped electrons 3. Back to CHE, repeat for N=5 cycles • Strong impact on data retention: shallow electrons with bad data retention are removed, deep electrons improve VT loss (blue shift) H. T. Lue et al., IRPS 2006 Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 73 CT memories – Conclusions • Charge trap memories offer improved SILC immunity and better scalability • Material engineering is still an issue, no solutions are yet known for metal gate/highK/trapping layer • Reliability is a concern: • Lateral redistribution in MANOS/NROM • Thin bottom oxide • Main strength = 3D capability, allowing further sccaling from planar flash to new architectures Feb. 23, 2010 D. Ielmini, "Non volatile memories" – 2 74 37

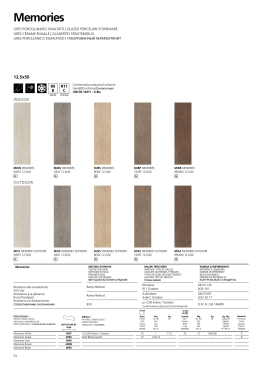

Scaricare