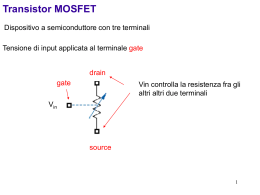

Studenti di Elettronica II, vedere A,B,C,D sul retro del foglio! cognome nome A A B C 3 3 2 I Totale matricola Cout IN L CIN=20fF, COUT=10pF – si calcoli U che minimizza il tempo di propagazione U2 U COUT 3 10 1012 3 U 3 500 8 15 CIN 20 10 V1(0)=-1V Si calcoli la tensione finale a cui si porta il nodo X a seguito della chiusura dell’interruttore B CX=1pF V2(0)=2V CY=10fF V4(0)=2V V3(0)=-1V QTOT 0 QTOT 0 (V1 0 V4 ) C X V2 0 V3 CY (VX V4 ) C X VX V3 CY 3 1 1e 12 3 10e 15 VX 1e 12 2 10e 12 VX 10e 15 10e 15 3 0.01 VX 2 VX 0.01 0.01 VX 0.98 / 1.01 0.97v D Si mostri la struttura di un transistore MOS a floating gate, e se ne illustri l’uso nelle memorie non volatili (es. FLASH) Il mos a floating gate a differenza di un mos classico presenta al di sopra del canale due piatti conduttivi isolati tra loro. La regione di contatto di gate avviene in quello superiore, mentre quello interno è lasciato flottante. La particolarità di questo dispositivo è che pilotando opportunamente la tensione di gate è possibile modificare la carica immagazzinata nel piatto flottante. Ciò al fine di alzare o abbassare la tensione di soglia. Se connessi come mostrato in figura è possibile immagazzinare un ‘1’ portando la tensione di soglia ad un valore superiore alla tensione della WL altrimenti viene immagazzinato un ‘0’. I Vdd A P X B N I1 I2 I3 I4 2 2 2 2 Totale Si assuma VTN= -0.1, VTP=0.1, SP=4, SN=1 e si trascuri l’effetto Body (=0). 1) Assumendo A=B, si calcoli per quale valore di tensione di ingresso si ha X=Vdd/2. 2) Si calcoli il consumo di potenza statico quanto A=B=0, e quando A=B=Vdd 3) Si calcoli la tensione in X quando A= 0, B=Vdd 4) Si calcoli il consumo di potenza statico del circuito nelle condizioni di cui al punto 3 NMOS: VGSb VB ,VDSb VX OFF : VGSb VTN VB 0.1v LIN : VGSb VTN VDSb VB 0.1v VX SAT : V V V V 0.1v V GSb TN DSb B X V VTN VX Caratteristica statica IN N off VTN PMOS: VGSa VA VDD ,VDSa VX VDD OFF : VGSa VTP VA 3.4v LIN : VGSa VTP VDSb VA 0.1v VX SAT : V V V V 0.1v V GSa TP DSb A X VIN VTP VX I) N sat P lin II) N lin P lin VTN P off III) P sat N lin VTP VDD VTP VDD VI VA VB VTP 1) Al fine di trovare in quale regione si ha Vx=Vdd/2, proviamo a trovare i valori di Vx nell’intersezioni con le rette che delimitano zona I,II,III. Se zona I : K N S N K S (VGS VTN ) 2 N N (VIN VTN ) 2 I DS , N 2 2 K S K P S P 2 2 P P I DS , P 2 (2(VGS VTP ) VDS VDS ) 2 (2(VIN VDD VTP ) (VX VDD ) (VX VDD ) ) Ugualiando le due correnti e ponendo Vx=Vin-Vtn si ottiene: K N S N 2 K P S P 2 VX (2(VX VDD VTP VTN ) (VX VDD ) (VX VDD ) 2 ) VX 14VX 24.4 0 2 2 Da cui Vx=2.04v > Vdd/2, pertanto non è in zona I, quindi o II o III. Se zona III : K P S P K P S P 2 2 I DS , P 2 (VGS VTP ) 2 (VIN VDD VTP ) K N S N K N S N 2 2 I ( 2 ( V V ) V V ) (2(VIN VTN ) VX VX ) DS , N GS TP DS DS 2 2 Ugualiando le due correnti e ponendo Vx=Vin-Vtp si ottiene: K S K P S P 2 2 (VX VDD ) 2 N N (2(VX VTN VTP ) VX VX ) VX 13.6VX 21.8 0 2 2 Da cui Vx=1.85v > Vdd/2, pertanto non è in zona II, ma in zona III. Quindi sostituendo nell’eq, di sopra Vx = Vdd/2 si ottiene VIN 1.97v ….continua in pagina 4 L L1 L2 L3 L4 VDD Clk X PD Clk N 2 2 2 Totale 2 Si assuma la capacità di ingresso dell’invertitore CINV=100fF: 1)Si realizzi il PD in modo che la funzione di uscita sia O=ABC’ + D’ B’C + CD. Sono disponibili ingressi nelle due fasi. 2) Sapendo che tutti i transistori N nel primo stadio hanno la stessa dimensione, si dimensioni la rete PD in modo che il ritardo di caso peggiore (90%) al nodo X sia 1ns 3) Si calcoli il ritardo attraverso l’invertitore se CO=1pF. Si consideri l’invertitore simmetrico. 4) Si calcoli il consumo di potenza dinamico del gate (entrambi gli stadi), con CINV e CO come indicato nei punti precedenti e fClk=200MHz 1) Al fine di realizzare la rete PD la funzione logica data va espressa al nodo x: X = O = ABC + DBC + CD) 2) Innanzi tutto individuiamo il cammino critico nella rete di pull down, che si ha per : (A,B,C,D ) : (0,1,0,0) (1,1,0,0) questo genera un fronte di discesa nel nodo X che genera un fronte di salita al nodo O. In tal caso la scarica avviene su 3 NMOS in PD + NMOS di valutazione = 4 NMOS. Partendo dalla formula del tempo di propagazione l’invertiamo ed otteniamo la Req,n e da questa otteniamo il fattore di forma Sn. tval90% = ln(10) * CL * ReqN => ReqN = 10-9/ (2,3*100*10-15) =4.34K RN = ReqN / #NMOS camm.crit = 4.34 / 4 =1.09K RN = RrifN * Srif /Sn => Sn = 5.39 * 1 / 1.09 = =4.955 VDD Clk O X A D C B B D C C 3) Supponiamo l’inverter dimensionato in modo simmetrico. Cin = Cox * Sn (1+ α) Lmin2 => Sn = Cinv /(Cox*(1+ α) Lmin2) Clk Sp=Sn* α =158 = 100* 10-15/ (3.45 * 10-15*3*0.352) = 79 Siccome l’inverter è simmetrico il ritardo può essere calcolato solo per il NMOS Req,N = RrifN /Sn = 5.39K/79 = 68.2 tfall90% = ln(10) * CL * ReqN = 2.3*10-12*68.2 = 157ps 4) La potenza dinamica può essere calcolata con la formula: PD = CL*Vdd2*f, pertanto so ha che : PD_DOMINO = 100fF*3.32*200MHz = 0.22mW PD_INV = 1pF*3.32*200MHz =2.2mW N PARAMETRI TECNOLOGICI (Vdd = 3.3 V) n channel VT 0 0.7 V K' 100 μA/V 2 Cox 3.45 fF/ μm2 L min 0.35 μm λ 0 γ 0 R eq (Vgs | Vdd |,90%, S 1) 5.39 kΩ p channel 0.7 50 μA/V 2 3.45 fF/ μm2 0.35 μm 0 0 10.78 kΩ 2) Va = Vb = 0 => zona I, la corrente può quindi essere calcolata considerando la corrente sul transistor N che è in saturazione. K S K S I DD I DS , N N N (VGS VTN ) 2 N N (VIN VTN ) 2 100 106 0.5 0.01 0.5uA 2 2 PS VDD I DD 1.65uW Va = Vb = Vdd => zona III, la corrente può quindi essere calcolata considerando la corrente sul transistor P che è in saturazione. K S K P S P (VGS VTP ) 2 N N (VIN VDD VTP ) 2 50 106 2 0.01 1uA 2 2 3.3uW I DD I DS , P PS VDD I DD 3) Va =0 => Vgs,p = Vdd => PMOS in lineare. Vb =Vdd => Vgs,n = Vdd => NMOS in lineare Imponendo l’ugualianza delle delle due correnti nel ramo di pull-up e pull-down e sostituendo Va =0 e Vb =Vdd si ottiene : K S K P S P 2 (2(VDD VTP ) (VX VDD ) (VX VDD ) 2 ) N N (2(VDD VTN ) VX VX ) 2 2 2 VX 7.2VX 23.1 0 VX 2.4v 4) Calcoliamo la corrente sul ramo di pull-down per i valori di sopra K N S N 2 (2(VDD VTN ) VX VX ) 50 106 (2 (3.4) 2.4 (2.4) 2 ) 0.528mA 2 1.74mW I DD I DS , N PS VDD I DD

Scaricare