INTRODUZIONE AI CONVERTITORI ANALOGICO-DIGITALI (ADC) 1 Fondamenti di elettronica L’IDEA DELLA CONVERSIONE ANALOGICO-DIGITALE Tensione di fondo scala , VFS VFS Intervallo di valori Vin a cui corrisponde lo stesso codice 2n intervalli … Vin Livello di tensione di ingresso 2 N=5 (D1D2..Dn=…101) Uscita : …101 N=4 (D1D2..Dn=…100) N=3 (D1D2..Dn=…011) 0 LSB VFS n 2 Risoluzione Fondamenti di elettronica RELAZIONE INGRESSO-USCITA di un ADC IDEALE VFS Codice di uscita 2 n Minima variazione dell’ingresso in grado di produrre un cambiamento nel codice di uscita. Risoluzione 111 1 LSB 110 ADC con 12 bit e VFS=10V 101 2.44mV di risoluzione. 100 011 Intervallo di valori Vin a cui corrisponde lo stesso codice 010 001 N 3 VFS 2n 000 1/8 1/4 1/2 3/4 Tensione di ingresso 1 Vin/VFS Fondamenti di elettronica ERRORE DI QUANTIZZAZIONE 111 110 101 100 011 Il codice di uscita SOTTOSTIMA la tensione di ingresso 010 001 000 Il codice di uscita SOVRASTIMA la tensione di ingresso 1/8 1/4 1/2 3/4 1 Vin/VFS ½ LSB -½ LSB 4 Fondamenti di elettronica ERRORE DI QUANTIZZAZIONE in ADC REALE 111 110 101 100 011 010 001 000 1/4 1/2 3/4 1 ½ LSB -½ LSB 5 Fondamenti di elettronica NON - LINEARITA’ DIFFERENZIALE 111 111 111 110 110 110 101 101 101 100 100 100 011 011 011 010 001 010 001 010 001 000 000 000 Larghezza del gradino ideale pari a 1 LSB. 1/4 1/2 3/4 1 Larghezza del gradino ERRORE di linearità differenziale DNL, Differential Non Linearity 6 Vin/VFS Scostamento tra la larghezza del gradino i-esimo ed il suo valore ideale di 1 LSB Fondamenti di elettronica NON - LINEARITA’ INTEGRALE 111 111 110 110 101 101 100 100 011 011 010 001 010 001 000 000 Retta interpolatrice 1/4 ERRORE di linearità integrale INL, Integral Non Linearity 7 1/2 3/4 1 Scostamento tra il centro del gradino reale e quello teorico Fondamenti di elettronica ERRORE per un CODICE MANCANTE 111 110 101 Codice che non uscirà mai 100 011 010 001 000 Vin/VFS 1/4 Se manca un codice, l’errore di quantizzazione è necessariamente maggiore di 1 LSB 8 1/2 3/4 1 1 LSB ½ LSB -½ LSB Fondamenti di elettronica ERRORE di GUADAGNO 111 110 101 Pendenza ideale 100 011 010 001 000 1/8 1/4 9 1/2 3/4 Tensione di ingresso 1 Vin/VFS Fondamenti di elettronica ERRORE di OFFSET 111 110 101 Offset 100 011 010 001 Vin/VFS 000 Offset 10 1/8 1/4 1/2 3/4 Tensione di ingresso 1 Fondamenti di elettronica ALTRE CARATTERISTICHE Dipendenza minima dei parametri dalla temperatura (espressi nei coefficienti di temperatura per gli errori di guadagno, offset e linearità) Monotonicità della risposta (il codice di uscita cresce sempre al crescere della tensione di ingresso) 11 Fondamenti di elettronica CONVERTITORI ANALOGICO-DIGITALI, ADC Ingresso analogico Vin oppure Iin Grandezza di riferimento Convertitore A/D D1, D2, …Dn Uscita digitale VFS, IFS ADC, Analog to Digital Converter D1D2…Dn Parola digitale di uscita BIT meno significativo – LSB, Least Significant Bit BIT più significativo –MSB, Most Significant Bit N è il numero decimale intero corrispondente alla parola digitale D1D2…Dn: N D1 2n 1 D2 2n 2 ... Dn 20 12 Fondamenti di elettronica STRUTTURA BASE DEI CONVERTITORI Segnale analogico da convertire Comparatore VX - VR(t) + Tensione di riferimento VR(t) viene fatta variare con l’obiettivo di eguagliare VX (entro l’errore di quantizzazione del convertitore) : VX VR (t ' ) 0.5 LSB Insieme di coefficienti binari D1D2…Dn che generano VR(t’) (e quindi VX ) 13 Fondamenti di elettronica CONVERTITORE A CONTATORE-RAMPA Principio di funzionamento Segnale analogico VX in INGRESSO VR(t) + VDAC DAC 2n valori discreti di VR a n bit Codice digitale di USCITA t CONTATORE a n bit 14 Clock (ck) Fondamenti di elettronica LOGICA di CONTROLLO Segnale analogico in INGRESSO VX VR(t) - + DAC a n bit Codice digitale di USCITA S R Flip - Flop Q Q E.O.C. CONTATORE a n bit (End Of Conversion) Clock (fck) Reset 15 Fondamenti di elettronica TEMPO di CONVERSIONE Il tempo di conversione, Tconv, varia proporzionalmente a VX : TMIN per VX = 0V TMIN = 0 s TMAX per VX VFS 2n TM AX f ck Velocità di conversione relativamente bassa Esempio : ADC a 10 bit e fck=1 MHz TMAX=1.024 ms Al massimo possono essere previste ~1000 conversioni al secondo 16 Fondamenti di elettronica ALTRE CARATTERISTICHE • Semplicità circuitale • Poco costoso • Sovrastima di VX VR(t)VDAC K+1 VX K t 17 Fondamenti di elettronica CONVERTITORE A INSEGUIMENTO Principio di funzionamento Segnale analogico VX in INGRESSO VR(t) + DAC a n bit Codice digitale di USCITA CONTATORE a n bit Up Logica Clock (ck) Down 18 Fondamenti di elettronica ANDAMENTO del SEGNALE VR(t),VX VX - VR(t) + 1 LSB VX DAC a n bit Codice digitale di USCITA CONTATORE a n bit Up Logica Down Clock VR(t), segnale in uscita dal DAC t 19 Fondamenti di elettronica PERDITA di ACQUISIZIONE VR(t),VX VX Fronte rapido di VX Il DAC ha perso l’aggancio VR(t) Perdita di acquisizione La parola immagazzinata dal contatore NON è rappresentativa di VX 20 Fondamenti di elettronica FREQUENZA MASSIMA di AGGANCIO Massima velocità di variazione dell’ingresso sinusoidale VX: 1/fin VFS d VFS sin( 2f in t ) VFS f in dt 2 t 0 t=0 Massima velocità di variazione dell’uscita del DAC: V 1 LSB 1 LSB f ck FS f ck n Periodo di clock 2 VFS fin 21 VFS 2n f ck da cui fin f ck 2n Fondamenti di elettronica METODO a RICERCA BINARIA Trovare la pallina più pesante ? 1g 1g 1g 1g 1g 1g 2g 1g 1g 1g 1g 1g 1g 1g 1g 2g 2g 1g 1g 1g 2g 1g Partendo da 8 palline, sono bastate 3 pesate ! In generale : partendo da 2n elementi, bastano n passaggi. 22 Fondamenti di elettronica CONVERTITORE ad APPROSSIMAZIONI SUCCESSIVE Segnale analogico VX in INGRESSO - VR(t) + DAC a n bit Codice digitale di USCITA LOGICA di CONTROLLO SAR – Successive Approximation Register Start Clock E.O.C. 23 Fondamenti di elettronica Esempio di approssimazioni successive VR(t),VX VFS 111 110 3VFS 4 101 100 VFS 2 110 101 VX 100 VR(t) 011 010 100 Codice finale VFS 4 001 000 0 T 24 2T 3T 4T t Fondamenti di elettronica TEMPO di CONVERSIONE TConv Per convertitori ad n bit n f ck Velocità di conversione elevata Esempio : ADC a 10 bit e fck=1 MHz TConv= 10 s Si potrebbe raggiungere un tasso di 100.000 conversioni/s Fattori limitanti la frequenza di clock, fck : • tempo di assestamento del DAC • tempo di risposta del comparatore (in particolare quando VX e VR differiscono di poco) • tempo di risposta della SAR 25 Fondamenti di elettronica FREQUENZA MASSIMA del SEGNALE da CONVERTIRE E’ fondamentale che il segnale di ingresso resti costante entro ±½LSB durante il tempo di conversione Massima velocità di variazione di un ingresso sinusoidale : d VFS sin( 2f in t ) VFS f in dt 2 t 0 TConv Durata della conversione : VFS fin V n .5 FS f ck 2n Esempio : ADC a 10 bit e fck=1 MHz n f ck da cui f in .5 f ck n 2n fin< 16 Hz per un segnale sinusoidale con ampiezza picco-picco pari a VFS 26 Fondamenti di elettronica

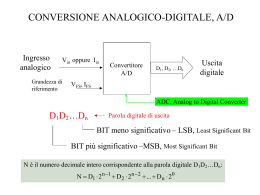

Scaricare