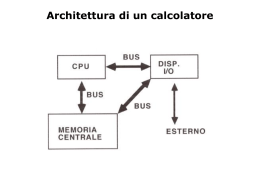

2 Unità centrale CPU Controllo Unità Aritmetico logica Un calcolatore digitale è composto da CPU, memorie e dispositivi di input/output. Dispositivi di ingresso\uscita Registri Memoria Principale Unità Disco Display bus 3 Central Processing Unit Descrizione Organizzazione Funzionamento 4 La CPU e’ il “cervello” del calcolatore e il suo compito è quello di eseguire i programmi, residenti nella memoria, leggendo ed eseguendo le loro istruzioni. I componenti sono collegati tra loro attraverso dei bus. 5 Un bus, che è un gruppo di fili tra loro paralleli, ha il compito di trasportare segnali di controllo, dati e indirizzi. Il Bus puo’ essere esterno alla CPU e ha lo scopo di permettere la comunicazione tra la memoria e i dispositivi di I\O. 6 A+B Registri A B A B L’organizzazione interna di una CPU è caratterizzata dal data path, che è costituito da una serie di componenti, tra i quali l’ALU, i registri, e molti bus di comunicazione. Registro ALU dell’ingresso Bus di ingresso dell’ALU ALU A+B Registro di uscita dell’ALU l 7 Arithmetic Logic Unit L’ALU esegue dei calcoli matematici sui dati e poi memorizza il risultato in un registro in uscita. I dati hanno due possibilità di percorsi: registro-memoria i dati vengono trasportati dal registro di uscita alle memoria e/o viceversa; 8 La memoria della CPU, che è ad alta velocità, viene utilizzata per memorizzare temporaneamente istruzioni e dati più frequentemente acceduti. 9 Il funzionamento della CPU si basa su una sequenza di operazioni, che insieme prendono il nome di fetch-decode-execute: 1 prelievo delle istruzioni dalla memoria, e immissione di queste nel registro delle istruzioni; Caricamento del nuovo program counter 2 dterminazione del tipo di istrizzone 3 ricerca operandi ed esegui l’istruzione. 10 L’hardware e’ l’insieme degli elementi costitutivi di un elaboratore Il software serve per utilizzare il calcolatore. Il software suddivide le istruzioni in piccole porzioni che esegue in modo più semplice attraverso un interprete, mentre l’hardware le esegue direttamente. 11 Durante gli anni 70’ dello scorso secolo il mercato dei calcolatori era in pieno sviluppo e aumentava sempre di più la richiesta di calcolatori a basso costo. Lo sviluppo di software eliminava i limiti di costo inerenti alla esecuzione di istruzioni complesse. 12 Ci sono dei principi di progettazione chiamati principi di progettazione RISC, che gli architetti delle CPU possono seguire. Tra i più importanti troviamo: 13 Tutte le istruzioni comuni vengono eseguite direttamente dall’hardware e non vengono interpretate da microcodice, per cui il sistema e’ più veloce. Mentre per i calcolatori che implementano istruction set CISC le istruzioni vengono scomposte in miscroistruzioni anche se questo passaggio rallenta la macchina. 14 I calcolatori moderni cercano di iniziare piu’ istruzioni possibili al secondo. Il parallelismo svolge quindi un ruolo fondamentale nel miglioramento delle prestazioni perché inviare una grossa quantità di istruzioni lente a intervalli brevi e’ possibile solo se istruzioni multiple si possono eseguire contemporaneamente. 15 Una limitazione della velocita’ con la quale vengono mandate in esecuzione le istruzioni e’ dovuta alla decodifica delle istruzioni. Per eliminare questo problema bisogna usare istruzioni con struttura regolare, di lunghezza fissa, con un numero limitato di campi e con formati molto simili. 16 La maggior parte delle operazioni di load e store trasferiscono dati tra la memoria e i registri. Queste operazioni di trasferimento sono piu’ lente e quindi talvolta si sovrappongono con le altre istruzioni; 17 Poiche’ l’accesso alla memoria e’ molto lento e’ necessario disporre di molti registri, almeno 32, in modo che un’istruzione, una volta letta, possa essere conservata in un registro fin quando non e’ piu’ necessaria. 18 Un modo per accelerare il funzionamento dei chip e’ aumentare la velocità del clock e i ricercatori utilizzano il parallelismo, nel tentativo di eseguire due o piu’ operazioni contemporaneamente per ottenere maggiori prestazioni con la frequenza di clock a disposizione. 19 Per eseguire piu’ istruzioni parallelamente si usava un prefetch buffer, che le prelevava invece di aspettare la lettura completa della memoria. Quindi il processo si divideva in due parti: lettura della memoria e esecuzione. Stadio di lettura delle istruzioni Stadio di decodifica delle istruzioni Stadio di lettura degli operandi Stadio di esecuzione delle istruzioni Stadio di scrittura 20 Registri +lente Da 32KB a alcuni MB Cache +capacita`di memorizzazione Memoria principale Da 16MB a decine di GB Dischi magnetici Nastri Memorizzazione permanente Dischi ottici Memorizzazione di archivi Da alcuni GB a decine di TB 21 Storicamente la capacita’ di accesso ai dati da parte delle CPU e’ sempre stata limitata dalla velocita’ di I/O della memoria. In realta`non si tratta di un problema tecnologico, ma economico; gli ingegneri sono in grado di costruire memorie veloci come le CPU, ma il costo complessivo del sistema sarebbe molto elevato. . 22 La validita’ di questo metodo dipende dalla quantità` di parole che si trovano nella cache. Statisticamente i programmi non accedono alla memoria a caso: se La CPU richiede un dato della memoria di indirizzo A, e` assai probabile che l`accesso seguente si troverà` nelle vicinanze di A. CPU cache Memoria principale bus Configurazione comune di CPU, cache e memoria 23 La memoria e`quella parte del calcolatore dove vengono immagazzinati i programmi e i dati. Alcuni ricercatori del settore usano il termine store (magazzino) o storage (immagazzinamento) invece di memoria, anche se il termine storage solitamente si riferisce alla memorizzazione su disco.

Scaricare

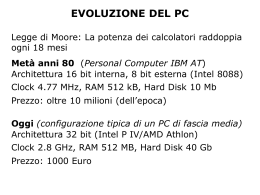

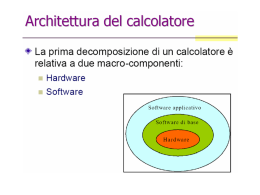

![[13] Data la CPU con pipeline nella pagina seguente: a](http://s2.diazilla.com/store/data/000261227_1-2c573294ec477e56a9fb3303e6a07e93-260x520.png)