Progettazione in VHDL del Pixel Shader v 1.4

Pag. 148

PARTE QUARTA

Progettazione in VHDL del Pixel

Shader v.1.4

Autori:

Alessandro Giorgetti

Daniele Petraccini

La presente parte è organizzata nei seguenti capitoli:

Capitolo 5. Specifiche di progetto del Pixel Shader v.1.4

Capitolo 6. Test bench per la simulazione in VHDL del processore

Capitolo 7. Architettura interna del Pixel Shader v.1.4

Capitolo 8. Simulazioni

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 149

Capitolo 5. Specifiche di progetto del Pixel Shader v.1.4

5.1. Linee generali del progetto

La presente parte della tesina è relativa alla progettazione in linguaggio

VHDL del Pixel Shader, processore matematico del quale si è fornita una

introduzione nel paragrafo 1.9.3.

Prima di addentrarci nella discussione concernente la realizzazione del

processore è bene esporre le linee generali del progetto, in particolar modo le

specifiche, gli obiettivi e le limitazioni.

Le specifiche sul funzionamento generale del processore sono state

estratte dalla documentazione che le principali ditte costruttrici di schede

grafiche mettono a disposizione dei programmatori: nei siti web di ATI,

NVIDIA e anche nel sito Microsoft si trovano spiegazioni dettagliate del

funzionamento di un pixel shader; tali informazioni sono state da noi usate

come specifiche generali di progetto del Pixel Shader, versione 1.4.

La documentazione di cui sopra non contiene tuttavia informazioni

sull’architettura interna del processore; quest’ultima deve essere così progettata

sulla base delle funzionalità note del processore, seguendo il criterio della

razionalità e cercando di aumentare, ove possibile, la velocità di esecuzione

delle diverse operazioni.

E’ bene fin da subito mettere in evidenza un aspetto importante. Il pixel

shader è per sua natura un processore molto complesso, sia per il fatto di dover

compiere operazioni matematiche in virgola mobile, sia per la necessità di

eseguire un grandissimo numero di istruzioni nell’unità di tempo. A fronte di

tali problematiche, nell’ambito della presente tesina sono state introdotte

alcune semplificazioni.

Innanzitutto le ALU floating-point sono state progettate a livello

comportamentale. D’altronde la possibilità di descrivere i blocchi funzionali di

un sistema digitale usando diversi livelli di astrazione è una caratteristica

fondamentale del linguaggio VHDL, che noi abbiamo usato a nostro

vantaggio.

In secondo luogo, per maggior semplicità, la struttura del processore è

stata concepita per eseguire le operazioni di caricamento, decodifica ed esecuzione

delle istruzioni ciascuna in un momento diverso, ovvero non si è provveduto a

parallelizzare le tre fasi, come invece avviene comunemente nei processori, allo

scopo di aumentarne le prestazioni.

Occorre fare una precisazione relativa al periodo del clock di sistema e

più in generale ai ritardi associati ai vari blocchi costituenti. Sotto tale punto di

vista, il componente senza dubbio più critico è l’ALU floating-point, descritto

nel nostro progetto a livello behavioural. La scorrelazione dall’hardware che

deriva da una così elevata astrazione non consente di stimare i ritardi relativi

alle porte logiche che implementeranno fisicamente l’ALU e quindi neanche il

minimo periodo di clock, la cui scelta è indissolubilmente legata a tali ritardi.

La scelta del clock è stata allora basata su una stima grossolana dei ritardi

degli altri blocchi componenti, più semplici e dunque descrivibili in modo da

essere maggiormente legati all’hardware. I tempi di esecuzione delle singole

istruzioni dell’ALU sono stati fissati in maniera piuttosto arbitraria, ma in ogni

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 150

caso la scelta è stata operata in maniera coerente, tenendo conto della

complessità di ciascuna operazione.

Alla luce di quanto esposto finora, l’obiettivo che si vuole raggiungere

con il progetto in esame è il seguente: ottenere una descrizione VHDL del

Pixel Shader che garantisca una funzionalità del processore compatibile con le

specifiche fornite da Microsoft, senza tuttavia ambire ad una architettura

direttamente implementabile in hardware e paragonabile, per prestazioni, ai

pixel shader attualmente presenti nel mercato. Seppur con le ovvie limitazioni

derivanti dall’intrinseca complessità del sistema oggetto di analisi, si cercherà di

progettare l’architettura del processore in maniera “intelligente”, così da

ottimizzare l’esecuzione dell’intero instruction-set.

5.2. Terminologia

Prima di addentrarci nell’analisi del Pixel Shader ci sembra utile spendere

alcune righe per spiegare la terminologia adottata. L’espressione pixel shader non

ha un significato univoco, ma può indicare in realtà cose tra loro differenti:

§ un progettista che parla di “pixel shader” si riferisce al processore,

ovvero ad una specifica parte dell’hardware della scheda grafica

che svolge funzionalità ben definite

§ per il programmatore, il “pixel shader” rappresenta il codice che

viene caricato nella memoria interna del processore e

successivamente eseguito.

Allo scopo di evitare confusione, nel seguito della tesina indicheremo con l’espressione

“Pixel Shader” (nota le iniziali maiuscole) il particolare processore da noi progettato in VHDL.

L’espressione “pixel shader” sarà invece usata in senso lato, per intendere l’intera classe di

processori. Infine, il codice caricato all’interno del processore sarà semplicemente indicato con

il termine “shader”.

Prima di proseguire è necessaria un’ultima precisazione. Esistono varie versioni di pixel

shader, che in linea di massima si differenziano tra loro per il diverso numero di registri interni

al processore e per il diverso set di istruzioni. Al momento attuale (giugno 2002) esistono le

versioni 1.0, 1.1, 1.2, 1.3, 1.4. Noi abbiamo scelto di implementare l’ultima versione e di

conseguenza il processore da noi progettato sarà indicato come Pixel Shader v.1.4. Le specifiche

di funzionamento indicate nel resto di questo capitolo sono da considerarsi proprie di tale

versione.

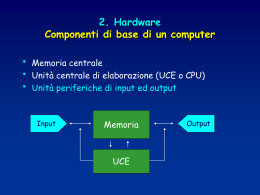

5.3. Schema di principio del Pixel Shader v.1.4

Dalla figura a pagina seguente, illustrante lo schema di principio del Pixel

Shader v.1.4, sono visibili i blocchi di base che formano l’architettura interna

del processore: l’unità logico aritmetica (ALU), i banchi di registri e

l’Instruction Pool.

Il funzionamento del processore può essere molto sommariamente

descritto come segue: i dati sul pixel corrente provenienti dall’esterno sono

memorizzati in opportuni registri in ingresso; l’ALU compie una serie di

operazioni su tali dati e mette i risultati su opportuni registri. Al termine

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 151

dell’esecuzione delle istruzioni, i dati presenti su un apposito registro di uscita

vengono inviati al resto della pipeline grafica.

Color Registers

PIXEL SHADER

v0

v1

Constant

Registers

Texture

Registers

c0

t0

c1

t1

Pixel Shader

ALU

Instruction

Pool

Texture

t5

Addressing

c7

r0

r1

r5

Temporary Registers

Output

Analizziamo ora con maggiore dettaglio la struttura del Pixel Shader,

partendo dalla descrizione dei quattro banchi di registri.

5.3.1 Banco di registri c

Il banco c contiene 8 registri, indicati con c0..c7, detti registri delle costanti.

Essi sono registri di sola lettura usati per contenere dei valori costanti, caricati

prima dell’esecuzione dello shader. Ciascun registro c è organizzato in quattro

valori reali.

5.3.2 Banco di registri r

Il banco r contiene 6 registri, indicati con r0..r5, detti registri temporanei.

Essi sono registri in lettura/scrittura usati per memorizzare dei dati

temporanei, sotto forma di quaterne di valori reali. Il registro r0 funge inoltre

da registro di uscita: al termine dell’esecuzione dello shader, il contenuto di r0 è

il colore di uscita per il pixel corrente.

5.3.3 Banco di registri t

Il banco t contiene 6 registri, indicati con t0..t5, detti registri delle texture.

Essi sono registri di sola lettura caricati prima dell’esecuzione dello shader con

le coordinate delle texture dei vari stage. Ciascun registro è formato da quattro

valori reali.

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 152

5.3.4 Banco di registri v

Il banco v contiene i registri v0 e v1, detti registri del colore, in quanto sono

comunemente caricati con i dati rispettivamente del colore diffuso e del colore

speculare associati al pixel corrente. Ogni registro è organizzato in quattro

valori reali, che possono essere visti come le componenti R, G, B, A del colore.

I registri v sono caricati prima dell’esecuzione dello shader e possono essere

usati solo in lettura.

Osservazioni sui registri - Nei paragrafi precedenti abbiamo detto che

ciascun registro interno al Pixel Shader contiene quattro valori reali; questa

affermazione merita ora un chiarimento. Secondo le specifiche sul pixel shader

alle quali abbiamo fatto riferimento nel nostro progetto, le quantità da noi

sopra definite reali debbono essere implementate nel formato fixed-point; nella

nostra versione del processore abbiamo invece deciso di operare una

estensione, memorizzando ogni quantità reale come valore floating-point. Tale

scelta è legata essenzialmente al fatto che il Pixel Shader è stato progettato in

una fase successiva al Vertex Shader, il che ha permesso di riutilizzare molti

componenti già progettati, ed inoltre procedure, funzioni e librerie già scritte.

Essendo il Vertex Shader basato su una aritmetica a virgola mobile, il Pixel

Shader ha risentito direttamente di tale scelta.

Singole componenti dei registri - Ciascun registro racchiude quattro

valori floating-point, che sono interpretati come le componenti R, G, B, A del

dato, pensato come colore. Per fare riferimento ad una singola componente

esiste una comoda notazione che fa uso dei suffissi .r, .g, .b, .a da applicare al

registro. Facciamo un esempio: la componente G del registro v0 sarà indicata

con la notazione v0.g.

Range dei registri - Le specifiche impongono un range ai quattro banchi

di registri, ovvero fissano il valore minimo e quello massimo per il dato

contenuto in ciascun registro. Ad esempio, i registri delle costanti possono

contenere valori compresi tra -1 e +1, mentre per i registri del colore il range è

fissato nell’intervallo compreso tra 0 e +1. Nella nostra implementazione si è

supposto di poter memorizzare quantità in virgola mobile senza alcuna

restrizione sul range.

5.3.5 Instruction Pool

Oltre ai quattro banchi di registri finora descritti esiste un ulteriore ed

importante elemento di memoria all’interno del Pixel Shader: si tratta

dell’Instruction Pool, blocco la cui funzione è memorizzare lo shader, ovvero

la sequenza di istruzioni che dovranno essere eseguite una volta caricati i dati

relativi al pixel corrente.

5.3.6 Pixel Shader ALU

L’unità aritmetico logica del Pixel Shader esegue istruzioni di due tipi:

§ istruzioni aritmetiche: si tratta di elementari operazioni

matematiche sui dati in ingresso

Progettazione in VHDL del Pixel Shader v 1.4

§

Pag. 153

istruzioni di texture addressing: eseguono una elaborazione

delle coordinate delle texture, eventualmente usando tali dati per

effettuare il campionamento di una texture (texture sampling); in

questo caso entra in gioco un blocco esterno al Pixel Shader,

denominato Texture Sampler.

5.3.7 Funzionamento del Pixel Shader

Ora che abbiamo introdotto tutti i blocchi fondamentali che

compongono il Pixel Shader, possiamo spiegare il funzionamento del

processore con un maggiore grado di dettaglio.

Innanzitutto dobbiamo distinguere le tre fasi di funzionamento che

sono: il caricamento dello shader, il caricamento del pixel e l’esecuzione dello

shader.

La prima fase in ordine temporale è il caricamento dello shader, che consiste

nella memorizzazione all’interno dell’Instruction Pool di tutte le istruzioni da

eseguire per ciascun pixel. In tale fase si effettua anche il caricamento del

banco di registri c, ovvero delle costanti che possono essere utilizzate

all’interno delle varie istruzioni.

La seconda fase è il caricamento del pixel. Essa consiste nella

memorizzazione del colore diffuso e del colore speculare rispettivamente nei

registri v0 e v1 e nella memorizzazione delle coordinate delle texture nel banco

di registri t. Precisiamo che i dati sul colore e sulle texture sono riferiti al pixel

corrente.

La terza fase è l’esecuzione dello shader, durante la quale vengono eseguite

tutte le istruzioni presenti all’interno dell’Instruction Pool. Terminato lo

shader, il contenuto del registro r0 rappresenta il colore di uscita per il pixel

corrente.

Esaurita la terza fase è possibile caricare il pixel successivo (ovvero si

ritorna alla seconda fase) e rieseguire lo shader partendo dalla prima istruzione

(terza fase). Una volta che tutti i pixel sono stati elaborati con lo shader

impostato, si ha la facoltà di caricare il processore con un nuovo shader e

dunque ricominciare il funzionamento partendo dalla prima fase.

5.4. Architettura interna dell’ALU

Ritornando alla figura di pag. 151, illustrante l’architettura del Pixel

Shader, si vede che il posto centrale è occupato dall’ALU, sulla cui funzionalità

abbiamo fornito alcuni cenni. In questo paragrafo vogliamo analizzare più in

dettaglio la struttura interna e le funzioni svolte da tale blocco fondamentale.

La figura all’inizio di pagina seguente, tratta dalla documentazione

Microsoft, mostra lo schema di principio dell’ALU del Pixel Shader. Il dato

principale da mettere in evidenza è la struttura a pipeline parallele dell’ALU:

§ l’area ombreggiata a sinistra indica la cosiddetta vector pipeline, la

quale opera su dati vettoriali costituiti dalla terna di canali (R, G,

B); la pipeline in questione viene anche chiamata color pipe

§ l’area ombreggiata a destra indica la cosiddetta scalar pipeline, che

opera invece su dati scalari, rappresentati dal canale (A); ad essa

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 154

ci si riferisce anche con l’espressione alpha pipe.

Le due pipeline operano indipendentemente tra loro e le operazioni che

ciascuna di esse esegue in un certo istante possono anche essere diverse.

Procediamo ora alla descrizione in ordine logico dei singoli blocchi

presenti nel diagramma, le cui etichette indicano - con espressione inglese - la

funzione da ciascuno di essi svolta.

Input Registers - Tali registri forniscono i dati in ingresso all’ALU del

Pixel Shader sotto forma di quaterne (R, G, B, A).

Component Copy - Tale blocco rappresenta uno swizzler, ovvero un

dispositivo che esegue la replica del contenuto di un canale specificato sugli

altri canali. Ad esso ci si riferisce anche con l’espressione inglese source register

selector.

Modify Data - Chiamato anche source register modifier, esegue delle

elementari operazioni matematiche sui dati letti dai registri sorgenti prima di

essere usati per l’esecuzione delle istruzioni.

Execute Instruction - Il blocco in questione rappresenta la vera e

propria esecuzione delle istruzioni, il cui scopo è quello di effettuare operazioni

aritmetiche o di texture addressing sui dati in ingresso. Nel caso in cui la vector

pipepine e la scalar pipeline eseguano parallelamente due istruzioni diverse si

parla di instruction pairing (su tale argomento ritorneremo nel paragrafo 5.11).

Modify Result - Chiamato anche instruction modifier, tale blocco esegue

delle elementari operazioni matematiche sul risultato di un’istruzione prima

della scrittura sul registro.

Masking - L’operazione di mascheratura permette di controllare,

attraverso la cosiddetta destination register write mask, quali componenti del

registro destinazione sono scritte dall’istruzione.

Output Register - Indica il registro destinazione.

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 155

5.5. Istruzioni del Pixel Shader v.1.4

Nel paragrafo precedente abbiamo visto che il dato che viene scritto sul

registro destinazione dopo l’esecuzione di un’istruzione dipende non soltanto

dall’istruzione stessa, ma anche dallo swizzler, dal source register modifier,

dall’instruction modifier e dalla write mask.

Nel presente paragrafo vogliamo fissare l’attenzione solo sulla parte di

esecuzione dell’istruzione vera e propria, rimandando a paragrafi successivi la

descrizione dettagliata di tutti gli altri blocchi che influenzano il dato finale.

Nelle pagine che seguono esporremo con chiarezza l’intero instructionset del Pixel Shader v.1.4, precisando le regole di sintassi necessarie per la

scrittura di uno shader corretto.

5.5.1 Tipi di istruzioni

L’instruction-set del Pixel Shader v.1.4 può essere suddiviso in cinque

tipi diversi di istruzioni:

§ version instruction (PS): in uno shader c’è sempre una sola

istruzione atta a specificarne la versione e tale istruzione deve

essere la prima.

§ constant instruction (DEF): serve a definire delle costanti.

§ phase instruction (PHASE): serve a scindere lo shader in due

fasi, denominate fase 1 e fase 2; l’istruzione PHASE viene anche

definita phase marker.

§ texture address instructions: manipolano i dati relativi alle

coordinate delle texture associate ai vari stage.

§ arithmetic instructions: includono comuni operazioni

matematiche.

5.5.2 Struttura di uno shader

Le istruzioni presenti all’interno di uno shader devono apparire in un

ordine ben definito ed inoltre esiste un massimo numero di istruzioni

consentite. Allo scopo si osservi lo schema sottostante, che illustra il cosiddetto

instruction flow dello shader 1.4.

La prima istruzione serve ad indicare la versione dello shader.

Successivamente ci sono le istruzioni per la definizione delle costanti.

Nella prima fase dello shader possono essere usate fino a 6 istruzioni di

texture addressing seguite da un massimo di 8 istruzioni aritmetiche.

Segue l’istruzione PHASE, che separa la fase 1 dalla fase 2.

Nella seconda fase dello shader si possono usare ancora 6 istruzioni di

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 156

texture addressing seguite da un massimo di 8 istruzioni aritmetiche.

La struttura qui presentata definisce il “massimo” shader che può essere

scritto, nel senso che non possono essere aggiunte ulteriori istruzioni al di fuori

dello schema mostrato. E’ tuttavia possibile fare shader più “piccoli”, ovvero

usare un numero inferiore di istruzioni. In particolare valgono le seguenti

regole:

§ le istruzioni per la definizione di costanti non sono obbligatorie

§ è possibile scrivere uno shader che abbia solo la fase 2: allo scopo

è sufficiente non inserire alcuna istruzione nella fase 1 e

tralasciare anche l’istruzione PHASE, che resta sottintesa.

5.5.3 Istruzioni PS, DEF, PHASE

Cominciamo la descrizione dettagliata dell’instruction-set del Pixel

Shader v.1.4 partendo dalle seguenti istruzioni: version instruction, constant

instruction, phase instruction.

Istruzione PS - E’ l’istruzione che serve a definire la versione dello

shader. La sua sintassi è la seguente:

ps.1.4

Ricordiamo che tale istruzione è la prima dello shader.

Istruzione DEF - Tale istruzione fornisce un metodo per definire delle

costanti da utilizzare all’interno dello shader. La sua sintassi è la seguente:

def dest, fVal0, fVal1, fVal2, fVal3

dest : rappresenta il registro destinazione, che può essere uno dei

registri c0..c7, più brevemente indicato con cn.

fVal0, fVal1, fVal2, fVal3 : rappresentano dei valori floatingpoint, che devono essere compresi tra -1 e +1.

Ricordiamo che la DEF deve essere inserita dopo l’istruzione PS e prima

di qualsiasi istruzione aritmetica o di texture addressing.

Istruzione PHASE - Serve a marcare la transizione tra la fase 1 e la fase

2. Nel caso l’istruzione PHASE non sia presente, l’intero shader è considerato in

fase 2. La sintassi è semplice:

phase

5.5.4 Istruzioni aritmetiche

Forniamo l’elenco completo delle istruzioni aritmetiche, spiegandone la

sintassi e le peculiarità.

Istruzione ADD - Esegue l’addizione componente per componente di

due registri. Sintassi:

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 157

add dest, src0, src1

: il registro destinazione è un registro rn.

src0, src1 : i registri sorgenti possono essere cn, rn nella fase 1; cn, rn,

vn nella fase 2.

L’istruzione evidenziata esegue la seguente operazione:

dest

dest = src0 + src1

che, per chiarezza, riportiamo sviluppata nelle singole componenti:

dest.r = src0.r + src1.r

dest.g = src0.g + src1.g

dest.b = src0.b + src1.b

dest.a = src0.a + src1.a

Istruzione BEM - Applica una trasformazione che serve a simulare il

cosiddetto bump environment-mapping. Sintassi:

bem dest.rg, src0, src1

: il registro destinazione è un registro rn.

src0 : è un registro cn o rn.

src1 : è un registro rn.

L’istruzione in questione esegue i seguenti calcoli:

(n: destination register index)

dest

dest.r = src0.r + M00(stage n) * src1.r

+ M10(stage n) * src1.g

dest.g = src0.g + M01(stage n) * src1.r

+ M11(stage n) * src1.g

Le quantità M00, M10, M01, M11 che compaiono nelle formule

precedenti sono gli elementi di una matrice 2x2, detta bump-environment matrix.

Esiste una matrice per ogni stage number n, in modo tale che i coefficienti

suddetti dipendono in realtà dall’indice del registro destinazione.

Si può pensare che esista un modulo esterno al pixel shader, interpellato

durante l’esecuzione dell’istruzione BEM, la cui funzione è quella di fornire i

quattro coefficienti M00(n), M10(n), M01(n), M11(n). Come vedremo nel

seguito, nel nostro progetto il modulo in questione è il blocco chiamato BEM

Module.

Osservazioni: l’istruzione BEM può essere usata una sola volta all’interno

dello shader ed inoltre essa deve comparire nella fase1. Ai fini del conteggio del

numero di istruzioni, la BEM viene considerata come 2 istruzioni aritmetiche.

Istruzione CMP - Consente di effettuare una scelta condizionata tra i

sorgenti src1 e src2 sulla base della condizione src0 >= 0. Sintassi:

cmp dest, src0, src1, src2

: il registro destinazione è un registro rn.

src0, src1, src2 : i registri sorgenti possono essere cn, rn nella fase 1;

cn, rn, vn nella fase 2.

Spiegazione: la condizione src0 >= 0 viene valutata componente per

componente; nel caso essa sia verificata si sceglie src1, altrimenti src2.

dest

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 158

Istruzione CND - Consente di effettuare una scelta condizionata tra i

sorgenti src1 e src2 sulla base della condizione src0 > 0.5. Sintassi:

cnd dest, src0, src1, src2

: il registro destinazione è un registro rn.

src0, src1, src2 : i registri sorgenti possono essere cn, rn nella fase 1;

cn, rn, vn nella fase 2.

Spiegazione: la condizione src0 > 0.5 viene valutata componente per

componente; nel caso essa sia verificata si sceglie src1, altrimenti src2.

dest

Istruzione DP3 - Calcola un prodotto scalare a 3 componenti (R, G, B) e

replica il risultato su tutti e quattro i canali. Sintassi:

dp3 dest, src0, src1

: il registro destinazione è un registro rn.

src0, src1 : i registri sorgenti possono essere cn, rn nella fase 1; cn, rn,

vn nella fase 2.

L’istruzione evidenziata sopra esegue quanto segue:

dest

dest.r = dest.g = dest.b = dest.a =

src0.r * src1.r + src0.g * src1.g + src0.b * src1.b

Istruzione DP4 - Calcola un prodotto scalare a 4 componenti (R, G, B,

A) e replica il risultato su tutti e quattro i canali. Sintassi:

dp4 dest, src0, src1

: il registro destinazione è un registro rn.

src0, src1 : i registri sorgenti possono essere cn, rn nella fase 1; cn, rn,

vn nella fase 2.

L’istruzione evidenziata sopra esegue quanto segue:

dest

dest.r = dest.g = dest.b = dest.a =

src0.r * src1.r + src0.g * src1.g +

src0.b * src1.b + src0.a * src1.a

Istruzione LRP - Esegue un’interpolazione lineare. Sintassi:

lrp dest, src0, src1, src2

: il registro destinazione è un registro rn.

src0, src1, src2 : i registri sorgenti possono essere cn, rn nella fase 1;

cn, rn, vn nella fase 2.

L’istruzione evidenziata esegue il seguente calcolo:

dest

dest = src0 * src1 + (1-src0) * src2

Istruzione MAD - Esegue una moltiplicazione seguita da una addizione.

La sintassi è la seguente:

mad dest, src0, src1, src2

: il registro destinazione è un registro rn.

src0, src1, src2 : i registri sorgenti possono essere cn, rn nella fase 1;

dest

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 159

cn, rn, vn nella fase 2.

L’istruzione evidenziata esegue il seguente calcolo:

dest = src0 * src1 + src2

Istruzione MOV - Copia il contenuto del registro sorgente nel registro

destinazione. Sintassi:

mov dest, src

: il registro destinazione è un registro rn.

src : il registro sorgente può essere cn, rn nella fase 1; cn, rn, vn nella fase

dest

2.

Istruzione MUL - Esegue la moltiplicazione componente per

componente di due registri. Sintassi:

mul dest, src0, src1

: il registro destinazione è un registro rn.

src0, src1 : i registri sorgenti possono essere cn, rn nella fase 1; cn, rn,

vn nella fase 2.

L’istruzione evidenziata esegue la seguente operazione:

dest

dest = src0 * src1

Istruzione NOP - Non esegue alcuna operazione. Sintassi:

nop

Istruzione SUB - Esegue la sottrazione componente per componente fra

due registri. Sintassi:

sub dest, src0, src1

: il registro destinazione è un registro rn.

src0, src1 : i registri sorgenti possono essere cn, rn nella fase 1; cn, rn,

vn nella fase 2.

L’istruzione evidenziata esegue la seguente operazione:

dest

dest = src0 - src1

5.5.5 Istruzioni di texture addressing

Istruzione TEXCRD - Copia il contenuto di un registro delle texture sul

registro destinazione. Sintassi:

texcrd dest, src

: il registro destinazione è un registro rn.

src : il registro sorgente è un registro tn.

Osservazione: l’istruzione in questione equivale ad una MOV da un

registro tn ad un registro rn, con la particolarità che solo le prime tre

componenti lette dal registro tn sono copiate e di conseguenza la quarta

componente del registro destinazione rimane non settata.

dest

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 160

Istruzione TEXDEPTH - Calcola una quantità, detta depth value, che verrà

usata nel test di confronto del depth buffer per il pixel corrente. Sintassi:

texdepth dest

: il registro destinazione può essere solo il registro r5.

L’istruzione evidenziata esegue quanto segue:

dest

(r5.g <> 0) =>

(r5.g = 0) =>

r5.r = r5.r / r5.g

r5.r = 1

Osservazioni: l’istruzione TEXDEPTH può essere usata solo nella fase 2.

Nella nostra implementazione del processore è presente un segnale di

uscita a 32 bit che corrisponde al contenuto del registro r5.r. Inoltre, qualora

nello shader compaia l’istruzione TEXDEPTH, la linea di uscita del Pixel Shader

chiamata PS_DepthEn viene settata ad ‘1’.

Istruzione TEXKILL - Annulla il rendering del pixel corrente se almeno

una delle prime tre componenti del registro sorgente è minore di zero. Sintassi:

texkill src

: il registro sorgente può essere rn o tn.

Osservazioni: l’istruzione TEXKILL può essere usata solo nella fase 2.

Nella nostra implementazione del processore, l’annullamento del rendering del

pixel corrente equivale a settare ad ‘1’ la linea di uscita del Pixel Shader

chiamata PS_PixelKill.

src

Istruzione TEXLD - Scrive nel registro destinazione i dati sul colore (R,

G, B, A) che si ottengono da una operazione di texture sampling. Sintassi:

texld dest, src

: il registro destinazione è un registro rn.

src : il registro sorgente può essere tn nella fase 1; rn, tn nella fase 2.

L’istruzione evidenziata opera come segue: utilizza le prime tre

componenti del registro sorgente (u, v, w) per campionare la texture il cui stage

number corrisponde all’indice del registro destinazione. La quaterna di valori

(R, G, B, A) che si ottiene come risultato viene scritta nel registro destinazione.

Osservazione: come abbiamo già avuto modo di vedere, l’operazione di

texture sampling viene eseguita da un modulo esterno al Pixel Shader che nel

nostro progetto è stato chiamato Texture Sampler.

dest

5.6. Source register selector (swizzler)

Nel paragrafo 5.4 abbiamo visto che, nel tipico flusso di esecuzione di

un’istruzione, il dato in ingresso proveniente dal registro sorgente è sottoposto

ad una successione di modificazioni o trasformazioni fino all’ottenimento del

dato finale, che viene scritto nel registro destinazione.

Nel paragrafo 5.5 abbiamo analizzato la trasformazione centrale della

catena, ovvero quella legata all’istruzione vera e propria, che può consistere in

una operazione aritmetica o di texture addressing.

In questo e nei prossimi paragrafi analizzeremo invece le modificazioni

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 161

apportate sui dati dagli altri blocchi. Cominceremo in particolare dal

componente detto swizzler.

Il source register selector (o swizzler) è un modificatore che prende in ingresso

il dato contenuto nel registro sorgente e lo modifica replicando il singolo

canale specificato su tutti e quattro i canali. L’operazione di swizzling ha la

seguente sintassi:

src.channel

: è il registro sorgente.

channel : è uno dei quattro canali r, g, b, a.

L’uso del modificatore è spiegato nella tabella seguente.

src

Source Register Selectors

Sintassi

Spiegazione

Red replicate

src.r

replica il canale rosso su tutti i canali

Green replicate

src.g

replica il canale verde su tutti i canali

Blue replicate

src.b

replica il canale blu su tutti i canali

Alpha replicate

src.a

replica il canale alfa su tutti i canali

Vediamo, con un esempio, come si utilizza il modificatore all’interno di

un’istruzione. L’istruzione

add r0, v0, v1.g

esegue la somma tra il dato contenuto nel registro v0 e il dato formato da

quattro canali tutti coincidenti con il canale g del registro v1. Per maggiore

chiarezza riscriviamo l’operazione sviluppando le singole componenti:

r0.r = v0.r + v1.g

r0.g = v0.g + v1.g

r0.b = v0.b + v1.g

r0.a = v0.a + v1.g

Osservazioni

§ Deve essere chiaro che lo swizzler usa il contenuto del registro

come dato in ingresso e dunque non provoca alcuna

modificazione del registro stesso.

§ Lo swizzling è in assoluto la prima modificazione che il dato letto

dal registro sorgente subisce nell’esecuzione di una istruzione.

§ Il modificatore in questione può essere usato soltanto all’interno

di istruzioni aritmetiche.

5.7. Source register modifier

Il source registrer modifier permette di eseguire delle semplici operazioni

matematiche sui dati a cui esso è applicato. Il modificatore in esame prende in

ingresso i dati letti dai registri sorgenti, eventualmente sottoposti a swizzling, e

fornisce in uscita i dati che saranno direttamente usati dall’istruzione.

Esistono in realtà cinque tipi diversi di modificatori, riportati nella tabella

a pagina seguente, nella quale si illustra la sintassi e il significato di ciascuno.

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 162

Source Register Modifier

Sintassi

Descrizione

Bias

src_bias

Sottrae 0.5 da tutte le componenti del registro:

output = input – 0.5

Invert

1-src

Sottrae ciascuna componente del registro

dall’unità: output = 1 - input

Negate

-src

Cambia segno a tutte le componenti del

registro: output = - input

Scalex2

src_x2

Raddoppia tutte le componenti del registro:

output = 2 * input

Signed Scaling

src_bx2

Sottrae 0.5 da ogni componente e raddoppia il

risultato: output = 2 * (input – 0.5 )

Osservazioni:

§ I modificatori descritti possono essere usati solo all’interno delle

istruzioni aritmetiche.

§ Il modificatore applicato ad un registro non ne cambia il

contenuto, ma modifica solo il dato letto.

§ I modificatori illustrati non possono essere applicati ai registri c.

§ I source register modifiers possono essere usati congiuntamente

ai source register selectors; in ogni caso la prima operazione ad

essere eseguita è quella di swizzling.

§ I cinque source register modifier illustrati possono essere

combinati tra loro. Al riguardo esistono delle restrizioni: Negate

può essere combinato con bias, scalex2 o signed scaling; quando

è combinato, negate viene eseguito per ultimo; Invert non può

essere combinato con nessun altro modificatore.

Facciamo un esempio che spieghi ulteriormente l’uso dei modificatori.

Nell’istruzione

mul r0, 1-r1.r, -r2_bx2

il modificatore invert viene applicato al registro r1, che è

preventivamente sottoposto a swizzling; al registro r2 vengono invece applicati

due modificatori: il signed scaling e l’invert. L’istruzione in questione esegue

allora i seguenti calcoli:

r0.r = (1-r1.r)*(-2*(r2.r-0.5))

r0.g = (1-r1.r)*(-2*(r2.g-0.5))

r0.b = (1-r1.r)*(-2*(r2.b-0.5))

r0.a = (1-r1.r)*(-2*(r2.a-0.5))

5.8. Instruction modifier

L’instruction modifier permette di modificare il dato proveniente

dall’esecuzione di un’istruzione prima che lo stesso venga scritto sul registro

destinazione.

La lista completa dei modificatori istruzione, con la sintassi e la relativa

spiegazione, è mostrata nella tabella a pagina seguente.

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 163

Instruction

Modifier

Sintassi*

Descrizione

_x2

instr_x2

Moltiplica per 2 il risultato dell’istruzione

_x4

instr_x4

Moltiplica per 4 il risultato dell’istruzione

_x8

instr_x8

Moltiplica per 8 il risultato dell’istruzione

_d2

instr_d2

Divide per 2 il risultato dell’istruzione

_d4

instr_d4

Divide per 4 il risultato dell’istruzione

_d8

instr_d8

Divide per 8 il risultato dell’istruzione

_sat

instr_sat

Satura il risultato dell’istruzione, eseguendo il clamping51 tra

0e1

(*) instr è l’identificativo dell’istruzione (es. add).

Osservazioni

Gli instruction modifiers possono essere usati soltanto all’interno di

istruzioni aritmetiche.

Il modificatore _sat può essere combinato con uno degli altri, in tal caso

viene eseguito per secondo.

Esempio:

add_x2_sat r0, v0, v1

L’istruzione appena scritta viene eseguita tramite la successione dei

seguenti passi:

§ prima di tutto vengono sommati tra loro i contenuti dei registri

sorgenti v0 e v1

§ la somma così ottenuta viene moltiplicata per 2 (modificatore

_x2)

§ il risultato del passo precedente subisce il modificatore _sat,

ovvero ciascuna delle quattro componenti viene sottoposta al

clamping tra 0 e 1.

5.9. Destination register write mask

Con l’espressione destination register write mask si indica la maschera usata

per controllare quali canali (R, G, B, A) del registro destinazione vengono

scritti dall’istruzione.

L’insieme delle maschere permesse è riportato nella tabella a pagina

seguente.

51

Con il termine clamping si indica la seguente operazione espressa in metalinguaggio:

if ( input < 0 ) then

output = 0

elseif ( input > 1 ) then

output = 1

else

output = input

end if

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 164

Write Mask

Sintassi

Descrizione

red, green,

blue, alpha

dest.rgba

Tutti i canali del registro destinazione sono scritti

none

dest

Come sopra

color

dest.rgb

Vengono scritti i canali (R, G, B) del registro destinazione

alpha

dest.a

Viene scritto solo il canale (A) del registro destinazione

red

dest.r

Viene scritto solo il canale (R) del registro destinazione

green

dest.g

Viene scritto solo il canale (G) del registro destinazione

blue

dest.b

Viene scritto solo il canale (B) del registro destinazione

arbitrary

(*)

(*)

(*) La maschera arbitrary è una qualunque combinazione di canali, elencati però nell’ordine r, g,

b, a. Ad esempio, con la maschera dest.rba vengono aggiornati i canali red, blue e alpha

del registro destinazione.

Osservazione

Le destination register write mask riportate sopra sono usate all’interno

di istruzioni aritmetiche.

5.10. Modificatori e maschere per le istruzioni TEXLD e TEXCRD

I modificatori e le maschere di cui ci siamo occupati nei precedenti

paragrafi sono utilizzabili, come detto, solo all’interno di istruzioni aritmetiche.

In realtà esistono due istruzioni di texture addressing, TEXLD e TEXCRD, che

supportano un proprio insieme di maschere e modificatori; tali argomenti sono

l’oggetto del presente paragrafo.

5.10.1 Source register selectors

Gli swizzlers utilizzabili con le istruzioni

nella seguente tabella.

TEXLD

Swizzler

Sintassi

Spiegazione

rgb

src.rgb

Fornisce il dato (R, G, B, B)

rga

src.rga

Fornisce il dato (R, G, A, A)

e TEXCRD sono riportati

Osservazione

Le due istruzioni di texture addressing prese in considerazione non

leggono mai più di tre componenti dal registro sorgente; i modificatori .rgb e

.rga forniscono l’opzione di prendere, quale terza componente letta, il canale

blue o il canale alpha del registro sorgente.

5.10.2 Source register modifiers

Riportiamo nella tabella a pagina seguente i source register modifiers

utilizzabili con le istruzioni TEXLD e TEXCRD.

Progettazione in VHDL del Pixel Shader v 1.4

Source

Register

Modifier

_db

Sintassi

src_db

_da

src_da

Pag. 165

Descrizione*

r'

g'

b'

a'

r'

g'

b'

=

=

è

è

=

=

è

r/b (r' = 1.0

g/b (g' = 1.0

indefinito

indefinito

r/a (r' = 1.0

g/a (g' = 1.0

indefinito

se b = 0)

se b = 0)

se a = 0)

se a = 0)

a' è indefinito

(*) (r, g, b, a)= componenti in ingresso;(r', g', b', a')= componenti in

uscita.

5.10.3 Destination register write mask

Per l’istruzione TEXLD si rende necessario l’uso della maschera .rgba.

Con l’istruzione TEXCRD si possono usare solo le maschere .rgb o .rg.

Terminiamo qui la spiegazione delle peculiarità delle istruzioni TEXLD e

TEXCRD, rimandando alla documentazione Microsoft per ulteriori dettagli.

5.11. Instruction pairing

Come già accennato, all’interno del Pixel Shader vi sono due pipeline che

operano in parallelo: la vector pipeline, che elabora i canali (R, G, B), e la scalar

pipeline, responsabile dell’elaborazione del canale (A). Come conseguenza, il

Pixel Shader è potenzialmente capace di eseguire contemporaneamente due

istruzioni aritmetiche, una sulla color pipe e l’altra sull’alpha pipe; in tal caso si

parla di instruction pairing.

La possibilità di esecuzione contemporanea di due istruzioni è soggetta a

determinati vincoli.

Innanzitutto le istruzioni che possono andare in pairing sono solo una

sottoclasse delle istruzioni aritmetiche e più esattamente: ADD, CMP, CND, DP3,

LRP, MAD, MOV, MUL, SUB.

In secondo luogo occorre specificare, mediante la destination register write

mask, la modalità con la quale le due istruzioni occupano le pipeline:

l’istruzione che usa la vector pipeline deve avere la maschera .rgb, quella che

usa la scalar pipeline deve avere la maschera .a. L’istruzione DP3, usando la

color pipe, deve necessariamente avere la maschera .rgb associata al registro

destinazione.

Infine, il pairing viene esplicitamente indicato nello shader facendo

precedere la seconda istruzione della coppia dal segno più (+).

Esempio: il codice

mul r0.rgb, t0, v0

+ add r1.a, r1, c2

permette di eseguire una moltiplicazione dei canali (R, G, B) e una

contemporanea somma dei canali (A); si noti che sia i registri sorgenti che

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 166

quelli destinazione delle due istruzioni in pairing possono essere differenti.

Facciamo ora un esempio con l’istruzione DP3:

dp3 r0.rgb, t0, v0

+ mul r0.a, r1, c2

Il prodotto scalare viene eseguito nella vector pipeline

contemporaneamente, la scalar pipeline esegue una moltiplicazione.

e,

5.12. Pixel Shader Assembler

A questo punto della trattazione abbiamo una panoramica completa

dello shader 1.4 e possiamo affermare di conoscere tutte le istruzioni e le

operazioni di base che il Pixel Shader deve saper svolgere. Le specifiche sul

funzionamento del nostro processore non sono tuttavia ancora esaurite:

l’Instruction Pool non può infatti essere caricato direttamente con lo shader in

formato testo, ma ovviamente richiede un flusso di dati in formato binario,

ottenuti dalla compilazione del codice sorgente. Si osservi a tal proposito lo

schema sottostante.

shader

(file .txt)

PIXEL

SHADER

ASSEMBLER

file

assemblato

(file .pso)

INSTRUCTION

POOL

...

Lo shader in formato testo viene passato al Pixel Shader Assembler,

un’utilità presente all’interno di Microsoft DirectX 8.1 SDK che assembla il

sorgente producendo un file binario con estensione .pso. Tale file, visto come

una successione di dati a 32 bit, viene passato in ingresso al Pixel Shader, che lo

memorizza all’interno dell’Instruction Pool per poi successivamente eseguirlo.

Ciò che vogliamo fare in questo paragrafo è spiegare la struttura del file

.pso, ovvero capire come il Pixel Shader Assembler codifica la sequenza di

istruzioni che compongono lo shader.

5.12.1 Struttura di un file .pso

Il seguente comando MS-DOS

psa -0 shader.txt

permette di assemblare il file sorgente “shader.txt”, ottenendo come

risultato il file denominato “shader.pso”. L’opzione -0 dell’assemblatore serve

ad evitare che nel file generato vengano inserite informazioni di debug.

Un file .pso è una sequenza di DWORD (gruppi di 4 byte, cioè 32 bit)

organizzata come mostrato nello schema all’inizio di pagina seguente.

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 167

Inizio shader: FF FF 01 04

10 dword con informazioni di servizio

istruzioni DEF (6 dword ciascuna)

sequenza istruzioni

Fine shader: 00 00 FF FF

La prima dword è la codifica dell’istruzione che specifica la versione dello

shader:

ps.1.4

Tale istruzione viene appunto tradotta nella sequenza FF FF 01 04.

Osservazione - Per chiarezza, indicheremo sempre ciascuna dword

come una sequenza di 4 byte, ordinati dal più significativo al meno

significativo. A sua volta, ciascun byte viene rappresentato come una coppia di

cifre esadecimali.

Dopo la dword di inizio shader ci sono 10 dword che portano

informazioni sulla versione dell’assemblatore e che devono essere separate dai

dati destinati all’Instruction Pool.

Seguono le istruzioni di definizione delle costanti, disposte in sequenza e

senza separatori. Ciascuna istruzione DEF viene così codificata:

00 00 00 51

dest

fval1

fval2

fval3

fval4

dove la prima dword rappresenta l’identificativo dell’istruzione stessa, la

seconda dword codifica il registro di destinazione e fval1, fval2, fval3, fval4

sono le codifiche in formato floating-point delle costanti che compaiono

nell’istruzione.

Il blocco che nello schema è indicato come “sequenza istruzioni”

rappresenta la codifica di tutte le istruzioni rimanenti che compaiono nello

shader: queste sono le istruzioni di texture addressing, le istruzioni aritmetiche e il

phase marker. Il modo in cui tali istruzioni sono codificate verrà spiegato tra

breve.

L’ultima dword è quella di fine shader: 00 00 FF FF.

5.12.2 Codifica delle istruzioni

Ogni istruzione che compare nello shader (esclusa la DEF, che è stata già

analizzata) viene codificata come una sequenza di dword così composta:

§ la prima dword è l’identificativo dell’istruzione

§ segue un insieme di dword, una per ogni registro destinazione o

sorgente, disposte nello stesso ordine con cui compaiono nello

shader.

Ad esempio, l’istruzione

add dest, src0, src1

viene tradotta in una sequenza di 4 dword che sono nell’ordine: il codice

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 168

operativo della ADD, la codifica del registro dest, la codifica del registro src0, la

codifica del registro src1.

5.12.3 OpCode

Vediamo in dettaglio la composizione di un codice operativo (OpCode)

di un’istruzione. Esso è una sequenza di 32 bit organizzati come segue.

31

24 23

16 15

8 7

0

0 p 0 0 0 0 0 0 0 0 0 0 0 0 0 0

La parte significativa dell’OpCode dell’istruzione è racchiusa nei bit che

vanno da 15 a 0. Forniamo qui di seguito l’elenco completo delle istruzioni

dello shader con associati i 16 bit meno significativi dell’OpCode.

Instr.

OpCode Instr.

OpCode

add

00 02

mov

00 01

bem

00 59

mul

00 05

cmp

00 58

nop

00 00

cnd

00 50

phase

ff fd

def

00 51

sub

00 03

dp3

00 08

texcrd

00 40

dp4

00 09

texdepth

00 57

lrp

00 12

texkill

00 41

mad

00 04

texld

00 42

Il bit 30, identificato in figura dal simbolo p, è il bit di pairing. Il valore che

tale bit assume nei diversi casi è ricavabile dalla seguente tabella.

Tipo Istruzione

Pairing

Bit

Istruzione Singola

0

Pairing

Prima Istruzione

0

Seconda Istruzione

1

In sostanza il bit di pairing assume il valore ‘1’ solo nell’OpCode della

seconda istruzione della coppia in pairing (cioè l’istruzione che nello shader è

preceduta dal simbolo +).

5.12.4 Codifica dei registri

Esistono due codifiche differenti per i registri: una applicata al registro

che segue immediatamente l’OpCode dell’istruzione, l’altra per tutti gli

eventuali registri presenti nell’istruzione. Analizziamo qui di seguito entrambe.

La dword che segue l’OpCode dell’istruzione rappresenta, nella maggior

parte dei casi, il registro destinazione e risulta così composta:

Progettazione in VHDL del Pixel Shader v 1.4

31

28 27

Pag. 169

24 23

20 19

0 0 0

identif.

registro

16 15

8 7

0

A B GR 0 0 0 0 0 0 0 0

modif.

sat write mask

indice registro

Analizziamo i singoli gruppi di bit evidenziati nel disegno.

I 4 bit più significativi, da 31 a 28, sono l’identificativo del registro. Si

veda al proposito la seguente tabella.

Identif.

registro

Codifica

binaria

Codifica

esadecimale

r

1000

8

v

1001

9

c

1010

A

t

1011

B

I bit dal 27 al 24 codificano l’instruction modifier secondo la tabella qui

sotto riportata.

Instr.

modif.

Codifica

binaria

Codifica

esadecimale

none

0000

0

_x2

0001

1

_x4

0010

2

_x8

0011

3

_d8

1101

D

_d4

1110

E

_d2

1111

F

Il bit 20 è il bit di saturazione, ovvero se pari ad ‘1’ indica la presenza del

modificatore _sat.

I bit dal 19 al 16 rappresentano la write mask per i canali A, B, G, R. Il

valore ‘1’ associato ad un certo canale indica che quella componente del

registro destinazione viene scritta dall’istruzione.

I bit da 7 a 0 sono la codifica binaria dell’indice del registro.

Per gli ulteriori registri che compaiono all’interno dell’istruzione viene

adottata una codifica diversa, illustrata nel disegno sottostante.

31

28 27

24 23

20 19

16 15

8 7

0

0 0 0 0 0 0 0 0

identif.

registro

modif.

A

B

G

R

indice registro

Per i bit da 31 a 28 valgono le stesse considerazioni fatte sopra.

I bit da 27 a 24 codificano il source modifier secondo la tabella mostrata

a pagina seguente.

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 170

Source

modif.

Codifica

binaria

Codifica

esadecimale

none

0000

0

negate

0001

1

bias

bias,

negate

0010

2

0011

3

bx2

bx2,

negate

0100

4

0101

5

invert

0110

6

x2

x2,

negate

0111

7

1000

8

db

1001

A

da

1010

B

I bit dal 23 al 16 sono relativi al source register selector: per ciascuno dei

quattro canali A, B, G, R, una coppia di bit indica da quale canale originario

viene prelevato il dato. In merito esiste la convenzione mostrata nella tabella

sottostante.

Canale

sorgente

codifica

R

00

G

01

B

10

A

11

Infine i bit da 7 a 0 sono la codifica binaria dell’indice del registro.

5.13. Strumenti software utilizzati nel progetto

Riportiamo nella tabella che segue l’elenco dei tool utilizzati per la

realizzazione del Pixel Shader, unitamente ai siti da cui essi sono prelevabili.

Software (casa produttrice)

Utilizzo

Sito web

HDL designer pro (Mentor Graphics)

Progettazione VHDL

www.mentor.com

Modelsim (Mentor Graphics)

Compilatore e simulatore VHDL

www.mentor.com

VHDL Simili (Symphony EDA)

Compilatore e simulatore VHDL

www.symphonyeda.com

WaveViewer (SynaptiCAD)

Visualizzatore di forme d’onda

www.synapticad.com

Microsoft DirectX 8.1 SDK Pixel Shader Assemblatore

Assembler

www.microsoft.com

www.msdn.microsoft.com

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 171

5.14. Organizzazione del progetto

Prima di procedere all’analisi dell’implementazione del Pixel Shader è

opportuno presentare l’organizzazione logica che si è deciso di dare al

progetto.

In fase di implementazione si è deciso di separare il progetto in tre

librerie distinte a seconda delle funzionalità dei singoli blocchi componenti.

•

Utilities: contiene al suo interno i packages relativi alla definizione dei tipi

di dati utilizzati nel progetto, delle funzioni di supporto per la conversione

da un tipo di dato all’altro e per l’accesso ai file. Contiene inoltre opportuni

packages che si occupano di definire le costanti utilizzate per indicare i

codici operativi del Pixel Shader e delle ALU. Di questa libreria fanno

inoltre parte le versioni parametriche dei componenti elementari necessari

allo sviluppo (quali ad esempio i multiplexer ed i demultiplexer).

•

PixelShader: in questa libreria sono contenute tutte le entità strettamente

pertinenti al Pixel Shader, nonché la struttura complessiva del processore

realizzata mediante wiring dei singoli blocchi componenti.

•

PixelShader_TestBench: come si evince dal nome, in questa libreria

vengono raggruppati tutti gli elementi che fanno parte del banco di prova:

Test Unit, Texture Sampler, BEMModule e la struttura che li collega al

Pixel Shader.

•

Stddevelopers_kit: di questa libreria fornita con il ModelSim è necessario

ricompilare, per il nuovo simulatore, i sorgenti relativi alle funzioni di

accesso ai file; i sorgenti completi per questa ed altre librerie standard ieee

sono fortunatamente disponibili nella directory “/vhdl_src/” contenuta

nella directory di installazione del ModelSim.

I sorgenti acclusi al presente volume sono quindi organizzati secondo le

categorie appena indicate; la stessa suddivisione viene mantenuta anche

nell’appendice in cui vengono riportati i sorgenti completi realizzati per la

sintesi del Pixel Shader.

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 172

Capitolo 6. Test bench per la simulazione in VHDL del processore

6.1. Introduzione

Prima di procedere all’analisi del Pixel Shader vero e proprio,

descrivendone i passi fondamentali per lo sviluppo e la realizzazione, è

opportuno presentare il test bench (o banco di prova) nella sua totalità. In

questo modo si potrà meglio comprendere la logica di funzionamento del

processore oggetto della presente tesina.

Come ulteriore premessa si fa notare che eventuali tipi di dato che non

appartengono allo standard del VHDL vengono definiti nella libreria

Utilities.PS_Types allegata al progetto; i file sorgenti di questa libreria

(PS_Types_pkg.vhd e PS_Types_pkg_body.vhd) possono essere consultati in

appendice e nel progetto accluso.

Il test bench si compone di cinque blocchi fondamentali: un generatore

di clock (Clock Generator), una unità che si occupa di reperire un’opportuna

matrice di dati dalla memoria di sistema (il BEM Module), una unità che esegue

il Texture Sampling (Texture Sampler), il Pixel Shader vero e proprio (il

processore oggetto della prova) ed infine la Test Unit (un modulo che si

occupa di pilotare adeguatamente il Pixel Shader).

Nello schema a pagina seguente sono visibili le unità funzionali sopra

elencate, le rispettive linee di collegamento e scambio dati ed i segnali per

l’handshaking.

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 173

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 174

6.2. Clock Generator

Per facilitare una eventuale estensione del progetto è stata prevista la

possibilità di utilizzare un clock bifase, tuttavia, per questioni di comodità, allo

stato attuale è stata utilizzata una sola fase.

La schematizzazione mediante VHDL è banale: si è fatto ricorso ad un

processo che generi il segnale di clock per entrambe le fasi e a due

assegnamenti concorrenti al processo stesso per riportare il segnale generato

alle due uscite del blocco. Occorre prestare attenzione al fatto che il clock

viene descritto in termini di ampiezza dell’impulso per la fase 1 e di

separazione tra quest’ultimo e l’inizio del fronte di salita per la fase 2.

Di seguito viene presentato il codice utilizzato

ENTITY ClkGen IS

GENERIC(

PulseWidth

: TIME := 10 NS;

PulseSeparation : TIME := 2 NS

);

PORT(

ClkGen_clk1 : OUT

bit;

-- clock fase 1

ClkGen_clk2 : OUT

bit

-- clock fase 1

);

--due segnali di supporto

SIGNAL clk1 : BIT := '0';

SIGNAL clk2 : BIT := '1';

END ClkGen ;

ARCHITECTURE ClkGen2 OF ClkGen IS

CONSTANT clock_period : TIME := 2*(PulseWidth+PulseSeparation);

BEGIN

clock_driver: PROCESS

BEGIN

clk1 <= '0', '1' AFTER PulseWidth+PulseSeparation;

clk2 <= '1', '0' AFTER PulseWidth, '1' AFTER

2*PulseWidth+PulseSeparation;

WAIT FOR clock_period;

END PROCESS clock_driver;

ClkGen_clk1 <= clk1;

ClkGen_clk2 <= clk2;

END ClkGen2;

Data la semplicità dell’entità in esame se ne è riportato integralmente il

codice realizzativo; per entità più complesse verranno riportati solo alcune parti

essenziali del relativo sorgente, tenendo presente che le versioni complete dei

listati di implementazione possono essere consultate nella relativa appendice e

nei sorgenti acclusi.

6.3. Texture Sampler

Sampler_En

Sampler_TextureStageNumber : (2:0)

Sampler_Data : (127:0)

(OTHERS => '0')

PixelShader_TestBench

Sampler

Sampler_Done

TEXSAMPLER

Il Texture Sampler è il blocco che dovrebbe simulare

le operazioni di Texture Sampling tipiche delle moderne

schede grafiche (nella presente tesina lo scopo del progetto

è la realizzazione del Pixel Shader e non delle unità di

sampling, per cui questa entità restituisce valori fittizi).

Il funzionamento del Texture Sampler può essere

schematizzato come segue. Il Sampler preleva da un

apposito bus i dati relativi alla coordinata necessaria per il

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 175

campionamento della Texture; sulla base delle coordinate ottenute preleva i

dati della texture corrispondente dalla memoria e li sottopone ad eventuali

operazioni di filtraggio (es. bilinear o trilinear filtering); al termine restituisce

sullo stesso bus i valori R, G, B, A calcolati.

Il Texture Sampler è quindi caratterizzato dai seguenti segnali di

controllo:

•

un segnale di abilitazione (Sampler_En) che indica all’unità il fatto che sul

bus in ingresso sono presenti dati validi per le coordinate e che

l’elaborazione può iniziare

•

un segnale di selezione del Texture Stage52

•

una porta di ingresso/uscita direttamente connessa al bus dati

(Sampler_Data) per lo scambio di informazioni

•

un segnale che indichi quando l’elaborazione è terminata (Sampler_Done).

La logica di funzionamento è molto semplice e si basa su un classico

meccanismo di handshaking: il Pixel Shader si occupa di fornire i dati corretti

sul data bus e di specificare il Texture Stage Number per indicare quale texture

andare a campionare; quando questi dati risultano corretti il Pixel Shader invia

il segnale di abilitazione al Sampler. Il Sampler è ovviamente dotato al suo

interno di una serie di latch per poter mantenere stabili i dati in ingresso, dato

che il Pixel Shader, dopo un tempo predeterminato, libera il bus in attesa del

risultato dell’elaborazione.

Il segnale di abilitazione viene mantenuto alto fino a che il Sampler non

risponde mandando a sua volta alto il proprio segnale di “done”. A questo

punto il Pixel Shader memorizza internamente le quattro dword del risultato e

di seguito spegne il Sampler abbassando il segnale di enable; in questo modo il

Sampler viene informato del fatto che il risultato è stato correttamente

memorizzato e libera a sua volta il bus dati.

Illustriamo quanto ora esposto facendo ricorso alle forme d’onda

risultato della semplice simulazione dello shader:

ps.1.4

texld r0, t0

avente come ingresso per il file delle texture i seguenti valori:

0 0.1 0.2 0.3 0.0

1 0.0 0.0 0.3 0.0

3 1.0 0.0 0.2 0.0

9 0.0 0.0 0.0 0.0

In sostanza vengono passati al Sampler, come coordinate su cui

campionare la texture, i valori (0.1; 0.2; 0.3).

Analizzando i segnali di interesse abbiamo:

52

Possono infatti venire caricate nella memoria video o di sistema fino ad un massimo di 6 texture distinte gestibili dall’hardware per

la geometria corrente; ogni texture appartiene ad uno stage differente, identificato da un indice progressivo.

Progettazione in VHDL del Pixel Shader v 1.4

Coordinate a cui

campionare la

texture

Pag. 176

Risultato delle operazioni

svolte dal Texture

Sampler

In questa sezione vediamo rappresentato lo stato di esecuzione delle

istruzioni del Pixel Shader (ps_mode = 3, “11” in codifica binaria).

All’inizio dell’esecuzione il bus è libero (ovvero è caratterizzato da una

sequenza di ‘0’); a 336 ns il Pixel Shader immette sul DataBus la codifica in

formato floating-point corrispondente alla quaterna di dword presenti nel

registro t0; il TextureStageNumber non subisce variazioni (in quanto l’indice

relativo è sempre 0).

In seguito (345 ns) viene attivato il Sampler e all’istante corrispondente ai

355 ns viene liberato il bus dati; si passa quindi all’attesa del termine di

elaborazione che avviene quando il Sampler manda ad ‘1’ il segnale

Sampler_done (445 ns) ed immette nel DataBus i valori risultato

dell’elaborazione.

Il Pixel Shader scrive questi valori sul registro indicato e di seguito

spegne il Texture Sampler (455 ns), di conseguenza anche il segnale di done del

Sampler si abbassa.

Per brevità di trattazione non viene riportato il codice VHDL che può

comunque essere consultato in appendice.

6.4. BEM Module

Il BEM Module si occupa di reperire dalla memoria di

sistema una matrice di valori, precedentemente memorizzata

BEMModule_TextureStageNumber : (2:0)

dal programmatore mediante opportune istruzioni esterne al

PixelShader_TestBench

Pixel Shader. La matrice è costituita da quattro dword53 e

BEMModule

viene utilizzata in una particolare istruzione dello shader

BEM

BEMModule_Done

(l’istruzione BEM, da qui il nome del modulo) per simulare

BEMModule_Data : (127:0)

effetti di Environmental Mapping.

Questo modulo è puramente fittizio ed è stato

realizzato allo scopo di fornire dei valori di prova al Pixel Shader quando questi

vengono richiesti dall’istruzione BEM.

Il meccanismo di comunicazione tra Pixel Shader e BEM Module è

analogo a quello indicato per il Texture Sampler.

Anche per il BEM Module non viene riportata la realizzazione VHDL

comunque consultabile in appendice.

BEMModule_En

53

E’ possibile memorizzare una matrice per ogni stage di texture; il TextureStateNumber serve ad indicare quale quaterna di valori si

vuole reperire.

Pag. 177

_

T

Progettazione in VHDL del Pixel Shader v 1.4

6.5. Pixel Shader

S

O

Per il momento possiamo considerare il Pixel Shader come una unità

funzionale descritta a livello comportamentale, rimandando al capitolo

seguente la illustrazione della sua architettura interna.

In questa sezione verrà fornita una spiegazione completa del

funzionamento del complesso Pixel Shader – Test Unit e della modalità di

interazione tra il processore e il resto dell’hardware della scheda grafica.

Verranno inoltre illustrati i segnali di ingresso ed uscita e fornite le relative

tabelle necessarie ad interpretarne il significato.

PS_Mode : (1:0)

PS_Done

PS_DestAddr : (6:0)

PS_SamplerEn

PS_DestReg

PS_BEMEn

P

(

PS_WriteEn

PS_SamplerDone

PS_TextureStageNumber : (2:0)

PS_BEMDone

PS_Clk1

PS_clk2

PS_R0 : (127:0)

PixelShader

PS

PSHADER

PS_R5R : (31:0)

PS_DepthEn

PS_Dump

PS_PixelKill

Poiché stiamo parlando di un processore completo che deve gestire fasi

di caricamento delle istruzioni, di caricamento dei dati relativi ai pixel su cui

operare e di esecuzione del microcodice, si è pensato di organizzarne il

funzionamento in quatto fasi (o modi di funzionamento) distinte54.

Nella tabella seguente viene presentata la codifica ed il significato di ogni

fase.

Codifica

00

01

10

11

Denominazione

WaitingCommand

LoadShader

LoadPixel

Execute

Descrizione

Stato di attesa / Stato iniziale dello Shader

Caricamento delle istruzioni e delle costanti

Caricamento dei dati relativi al pixel da elaborare

Esecuzione delle istruzioni dello shader per il pixel corrente

Nello schema successivo vengono indicate le condizioni sotto cui è

consentito il passaggio da un modo di funzionamento all’altro del Pixel Shader.

PSMode=10

WAITING

WAITING

COMMAND

COMMAND

00

00

PSMode=01

PSMode=10

LOAD

LOAD

SHADER

SHADER

01

01

PSMode=11

LOAD

LOAD

PIXEL

PIXEL

EXECUTE

EXECUTE

10

10

more pixels

no more pixels

54

Si rende quindi necessaria la presenza di appositi segnali che consentano al resto della scheda di impostare il corretto modo di

funzionamento in base alla situazione (segnali PS_Mode).

11

11

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 178

Di seguito indichiamo tutti i segnali del Pixel Shader, distinguendo tra

segnali di ingresso, ingresso/uscita, uscita.

I segnali di ingresso sono i seguenti:

•

PS_Mode: setta il modo corrente di funzionamento del processore (in

riferimento a quanto detto sopra).

•

PS_DestAddr: indirizzo in cui scrivere il dato presente sul DataBus;

occorre prestare attenzione al fatto che i vari registri presenti all’interno del

Pixel Shader hanno range differenti tra loro. Si è adottata una normale

codifica binaria senza segno.

•

PS_DestReg: la presenza di questo segnale è necessaria per discriminare in

quale dei registri di destinazione si intende scrivere il dato in ingresso.

Questo bit assume differenti significati a seconda dello stato di

funzionamento dello Shader (fare riferimento alla tabella).

Codifica

0

1

PS_Mode

LoadShader

LoadPixel

LoadShader

LoadPixel

Destinazione

registri C

registri V

Instruction Pool

registri T

•

PS_WriteEn: segnale di abilitazione per la scrittura sui registri dei dati

presenti sul DataBus; deve essere inviato al Pixel Shader una volta che si è

certi della validità dei dati, dell’indirizzo e del valore di PS_DestReg.

•

PS_SamplerDone: indica il termine dell’elaborazione da parte del Texture

Sampler.

•

PS_BEMDone: indica il termine dell’elaborazione da parte del BEM

Module.

•

PS_Clk1: Clock, fase 1.

•

PS_Clk2: Clock, fase 2 (non utilizzato nell’implementazione corrente).

•

PS_Dump: segnale di debug. Indica di effettuare il dump su file del

contenuto dei registri. Valido solo a livello di progettazione e da escludere

in fase realizzativa.

Esiste un solo segnale di ingresso/uscita:

•

PS_Data: la linea di connessione con il bus dati esterno.

I segnali di uscita sono i seguenti:

•

PS_Done: indica il termine dell’elaborazione del pixel corrente o

l’avvenuta scrittura del dato in ingresso secondo la seguente tabella.

Evento

PS_Mode

Descrizione

LoadShader/LoadPixel Termine del caricamento dei dati presenti sul bus

Execute

Termine dell’elaborazione del pixel corrente

•

PS_SamplerEn: segnale di abilitazione per il Texture Sampler. Anche in

questo caso verificare che i dati da inviare al Sampler siano validi prima di

attivare l’unità.

•

PS_BEMEn: segnale di abilitazione per il BEM Module, valgono le

precauzioni indicate per il Sampler.

•

PS_TextureStageNumber: fare riferimento a quanto detto a proposito di

Pag. 179

t

t

Progettazione in VHDL del Pixel Shader v 1.4

Texture Sampler e BEM Module.

PS_R0: codifica RGBA del colore in uscita per il pixel corrente. È il

risultato vero e proprio dell’elaborazione delle istruzioni dello shader.

•

PS_R5R: valore da sostituire nel depth-buffer ottenuto in seguito ad una

chiamata all’istruzione TEXDEPTH.

•

PS_DepthEn: indica se utilizzare o meno il valore in uscita da PS_R5R

per effettuare il depth test situato più avanti nella pipeline grafica. Se il

valore è ‘1’ si deve utilizzare il risultato fornito dallo shader.

•

PS_PixelKill: indica la necessità di annullare il rendering del pixel corrente

in seguito ad una istruzione TEXKILL. Il Pixel Shader informa di questa

necessità il resto dell’hardware, che deve quindi provvedere ad iniziare

immediatamente l’elaborazione del pixel successivo senza inviare i dati

elaborati per il pixel eliminato al resto della pipeline.

e

e

s

s

•

6.6. Test Unit

E’ il cuore vero e proprio del test bench: suo è il compito di gestire

il

Pixel

Shader, fornendogli correttamente i dati, e di interpretarne

TestUnit_DestReg

TestUnit_WriteEn

adeguatamente le risposte, evidenziando eventuali problematiche di

progettazione.

PixelShader_TestBench

TestUnit

Non è necessario soffermarsi su una descrizione degli ingressi e

TU

TestUnit_Dump

delle uscite perché sono essenzialmente gli stessi del Pixel Shader; ad

TestUnit_Clk1

eccezione del clock, un ingresso per lo shader corrisponde ad una uscita

della Test Unit e vice versa.

Occorre tuttavia puntualizzare che la Test Unit preleva i dati da fornire al

Pixel Shader da una serie di file. Per un corretto funzionamento si consiglia di

creare la directory “C:\PSDATA” in cui andranno inseriti i file di input ed in

cui saranno generati i file di output e di report.

I file necessari ad una corretta simulazione sono i seguenti:

TestUnit_PSMode : (1:0)

T

T

TestUnit_DestAddr : (6:0)

PS_DepthEn

PS_PixelKill

PS_R0 : (127:0)

PS_R5R : (31:0)

•

PS.PSO – file binario, risultato della compilazione delle istruzioni dello

shader effettuata mediante l’assemblatore standard (psa.exe) fornito con il

Microsoft DirectX 8.1 SDK. Questo file andrà generato con il parametro

“-0” in modo da non includervi informazioni di debug (che avrebbero

complicato in modo inutile la routine di caricamento dei dati

nell’Instruction Pool del Pixel Shader).

•

C.TXT – file di testo che indica quali dati caricare nel banco costanti e in

quale indirizzo.

Il formato di questo file è il seguente:

N F.F F.F F.F F.F

•

•

N: numero intero compreso tra 0 e 7, indica il rispettivo

banco costanti da caricare.

F.F: un valore floating-point (attenzione : il VHDL non è

così flessibile come altri linguaggi di programmazione per

cui se le routine di input si aspettano un numero in

formato floating-point non possiamo specificare ad esempio

1, ma dobbiamo fornirlo con la notazione 1.0)

Esempio (questo file carica i banchi costanti 0 e 2, lasciando

non inizializzati gli altri):

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 180

0 1.0 1.1 1.2 1.3

2 0.1 0.2 0.3 0.4

•

V.TXT – file di testo che indica quali dati caricare nei registri colore e in

quale indirizzo.

•

T.TXT – file di testo che indica quali dati caricare nei registri relativi alle

coordinate delle texture e in quale indirizzo.

Il formato di questi due file è il seguente:

N F.F F.F F.F F.F

•

•

•

•

N: numero intero compreso tra 0 e 1 per i registri V, tra 0 e

5 per i registri T; il termine dei dati relativi ad un pixel

si indica inserendo come indice dei dati successivi il numero

9. In questo modo è possibile fornire dati relativi a più

pixel in sequenza.

F.F: un valore floating-point (attenzione : il VHDL non è

così flessibile come altri linguaggi di programmazione per

cui se le routine di input si aspettano un numero in formato

floating-point non possiamo specificare ad esempio 1, ma

dobbiamo fornirlo con la notazione 1.0). In corrispondenza

dell’indice di fine pixel introdurremo sempre la quaterna di

dati “9.9 9.9 9.9 9.9”.

Per quanto riguarda i dati sulle texture, sebbene al massimo

sia significativa una terna di valori (coordinate di texture

cubica), occorre comunque fornirne quattro (per via delle

funzioni di lettura dati); il quarto valore non verrà

comunque considerato.

Per ogni pixel che si intende far elaborare è necessario

fornire le informazioni sul colore, seguite dall’indice di

fine pixel; a queste devono corrispondere necessariamente

delle informazioni sulle texture. Qualora queste ultime non

siano necessarie si deve comunque riportare l’indice di fine

dati anche per le texture.

Esempio (al primo pixel sono associati dati colore e texture,

al secondo solo dati colore):

V.TXT 0 0.1 0.2 0.3 0.4

1 1.0 1.0 1.0 1.0

9 9.9 9.9 9.9 9.9

0 0.3 0.2 0.1 0.4

9 9.9 9.9 9.9 9.9

Primo pixel con

associate coordinate di

texture

Secondo pixel senza

T.TXT 0 0.1 0.2 0.0 0.0

coordinate di texture

9 9.9 9.9 9.9 9.9

associate

9 9.9 9.9 9.9 9.9

Tutte le funzioni necessarie alla lettura ed alla scrittura di file di testo e

binari, nel formato qui presentato, sono le seguenti:

•

ReadDword, Read4Dword: per la lettura di file binari

•

ReadData: per la lettura dei file di testo

•

WriteString: per la scrittura di una stringa su file di testo

•

WriteBit: per la scrittura di un singolo bit su file di testo

•

WriteDword, Write4DwordCol, Write4DwordRow: per la scrittura di dati

in formato floating-point su file di testo

Progettazione in VHDL del Pixel Shader v 1.4

Pag. 181

•

Write4DwordHex: per la scrittura di 4 dword in formato esadecimale su

file di testo.

Per analizzarne i sorgenti fare riferimento alla libreria Utilities.File_IO ed

ai file di implementazione (file_io_pkg.vhd e file_io_pkg_body.vhd) riportati in

appendice.

Torniamo all’implementazione della Test Unit. Trattandosi

essenzialmente di una unità di controllo, si è scelto di realizzarla mediante una

macchina a stati finiti, sincrona con il clock fase 1. A differenza dell’unità di

controllo del Pixel Shader, sensibile ai fronti di salita del clock, la Test Unit

effettua le transizioni di stato in corrispondenza dei fronti di discesa.

Prima di entrare nel dettaglio della realizzazione è necessario fornire una

breve introduzione ai tool utilizzati.

6.6.1 HDL Designer e generazione di una macchina a stati finiti

Dato che ci si avvale dei tool HDL Designer Series, vediamo come

impostare correttamente le opzioni per la generazione automatica del codice

sulla base del diagramma a stati che andremo a realizzare. Nella figura seguente

riportiamo la schermata delle opzioni (raggiungibile dal menu Diagram -> State

Machine Properties nella finestra di generazione della macchina a stati finiti)

con i settaggi utilizzati55.

Analizziamo i vari frame di opzioni:

55

•

Machine: specifica se vogliamo realizzare una macchina sincrona o

asincrona; in quest’ultimo caso si indica l’intervallo necessario ad effettuare

gli eventuali cambiamenti di stato.

•

Clock: nel caso di macchina sincrona si specifica il segnale di clock e

l’eventuale sensibilità ai fronti di salita o discesa.

•

State Variable: indica se si deve utilizzare un tipo di dato definito