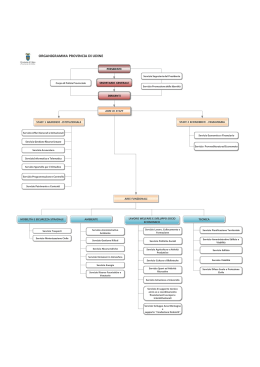

Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione SCARICHE ELETTROSTATICHE NEI CIRCUITI INTEGRATI: Come proteggerli! Gaudenzio Meneghesso UNIVERSITA' DI PADOVA Dipartimento di Ingegneria dell’Informazione Via GRADENIGO 6/A 35131 PADOVA, ITALY Tel. +39-049-827-7653 (office) Fax. +39-049-8277699 e-mail: [email protected] Gaudenzio Meneghesso Sommario: • Introduzione alle ESD; • Modelli HBM, MM, CDM, TLP; • Strutture di protezione; • Esempio di Analisi di strutture di protezione: miglioramenti; • Simulazione; • Conclusioni. ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Definitions Il problema delle ESD Più del 30 % dei guasti osservati sui circuiti integrati sono dovuti a Scariche elettrostatiche (ESD) o a Electrical Overstress (EOS). Tutti i corpi (anche quelli umani) possono caricarsi a diverse migliaia di Volts per motivi diversi. Università di Padova, Dipartimento di Ingegneria dell’Informazione • Electrical Overstress (EOS) The exposure of an object to a current or voltage beyond its maximum ratings. • Electrostatic Discharge (ESD) Soluzioni al problema EOS/ESD? • • The transfer of electrostatic charge between bodies or surfaces at different electrostatic potential. ESD is a subset of EOS. Evitare che i corpi si carichino; Proteggere i dispositivi con strutture apposite; ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione EOS/ESD FAILURES AND THEIR IMPACT •It is estimated that 25% of all component failures are due to Electrostatic Discharge (ESD) and Electrical Overstress (EOS). •EOS/ESD has been a predominant failure mechanism across all products in many companies. •Constantly changing technologies make the design of proper protection very challenging. •ESD is a high current event (1-10 Amps) with a short duration (1-100 ns); It can be overcome with design of proper on-chip protection clamps •EOS can occur due to voltage overshoots resulting in high currents for 1 us - 1 ms. EOS is very destructive but can be reduced with proper latchup reliability ESD nei circuiti integrati – Udine 22 Novembre 2005 ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione ELECTROSTATIC DISCHARGE (ESD) •What is Electrostatic Discharge? • The sudden discharge of a charged body • Triboelectric and induced charging •Importance of ESD to the Semiconductor Industry • Unexpected destruction of semiconductor devices • Losses can occur anywhere from fabrication to field • Millions of dollars in real losses each year • Unknown amount of hidden losses each year ESD nei circuiti integrati – Udine 22 Novembre 2005 1 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso People Discharge Frequently But To feel a Discharge it must be about 3,000 volts 100 volts or less can damage components! ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso All Materials Tribocharge Università di Padova, Dipartimento di Ingegneria dell’Informazione caricamento triboelettrico ElectroStatic Charge Generation: • Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD ’t Feel Can ESD That That A A Person Person Can’ Can’t Feel Can Easily Damage Electronic Can Easily Damage Electronic Components Components When 2 Surfaces in Contact then Separate • Some Atom Electrons Move Causing Imbalance One Surface Has Positive Charge & One Surface Has Negative Charge ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso www.esdsystems.com Università di Padova, Dipartimento di Ingegneria dell’Informazione caricamento per induzione ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Two Types of Materials Conductors • Electrical Current Flows Easily • So Can be Grounded • Can Discharge • Examples Metals and People ESD nei circuiti integrati – Udine 22 Novembre 2005 ESD nei circuiti integrati – Udine 22 Novembre 2005 2 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Large Charges Generated All The Time Two Types of Materials Insulators • Electrical Current Does Not Flow Easily • Cannot be Grounded • Example: Plastics • Walking across a carpet: 1,500 - 35,000 volts • Walking over untreated vinyl floor: 250 - 12,000 volts Typically very high charging • Vinyl envelope used for work instructions: 600 - 7,000 volts • Worker at a bench: 700 - 6,000 volts • Unwinding regular tape: 9,000 - 15,000 volts ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso www.esdsystems.com Università di Padova, Dipartimento di Ingegneria dell’Informazione [40] IN-PLANT ELECTROSTATIC SURVEY RESULTS (UNGER, 1981 IRPS) ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Table of Typical Generated Electrostatic Voltages* (values shown in volts) CONDITION AVERAGE READING(V) Person Walking Across Linoleum Floor 5,000 Person Walking Across Carpet 15,000 Person Working at Bench 800 Ceramic Dips in Plain Plastic Tube 700 Ceramic Dips in Plastic Set-Up Trays 4,000 Ceramic Dips in Styrofoam 5,000 Circuit Packs as Bubble Plastic Cover Removed 20,000 Circuit Packs as Packed in Foam Box 11,000 Circuit Packs (Packaged) as Returned For Repair 6,000 Event 10% 40% 50% 12,000 5,000 3,000 Motion of bench employee 6,000 800 400 Removing DIPS from plastic tube 2,000 700 400 21,000 11,000 5,500 Walking across a vinyl floor Packing PWBs in foam line box * TED DANGELMAYER, ESD PROGRAM MANAGEMENT, KLUWER ACADEMIC PUBLISHERS, 1999 ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Tiny Conductive Paths Can Easily Be Damaged Smaller components mean greater sensitivity to ESD. Damage to these components can not be detected by the naked eye. • At this magnification we see that 1/2 of the width of the material has been destroyed • At higher magnification, the pit in the area between the base and emitter becomes more obvious • Relative Humidity ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Types Of ESD Device Damage • Latent Defect Component wounded But Inspection Passes • Catastrophic Failures Inspection Able to detect Integrated Circuit ESD nei circuiti integrati – Udine 22 Novembre 2005 ESD nei circuiti integrati – Udine 22 Novembre 2005 www.esdsystems.com 3 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione The Basics Of ESD Control • Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Neutralize Insulators Via Ionizers • Charged Insulators Cannot be grounded Ground Conductors • • Shield ESDS When store or transport outside EPA Ionizer air flow floods area with Ions - Neutralizing Charge • Neutralize insulators with ionizers ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso www.esdsystems.com Università di Padova, Dipartimento di Ingegneria dell’Informazione Ground Conductors Including People • ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso www.esdsystems.com Università di Padova, Dipartimento di Ingegneria dell’Informazione STATIC CONTROL MATERIALS Materials that are used to control static electricity Wrist Straps • CONDUCTIVE: Lowest surface resistance. Poses high risk of ESD damage. Conductive (<10e5 Ohms per square) • Must work, so test wrist strap daily • DISSIPATIVE: Bleeds off charges at optimum rate. Strongly preferred. • Foot Grounders Dissipative (10e5 to < 10e12 Ohms per square) • Must work, so test foot grounder daily • INSULATIVE: Non-conductive, removed from workplace whenever possible. Poses high risk of ESD damage. (> 1x10e12 Ohms per square) ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso www.esdsystems.com Università di Padova, Dipartimento di Ingegneria dell’Informazione Shield ESD Sensitive Items Outside Protected Area Faraday Cage Charges Kept on Outside of Package: Closed Metallized Shielding Bag • Covered conductive tote box • ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Come posso difendermi da ESD: • soluzioni passive: Metto a massa …. tutto il mondo esterno; Uso mobili e superfici varie conduttive; Adatto l’ambiente esterno (umidità, ionizzatori …) Metto a massa tutti gli operatori …… ma non basta • Soluzioni attive: Strutture di protezione: ESD nei circuiti integrati – Udine 22 Novembre 2005 www.esdsystems.com ESD nei circuiti integrati – Udine 22 Novembre 2005 4 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Strutture di Protezione: VDD Segnale Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Caratteristiche di una protezione 9 Trasparenza per il segnale 9 Bassa impedenza per la scarica 9 Velocità di intervento PAD ESD VSS • Impedenza infinita rispetto al “vero” segnale entrante; • Impedenza nulla durante l’evento ESD; • Non perturbare il funzionamento del circuito stesso; 9 Robustezza alle scariche 9 Area occupata minima 9 Compatibilità con il processo del dispositivo ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso MODELLI HBM, MM, CDM Sommario: • Introduzione alle ESD; • Devo modellizare in laboratorio l’evento di scarica per potere analizzare il problema; • Modelli HBM, MM, CDM, e altri; • Devo quindi trovare dei circuiti equivalenti che rappresentino le diverse condizioni di scarica che possono interessare i dispositivi; • Strutture di protezione; • Esempio di Analisi di strutture di protezione: miglioramenti; • le situazioni più comuni sono: Corpo umano carico che si scarica (HBM), Una macchina carica che si scarica (MM), Un oggetto carico che si scarica (CDM). • Simulazione; • Conclusioni. ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso Human Body Model (HBM) Università di Padova, Dipartimento di Ingegneria dell’Informazione Machine Model (MM) 8 RV RC + V C DUT Corrente DUT (A) Simula la scarica di un corpo umano carico su un dispositivo a 1.6 massa Scarica CMM C=200nF RC=0Ω LC=2.5 μH 4 1.4 RV RC 2 1.2 1 + 0 V 0.8 LC=0.5 μH 6 C 0.6 DUT I (A ) –2 20 40 60 80 100 –4 120 140 160 180 t (20ns/DIV) 0.4 –6 0.2 –8 0 0 • • • • 20 40 60 tempo (ns) 80 100 Impulso “lento” (Rise time: 10 ns, Fall time: 100-300 ns) Elevata energia Non affetto da parassiti (vedi dopo) Scarica originata esternamente al dispositivo ESD nei circuiti integrati – Udine 22 Novembre 2005 • • • • Impulso “veloce” (pochi ns) Elevate correnti Affetto da parassiti Scarica originata esternamente al dispositivo ESD nei circuiti integrati – Udine 22 Novembre 2005 5 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Field Induced CDM Tester Charged Device Model (CDM) Simula la scarica verso massa di un dispositivo carico • • • Socketed CDM 6 Field Induced R-CDM 5 Direct Charging R-CDM v S2 Metal Plate 3 I CDM (A) S1 4 Ld Rd Cd 2 1 0 -1 -2 -3 0 0.4 0.8 1.2 1.6 2 Tempo (ns) • • • • Impulso veloce (Rise time: 200 ps, durata: 2 ns) Elevate correnti Molto sensibile agli elementi parassiti Scarica originata internamente al dispositivo This is the commonly used CDM tester and has a very fast rise time. ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD Waveforms Comparison [1] Gaudenzio Meneghesso IEC System Level ESD Stress • Very different from HBM HBM vs CDM vs MM (5000V) (500V) (500V) • Involves zapping at the system level Discharge Current, IESD (A) 14 CDM 11 • Simulation is important for device pins exposed to outside world (examples in cell phones and computer interface connections) 8 5 2 HBM • Much higher peak currents -1 MM -4 0 20 40 60 80 100 120 Time, t (ns) Courtesy of Horst Gieser IEC system level test current waveform looks like a CDM pulse on top of an HBM pulse. The peak current could be 20 or 30 Amps. Typical requirements are 8 kV using zap gun with contact discharge. ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione MODELLI per simulare ESD: • Corpo umano carico che si scarica (HBM); • Una macchina carica che si scarica (MM); • Un oggetto carico che si scarica (CDM); Altri Modelli meno noti: • • • • Università di Padova, Dipartimento di Ingegneria dell’Informazione SDM Socket discharge Model (ex CDM); IEC Contact Discharge Model; Charged board model (CBM); Cable discharge event (CDE) Related to any cable connection (LAN, …); Tutti modelli tipo GO – NO_GO e difficilmente riproducibili a causa dei parassiti. ESD nei circuiti integrati – Udine 22 Novembre 2005 ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD REQUIREMENTS (U.S.A.) 1. MIL-STD, JEDEC HBM +/- 2 KV Required by most customers Waivers given at 1 KV in some cases +/- 4 KV Delco (Auto Manufacturer) +/- 8 kv On Special Automotive Pins (Power Outputs) 2. MACHINE MODEL Phasing out by most U.S. manufacturers Some still require 200 V Waivers given to 100 V in some cases 3. CHARGED DEVICE MODEL No clear standard +/- 1000 V Some customers who require this +/- 500 V level was generally found to be reliable ESD nei circuiti integrati – Udine 22 Novembre 2005 6 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione On-Chip Protection Design ESD REQUIREMENTS (U.S.A.) (continued) 4. SPECIAL TRANSIENT TESTING Required By Auto Manufacturers With Many Different Transient Pulses ‘Load Dump’ Test - High Energy Pulse of 100 V Magnitude and 10-100 MS Long ‘Chatter Test’ - Toggle Output While Exercising The Part EMI Testing NMOS VSS VSS ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Basic diode ESD Protection Network Università di Padova, Dipartimento di Ingegneria dell’Informazione On-Chip Protection Design Protect internal circuits from ESD (Electrostatic Discharge) damage Vdd ESD Current Shunt Output Pad Clamp Circuit Input gate oxide failure Vss Output drain thermal failure ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Basic diode ESD Protection Network VDD Diode clamps PMOS NMOS PAD D1 Current Shunt Vss ESD I/O PAD Vdd ESD Clamp Circuit Input Pad ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione VSS The ESD Clamp is designed to protect the Input gates or the Output drain junctions by discharging the high ESD current. The clamp has a low resistance to Vss (Ground) during ESD. Inputs/Outputs/Power Pins Gaudenzio Meneghesso NMOS ESD Clamp WHAT SHOULD THE PROTECTION DEVICE DO? Clamp the ESD Voltage to Shunt the ESD Stress Current Turn on Fast (Less Than 1 ns) Carry Large Currents of 2 Amps or More for 150 ns Have Low-on-Resistance Occupy Minimum Area at the Bond Pad Have Minimum Capacitance Introduce Minimum Series Resistance Be Immune to Process Drifts Be Robust for Numerous Pulses Offer Protection for Various ESD Stress Models Not Interfere With the I/C’s Functional Testing Not Cause Increased Vcc or I/O Leakage Survive the Burn-in Tests PMOS IC Pin ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Input PMOS 5. IEC SYSTEM LEVEL TEST Important for chip pins exposed to outside world (examples in cell phones and computer interface connections) 8 kV Contact Discharge Level required by most customers Gaudenzio Meneghesso VDD VDD Output R VSS D1 deve avere un Vbr inferiore al breakdown dell’OX Per tensioni positive, il diodo va in Break. Per tensioni negative, il diodo va in conduzione diretta. ESD nei circuiti integrati – Udine 22 Novembre 2005 Current limiting resistor Thin gate oxides ESD nei circuiti integrati – Udine 22 Novembre 2005 7 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Basic diode ESD Protection Network Vdd Suply Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione BJT-based ESD Protection Network VDD VDD D2 D4 R PMOS I/O PAD NMOS PMOS I/O PAD D3 D1 NMOS GND VSS VSS This is the traditional protection concept where diodes are used. D1 provides protection to GND and D2 for protection to Vdd. D3 and D4 are local clamps for oxide protection. However, in advanced technologies D1 and D3 are not efficient GND and are replaced by NMOS protection concepts. ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Collettore Emettitore SD L + + n p P Caratteristiche statiche - SNAPBACK 50 Transistor Bipolare Laterale 45 C orre nte d i colle tto re (mA) Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD DESIGN WINDOWS Strutture di Protezione: SS n+ Gaudenzio Meneghesso Substrato 40 35 30 3 It2, Vt2 VDD+10% Current [A] Gaudenzio Meneghesso ESD nei circuiti integrati – Udine 22 Novembre 2005 Core Overvoltage 2 Vh 1 It1, Vt1 25 0 20 0 15 2 4 6 8 10 Voltage [V] 10 5 This represent a good design 0 0 2 4 6 8 10 12 Tensione di collettore (V) ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD DESIGN WINDOWS 3 It2, Vt2 3 Core Overvoltage 2 Vh 1 Core OverVoltage VDD+10% Current [A] Current [A] VDD+10% ESD DESIGN WINDOWS It1, Vt1 0 2 It2, Vt2 Vh 1 It1, Vt1 0 0 2 4 6 8 10 Voltage [V] NO- Internal core damaged prior to the ESD protectionj elements turn-on! ESD nei circuiti integrati – Udine 22 Novembre 2005 0 2 4 6 8 10 Voltage [V] NO- Inefficient ESD protection element! ESD nei circuiti integrati – Udine 22 Novembre 2005 8 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD DESIGN WINDOWS 3 It2, Vt2 Current [A] VDD+10% Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Caratteristiche di una protezione Core Overvoltage 9 Trasparenza per il segnale 9 Bassa impedenza per la scarica 2 9 Velocità di intervento Vh 1 It1, Vt1 9 Robustezza alle scariche 9 Area occupata minima 0 0 2 4 6 8 10 9 Compatibilità con il processo del dispositivo Voltage [V] NO- SELF-triggering possible! ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione NMOS Transistor Bipolar Breakdown IN UNA TECNOLOGIA CMOS? VDD PMOS I/O PAD Gate Source Drain N+ NMOS VSS C B P-Substrate An NMOS transistor under ESD conditions can operate as a parasitic bipolar transistor. That is, the surface conduction of the MOSFET switches to bipolar conduction through bulk. GND Grounded Gate NMOS (GGNMOS) Very primitive and simple ESD protection elements within a pure CMOS technology (GGNMOS concept) Drain becomes Collector (C), Substrate becomes Base (B), and Source becomes Emitter (E) to form the NPN transistor. ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso N+ E ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione PROTECTION CIRCUIT ELEMENTS Cross-section of a lateral SCR Device in CMOS [6] BVox I(A) VDD X Y R-nwell Lateral NPN Snapback ~ 2-5 Ohms Vbe (pnp) PNP 2 Forward Diode ~ 5 Ohms NPN PN Diode Reverse Biased ~ 5075 Ohms SCR latch ~1-2 Ohms 1 Vbe (npn) Lateral PNP Snapback ~ 10-15 Ohms R-pwell VSS The lateral NPN and the vertical PNP form the SCR. Rnwell and Rsub play critical role in the trigger of the SCR. Modifications are done to this structure to lower its trigger voltage since the nwell breakdown is too high. Anode/Cathode spacings (X/Y) determine the trigger for this SCR. ESD nei circuiti integrati – Udine 22 Novembre 2005 2 4 6 8 10 V(Volts) Any type of ESD clamp must protect the gate oxide with a breakdown of Bvox. ESD nei circuiti integrati – Udine 22 Novembre 2005 9 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso ESD Design Example 1 Università di Padova, Dipartimento di Ingegneria dell’Informazione STANDARD APPROACH Vdd ESD prot. ESD Parameters: NMOS Vbr = 12 V, Vsp = 8 V, It2 = 5 mA/um; SCR Vtr = 14 V; Vox = 15 V. To Input Gate I/O/ NMOS SCR R=? Pad ESD prot. W = 60 um Vox is too close to the SCR trigger. Therefore a secondary stage with resistor and grounded gate NMOS is needed. Vtr -Vsp = 6 V = I*R; W=60 um, I(f) = 300 mA; R = 6V/300 mA = 20 ohms. For worst case design, use R = 40 ohms. Do not make NMOS larger than 2 fingers. Otherwise, a resistor is needed for each finger. Università di Padova, Dipartimento di Ingegneria dell’Informazione BIG CLAMP APPROACH (I) Advantages: Lowering of the parasitic capacitance in parallel with the I/O; Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD induced damages in ICs Drawbacks: Large parasitic capacitance in parallel with the I/O; ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione BIG CLAMP APPROACH (II) CRITICAL POINT: The voltage drop along the Vdd and Vss line must be taken into account. (distributed ESD protection, EOS/ESD 2001) ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Circuit to be protected Vss ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Advantages: Protection close to the internal circuit; ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione EOS Damage A brief overview of different ESD induced damages will be given in the next. This type of severe damage is not related to ESD but is caused by overstress. ESD nei circuiti integrati – Udine 22 Novembre 2005 ESD nei circuiti integrati – Udine 22 Novembre 2005 10 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso ESD Models Comparison MM Model HBM Test Levels (Volts) 500, 1000, 1500 2000, 2500 Pulse Width (ns) ~150 Rise Time 2-10 ns Università di Padova, Dipartimento di Ingegneria dell’Informazione Transistor Damage in an IC CDM 100, 150, 200 250, 500, 750, 1000 ~80 ~1 n/a Drain [1] To IC Output Pin To IC Input Pin Gate <400 ps Source To IC Ground Pin • Junction Damage Typical ESD Failures • Metal Penetration • Gate Oxide Damage • Metal Melt • Charge Trapping • Contact Spiking • Junction Damage Drain Junction Edge Damage Due to Heating (Notching) Leakage Current < 1 μ A • Gate Oxide Damage Amerasekera and Duvvury, ESD In Silicon Integrated Circuits, John Wiley 2002. ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Transistor Damage in an IC [1] Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione OXIDE DAMAGE FROM ESD EVENTS [28] To IC Output Pin Drain Drain To IC Output Pin To IC Input Pin To IC Input Pin Gate Source Gate To IC Ground Pin Source To IC Ground Pin Drain to Source Filamentation leakage Current ~ 10 μA Gate Oxide Damage Due to Voltage Buildup Amerasekera and Duvvury, ESD In Silicon Integrated Circuits, John Wiley 2002. ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Metal Interconnect Failure With ESD Pulses Drain Chaine, ESD Symp. 1994 leakage Current > 1 nA. Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione [31] To IC Output Pin To IC Input Pin Gate ADVANCED PROCESS EFFECTS Source To IC Ground Pin Metal connections to the IC circuits can blow up during ESD causing open circuit failures. Proper metal width has to be designed using characterization under ESD pulses. Banerjee et al., IRPS 96, EDL Sept. 1997 ESD nei circuiti integrati – Udine 22 Novembre 2005 ESD nei circuiti integrati – Udine 22 Novembre 2005 11 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Technology Scaling Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Caratteristiche di una protezione 0.13 9 Trasparenza per il segnale 0.10 9 Bassa impedenza per la scarica 20 9 Velocità di intervento Yes 9 Robustezza alle scariche Yes 9 Area occupata minima The present technologies are between 0.35 and 0.13 um. Both LDD and sailicides are part of the technologies that can have a major impact on ESD. Blocking the silicide and/or adding a deeper drain/source implant to overcome the LDD effects form an important process option for ESD. 9 Compatibilità con il processo del dispositivo ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione Cross-Section of an Advanced NMOS Transistor Gate Oxide Silicide Drain N+ Sidewall P Evolution of ESD Protection Circuits N+ Lightly Doped Region P-Well Process Issues for ESD STI Effect NMOS GCNMOS with Sub. Trig. LDD Effect 5000 Re-optimized SCR FOD 4000 Silicide Effect 3000 Silicide + thin Epi Effect 2000 Abrupt Junctions 0 1980 Salicides 1985 1990 1995 GCNMOS - Gate Coupled Device FOD SCR GCNMOS PTNMOS NTNMOS PLTSCR PTNMOS - PNP Driven Sub. Trig. LDD Junctions 2000 Year ESD nei circuiti integrati – Udine 22 Novembre 2005 Università di Padova, Dipartimento di Ingegneria dell’Informazione SCR 6000 It2 can be influenced by several process features that are indicated here. Gaudenzio Meneghesso Thin Epi Effect 7000 1000 P-Substrate/Epi Layer FOD - Field Oxide Device 8000 Source N- Surface Implants Pocket Implant Università di Padova, Dipartimento di Ingegneria dell’Informazione [1] Gate P N- Gaudenzio Meneghesso ESD HBM (V) Gaudenzio Meneghesso ESD nei circuiti integrati – Udine 22 Novembre 2005 NTNMOS - MOS Driven Sub. Trig. PLTSCR - Gate Isolated SCR ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Process Effects: Silicide • Process has a major impact on ESD performance and protection design. • LDD junctions improve CHC but have negative impact on ESD due to increased power dissipation in the junction. • Silicided diffusions for improved circuit speed have drastic negative effect on ESD due to reduced resistance and susceptibility to heat damage. • Low resistance substrates improve Latchup but degrade ESD with reduced It2. • Trade-off between ESD, CHC, and Latchup is important during process development. ESD nei circuiti integrati – Udine 22 Novembre 2005 Drain contact to gate spacing is an important parameter for non-silicided NMOS devices. Optimum value depends on the technology but it is usually around 4 um. ESD nei circuiti integrati – Udine 22 Novembre 2005 12 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione [42] But: SUBSTRATE PUMP NMOS CONCEPT Floating P+ Guardring connection to pump source Booting Capacitor PAD Protection NMOS Floating guardring to ground resistance NMOS body to floating guardring resistance Substrate Pump NMOS Substrate Resistance Duvvury et al., ESD Symp. 00 Gate Resistor Keppens et al. (Sarnoff Europe), Active-Area-Segmentation (AAS) Technique for Compact, ESD Robust, Fully Silicided NMOS Design, 25th EOS/ESD Symposium, September 21-25, 2003. ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Require an extra mask Require large GD spacing Is very area consuming Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Keppens et al. (Sarnoff Europe), Active-Area-Segmentation (AAS) Technique for Compact, ESD Robust, Fully Silicided NMOS Design, 25th EOS/ESD Symposium, September 21-25, 2003. Keppens et al. (Sarnoff Europe), Active-Area-Segmentation (AAS) Technique for Compact, ESD Robust, Fully Silicided NMOS Design, 25th EOS/ESD Symposium, September 21-25, 2003. ESD nei circuiti integrati – Udine 22 Novembre 2005 ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Multi-Finger Turn-on - domino-type OTTIMIZZAZIONE? Silicon proven circuits – lower clamping voltage – more ESD design window margin – perfect width scaling – area efficient devices ESD nei circuiti integrati – Udine 22 Novembre 2005 13 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Gaudenzio Meneghesso Simulazione di dispositivo Università di Padova, Dipartimento di Ingegneria dell’Informazione Simulazione di dispositivo Dopo snap Prima dello snap BV = 7V Corrente Temperatura Corrente ESD nei circuiti integrati – Udine 22 Novembre 2005 Temperatura ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso SPICE-Based ESD Protection Design Utilizing Diodes and Active MOSFET Rail Clamp Circuits Università di Padova, Dipartimento di Ingegneria dell’Informazione Why Not Direct I/O to VSS ESD Protection with Snapback Clamps? OVDD PMOS BUFFER LPNP + I/O Pad Snapback Clamps PRIMARY ESD CURRENT PATH Ballast Res. Snapback Clamp LNPN NMOS BUFFER VSS Problems with Snapback Clamps; Rely on avalanching junctions to trigger parasitic LNPN or SCR. Highly process sensitive, often not scalable, difficult to simulate. Clamps occupy too much layout area. NMOS output buffer must be protected with ballast resistance. May add significant capacitance to the I/O. May require ESD vs. latchup trade-offs. Difficult to quantify or manage ESD risk with foundry processes. Often not reliable for sub-0.25μm technologies. ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione ESD Modeling/Simulation ESD circuit simulation for the 0.18 um technology NMOS transistors was improved by including in the model simulation of the breakdown between the external base and the emitter diffusion as well as the forward bias condition. Ref: H. Wolf et al., Proc. of the IRPS, p162, 2002 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione Introduction Why Rail-Based I/O Protection without Snapback Clamps? OVDD PRIMARY ESD CURRENT PATH TRIGGER CIRCUIT VPNP BJT PMOS LPNP + M0 I/O Pad N+ Diode LNPN Active MOSFET Rail Clamp NMOS VSS The simplified NMOS sub-circuit model consisting of the BSIM3 model and the bipolar extension. This simulation approach is to enable duplication of “real world” failures in products. High current simulation result for 2 kV. For Pad to VDDP stress, 1 A goes through the PMOS diode, but the NFET (circled) used as a protection diode fails because of excess current (50 mA). ESD nei circuiti integrati – Udine 22 Novembre 2005 Advantages of Rail-Based ESD protection; No avalanching junctions in primary ESD current path. Highly process portable, scalable, and easy to simulate w/ SPICE. Most layout area efficient ESD solution. [Stockinger03] Ballast resistance not needed in the NMOS output buffer. Least added I/O capacitance of available ESD options. [Richier00] ESD and latchup unrelated – may be independently optimized. Quantify and manage ESD risk independent of foundry processes. Highest probability of first-pass ESD Qualification. ESD nei circuiti integrati – Udine 22 Novembre 2005 14 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione New Idea: Boosted ESD Rail Clamps for I/O Protection Boost 20 Ω 9.6V OVDD 7.5V 20 Ω 9.6V 0.2 Ω 0.2 Ω 7.0V 9.6V Boost OVDD 6.5V PRIMARY ESD CURRENT PATH TRIGGER CIRCUIT A1 A2 10.8V + 3.8A A1 A2 PMOS I/O1 Pad 0.0V M0 LPNP2 PMOS 9.6V I/O2 Pad NMOS B LNPN1 NMOS B NMOS CLAMP M0 W = 2384μm Vds = 2.7V Vgs = 5.8V Ids = 1.34 mA/μm 3.8V VSS VSS Add a small A2 diode (VPNP) in each I/O cell and a narrow “Boost” bus. Power the ESD trigger circuits with the Boost bus. A1 & B size unchanged from prior example. M0 resized such that both Vds(NMOS1) and Vds(PMOS2) remain 7.0V. IR drops along the primary ESD current path not seen at trigger circuit. During ESD, the M0 Vgs is Boosted well above Vds. Ids increases ~2X so that the clamp width may be reduced by half! [Stockinger03] ESD nei circuiti integrati – Udine 22 Novembre 2005 Gaudenzio Meneghesso Università di Padova, Dipartimento di Ingegneria dell’Informazione IMPORTANT ISSUES IN ESD • Process sensitivity of protection circuits • Process monitor, Fab to Fab sensitivity • Advanced drain junction and silicide effects • Internal core ESD failures • Oxide failures due to Charged Device Model stress • Mixed voltage protection - trade off with CHC • RF Designs • Complex package effects • Compatibility of HBM and MM requirements • I/O protection area scaling • Bus resistance effects • New technologies : SOI, non-epi, STI • Test equipment standards for CDM and MM • Accurate simulation and modeling methods ESD nei circuiti integrati – Udine 22 Novembre 2005 15

Scaricare