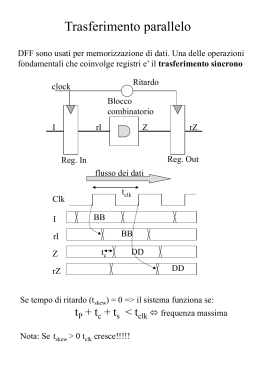

Metodi per la misura di intervalli temporali con una risoluzione del picosecondo Salvatore Loffredo 18 maggio 2007 Indice: La terminologia e i parametri tecnici caratteristici di un TDC Metodi di misura e di interpolazione Interpolazione mediante l’utilizzo di Field Programmable Gate Array Caratteristiche di disegno Confronto delle prestazioni di differenti TDC realizzati con diverse tecnologie Conclusioni Principali prestazioni e parametri delle misure di tempo di volo (TOF) Principali prestazioni e parametri delle misure di tempo di drift Misura di un intervallo temporale Parametri che caratterizzano un TDC: range di misura precisione risoluzione non linearità differenziale (DNL) e integrale (INL) tempo morto velocità di lettura Funzione di trasferimento ideale e reale di un TDC a 10 bit Ideale Reale _____ Non linearità differenziale: Non linearità integrale: DNLi LSBi LSB _____ LSB _____ j 1 LSBi LSB INL j _____ i 1 M LSB Metodo del contatore Risoluzione uguale al periodo del clock Lungo intervallo di misura L’errore massimo di una singola misura può raggiungere quasi ± T0 T0 1 f0 Tp nT0 T c Frc T0 T1 T T2 T1 T0 T p(T1 ) 1 c p(T2 ) c T pT1 qT2 1 T1 T 0 2 T2 T 0 Metodo del contatore T0 pq T0 c(1 c) T0 2 T av 0 0.39T0 8 max N N1 N 2 N max p N1 N q 2 N N TN T0 T0 T Nav 0.39 0 8 N N 2 N T1 N1 T2 N 2 N T TN Hewlett-Packard 1970, Time interval averaging L’errore sulla misura è diminuito di Per modalità di utilizzo multihit è preferibile campionare le uscite del contatore negli istanti di start e stop N Metodi utilizzati per realizzare TDC con elevata risoluzione: Stretching temporale (A) seguito dal metodo del contatore (D) Doppia conversione: tempo-ampiezza (A) seguita dalla conversione standard analogico-digitale (A/D) Il metodo di Vernier con due oscillatori (D) Conversione tempo-digitale utilizzando delle linee di ritardo (D) Il metodo di Vernier con una linea di ritardo differenziale che comprende due linee di ritardo (D) In generale i metodi analogici classici sono più difficili da implementare in un ASIC, sono più sensibili alla temperatura ed hanno un tempo di conversione più lungo Stretching temporale I2 I1 Fattore di stretch: I I K 1 2 I2 Tempo di scarica: Tr TK Tempo totale: Conversione analogico/analogico/digitale Risultato di una misura: Risoluzione: T T LSB 0 K 1 nT0 K 1 T Tr T ( K 1) Tempi di conversione lunghi Circuiti discreti a basso costo Risoluzione fino a 10 ps Doppio stadio di stretching Risoluzione fino a 1 ps Kalisz et al.,1987 In tecnologia 0.35 μm CMOS Risoluzione fino a 50 ps, Chen et al., 2006 Conversione tempo-ampiezza Risoluzione: LSB T0 K Risultato di una misura: T nT0 K Conversione analogico/analogico/digitale Circuiti discreti a basso costo In tecnologia 0.8 μm Bi-CMOS Risoluzione da 1 a 20 ps Kostamovaara et al, 1998 Kalisz et al., 1994 Risoluzione fino a 32 ps, Raisanen et al., 2006 Ottime risoluzioni, basso errore di quantizzazione Bassi tempi di conversione, caratteristici dell’ADC Errore di linearità e di precisione superiori alla risoluzione Metodo di Vernier 1 T2 Risoluzione: r T1 T2 f1 1 T1 f2 Tempo di conversione massimo: TT n2 maxT2 1 2 r r 100 ps Se T1 10ns e T2 9.9ns Risultato di una misura: T (n1 1)T1 (n2 1)T2 TD 990ns (n1 n2 )T1 (n2 1)r Se T T1 n1 n2 T (n2 1)r In tecnologia Si Bipolare Buone risoluzioni Tempi di conversione elevati Risoluzione fino a 1 ps, Otsujy, 1993 Conversione temporale mediante linee di ritardo, TDC Flash T K HP5371A Stephenson, 1989 Risoluzione 200 ps 0.8 μm CMOS Gorbics et al., 1997 Risoluzione 46.9 ps 0.25 μm CMOS Mota et al., 2000 Risoluzione 24.4 ps 0.6 μm CMOS Mantyniemi et al., 2002 Risoluzione 29.6 ps 0.35 μm CMOS Jansson et al., 2006 Risoluzione 12.5 ps Vernier differenziale m 1 T m 2 T m( 1 2 ) TD TP TMAX Se 1 1.6ns TD 15TMAX 1 2 Risoluzione TMAX N ( 1 2 ) Tempo massimo misurabile TP N 1 Tempo di propagazione della linea TMAX 1 TMAX 1 1 TMAX 1 2 1 2 e 2 1.5ns 1 2 100 ps se TMAX 10ns Tempo morto massimo Buone risoluzioni Tempi di conversione elevati TD 150ns In tecnologia 0.7 μm CMOS Risoluzione fino a 5 ps, Dudek et al., 2000 Interpolazione di Nutt T NCT0 N A A N B B Nutt, 1968 A Risoluzione TDC start B Risoluzione TDC stop Risoluzione uguale a quella dei TDC a breve range Lungo intervallo di misura, limitato dai bit del contatore In tecnologia 0.65 μm CMOS FPGA QuickLogic Risoluzione fino a 100 ps, contatore e Vernier differenziale, Kalisz et al., 2000 In tecnologia 0.65 μm CMOS FPGA Xilinx Risoluzione fino a 70 ps, contatore e linee di ritardo, Wu et al., 2006 TDC in Field Programmable Gate Array Linea di ritardo Vernier in FPGA, Kalisz et al., 2000 Interpolazione all’interno del periodo del segnale di clock (100 MHz, 10 ns) 128 celle utilizzate del dispositivo FPGA della famiglia pASIC2 della QuickLogic T m( 1 2 ) 1 2 100 ps Risoluzione Tempo massimo TMAX N ( 1 2 ) 128 100 ps 12.5ns misurabile dal Vernier 1 TD 1 TMAX Tempo morto massimo 1 2 TDC in Field Programmable Gate Array Linea di ritardo in FPGA, Wu et al., 2006 Interpolazione all’interno del periodo del segnale di clock (96 MHz, 10.4 ns) 144 celle utilizzate del dispositivo FPGA della famiglia Virtex II della Xilinx T m 69.5ps Risoluzione TMAX N 144 69.5 ps 10ns Sum A B Ci Co AB ( A B )Ci Tempo morto indipendente dall’intervallo temporale misurato T0 TDC in Field Programmable Gate Array Linea di ritardo in FPGA, Wu et al., 2006 Non linearità della conversione introdotta dalla disposizione delle risorse logiche all’interno dell’FPGA Non linearità della conversione introdotta dallo skew della rete di distribuzione del segnale di clock Skew massimo del segnale di clock=64 ps TDC in Field Programmable Gate Array Linea di ritardo in FPGA, Xilinx Virtex 5 Tempo di propagazione tra l’ingresso CIN e l’uscita COUT della slice=90 ps Skew massimo del segnale di clock all’interno di una “regione di clock”=12 ps Device Clock Manager (DCM) Il DCM interno alla Virtex 5 consente di moltiplicare il segnale di clock di riferimento Il DCM genera quattro repliche del segnale di clock sfasate l’una rispetto all’altra di 90° Si raggiungono risoluzioni del contatore ‘coarse’ pari ad 1/4 del periodo di clock Correzione della non linearità, Kalisz, 2003 1) Identificare la non linearità utilizzando dei treni di impulsi casuali, effettuare N misure per realizzare un istogramma per gli M canali Contenuto ideale di ogni canale: Ma in un caso reale: DNLi ns ni ns ns j INL j i 1 DNLi M 2) Utilizzare dei vettori di correzione, contenenti M valori di INL N M Precisione del TDC, Mantyniemi, 2004 q 2 st 2 sp 2 clk 2 stinl 2 spinl 2 q Errore di quantizzazione st Jitter del segnale di start sp Jitter del segnale di stop clk Jitter del segnale di clock di riferimento stinl Deviazione standard dell’INL dell’interpolatore di start pinl Deviazione standard dell’INL dell’interpolatore di stop Confronto delle prestazioni: Conclusioni: Sono state presentate varie architetture di TDC presenti in letteratura È stato analizzata la struttura basata sul metodo di interpolazione di Nutt, implementabile in FPGA L’utilizzo di dispositivi FPGA consente un’elevata flessibilità di disegno di TDC Le tecnologie attuali consentono di ottenere elevate risoluzioni (30 ps su Virtex 5) La struttura della Virtex 5 consente anche di monitorare i parametri che influenzano il funzionamento del TDC (temperatura e tensione di alimentazione del dispositivo)

Scaricare