UNIVERSITÀ DI CATANIA

Facoltà di Ingegneria

corso di laurea in Ingegneria Informatica

Massimo Trubia

PROGETTO E IMPLEMENTAZIONE DI UN MODELLO DI

FLOATING POINT UNIT IN UN SIMULATORE DI CPU MIPS64

Tesi di Laurea

Relatore:

Chiar.mo Prof. V. Catania

Correlatori:

Ing. F. Fazzino

Ing. D. Patti

Anno Accademico 2006/2007

Indice

1 Introduzione

1.1

2

Obiettivo della tesi . . . . . . . . . . . . . . . . . . . . . . . . . .

2

1.1.1

EduMIPS64 . . . . . . . . . . . . . . . . . . . . . . . . . .

3

1.2

Contributi . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

1.3

Panoramica della tesi . . . . . . . . . . . . . . . . . . . . . . . . .

4

2 L’architettura MIPS64

5

2.1

Storia dei processori RISC . . . . . . . . . . . . . . . . . . . . . .

5

2.2

Architettura Load/Store . . . . . . . . . . . . . . . . . . . . . . .

7

2.3

Registri . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

2.4

Indirizzamento . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8

2.5

Instruction set . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9

2.5.1

Formati delle istruzioni . . . . . . . . . . . . . . . . . . . .

9

2.5.2

Raggruppamento per funzionalità . . . . . . . . . . . . . .

11

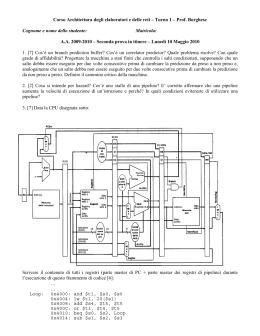

Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14

2.6.1

Implementazione di una pipeline a cinque stadi . . . . . .

16

2.6.2

Dipendenze . . . . . . . . . . . . . . . . . . . . . . . . . .

17

2.6.3

Hazard . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20

2.6

I

3 La floating point unit dei processori MIPS64

23

3.1

Numeri in virgola mobile . . . . . . . . . . . . . . . . . . . . . . .

23

3.2

Standard IEEE 754-1985 . . . . . . . . . . . . . . . . . . . . . . .

24

3.2.1

Memorizzazione di un numero floating point . . . . . . . .

25

3.2.2

Valori speciali . . . . . . . . . . . . . . . . . . . . . . . . .

26

3.2.3

Eccezioni . . . . . . . . . . . . . . . . . . . . . . . . . . .

28

3.2.4

Arrotondamenti . . . . . . . . . . . . . . . . . . . . . . . .

30

3.2.5

Operazioni floating point . . . . . . . . . . . . . . . . . . .

31

3.3

Floating point unit e standard IEEE 754 . . . . . . . . . . . . . .

34

3.4

Registri floating point . . . . . . . . . . . . . . . . . . . . . . . .

35

3.4.1

FCSR . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

35

3.4.2

Altri registri . . . . . . . . . . . . . . . . . . . . . . . . . .

37

Instruction set . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

38

3.5.1

Trasferimento dati . . . . . . . . . . . . . . . . . . . . . .

38

3.5.2

Aritmetiche . . . . . . . . . . . . . . . . . . . . . . . . . .

39

3.5.3

Conversione . . . . . . . . . . . . . . . . . . . . . . . . . .

39

3.5.4

Spostamento operandi formattati . . . . . . . . . . . . . .

40

3.5.5

Salto condizionale . . . . . . . . . . . . . . . . . . . . . . .

40

Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

41

3.6.1

Concorrenza sul register file . . . . . . . . . . . . . . . . .

42

3.6.2

Rilevamento degli hazard . . . . . . . . . . . . . . . . . . .

43

3.6.3

Pipeline FP del MIPS R4000 . . . . . . . . . . . . . . . .

44

3.5

3.6

4 La floating point unit di EduMIPS64

4.1

46

Operazioni floating point . . . . . . . . . . . . . . . . . . . . . . .

46

4.1.1

48

Gestore delle eccezioni sincrone . . . . . . . . . . . . . . .

II

4.2

4.3

4.4

4.1.2

Addizione . . . . . . . . . . . . . . . . . . . . . . . . . . .

49

4.1.3

Moltiplicazione . . . . . . . . . . . . . . . . . . . . . . . .

50

4.1.4

Divisione . . . . . . . . . . . . . . . . . . . . . . . . . . . .

51

Registri . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

53

4.2.1

FCSR . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

53

Instruction set . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

57

4.3.1

Classe Instruction . . . . . . . . . . . . . . . . . . . . . . .

57

4.3.2

Classi base dell’instruction set . . . . . . . . . . . . . . . .

58

4.3.3

Ereditarietà dalla classe ComputationalInstructions . . . .

59

4.3.4

Ereditarietà dalla classe FlowControlInstructions . . . . .

65

4.3.5

Ereditarietà dalla classe LDSTInstructions . . . . . . . . .

66

Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

67

4.4.1

Pipeline floating point . . . . . . . . . . . . . . . . . . . .

67

4.4.2

File di configurazione della FPU . . . . . . . . . . . . . . .

68

4.4.3

Interazione tra CPU ed FPU . . . . . . . . . . . . . . . . .

69

5 Conclusioni

78

A Manuale utente della FPU di EduMIPS64

80

A.1 Introduzione . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

80

A.2 Valori speciali . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

81

A.2.1 NaN o Invalid Operation . . . . . . . . . . . . . . . . . . .

81

A.2.2 Zeri o Underflow . . . . . . . . . . . . . . . . . . . . . . .

81

A.2.3 Infiniti od Overflow . . . . . . . . . . . . . . . . . . . . . .

82

A.2.4 Infiniti o Divide by zero . . . . . . . . . . . . . . . . . . .

82

A.3 Configurazione delle eccezioni . . . . . . . . . . . . . . . . . . . .

82

III

A.4 Direttiva .double . . . . . . . . . . . . . . . . . . . . . . . . . . .

84

A.5 Registro FCSR . . . . . . . . . . . . . . . . . . . . . . . . . . . .

84

A.6 Instruction set . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

85

IV

Elenco delle figure

2.1

Formati dell’ISA MIPS64 . . . . . . . . . . . . . . . . . . . . . . .

10

2.2

Pipeline di EduMIPS64 . . . . . . . . . . . . . . . . . . . . . . . .

16

3.1

Formato dei numeri FP in doppia precisione . . . . . . . . . . . .

25

3.2

Formato dei numeri FP in singola precisione . . . . . . . . . . . .

25

3.3

Mantisse prima della moltiplicazione . . . . . . . . . . . . . . . .

32

3.4

Risultato del prodotto fra le mantisse prima della normalizzazione

32

3.5

Prodotto normalizzato prima dell’arrotondamento . . . . . . . . .

32

3.6

Mantisse prima dell’addizione . . . . . . . . . . . . . . . . . . . .

33

3.7

Risultato della somma delle mantisse prima della normalizzazione

34

3.8

Mantissa normalizzata prima dell’arrotondamento . . . . . . . . .

34

3.9

Registro FCSR . . . . . . . . . . . . . . . . . . . . . . . . . . . .

36

3.10 Pipeline a 5 stadi . . . . . . . . . . . . . . . . . . . . . . . . . . .

41

3.11 Register file di un processore MIPS64 . . . . . . . . . . . . . . . .

42

4.1

Sommatore floating point (R1+R2=R3) . . . . . . . . . . . . . .

50

4.2

Moltiplicatore floating point . . . . . . . . . . . . . . . . . . . . .

52

4.3

Divisore floating point . . . . . . . . . . . . . . . . . . . . . . . .

52

4.4

Diagramma delle classi dei registri di EduMIPS64 . . . . . . . . .

54

4.5

Modalità di accesso alla classe FCSRRegister . . . . . . . . . . . .

54

V

4.6

Classe Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . .

58

4.7

Classi base dell’istruction set . . . . . . . . . . . . . . . . . . . . .

59

4.8

Classi ereditate da ComputationalInstructions . . . . . . . . . . .

60

4.9

Ereditarietà dalla classe FlowControlInstructions

. . . . . . . . .

65

4.10 Ereditarietà dalla classe LDSTInstructions . . . . . . . . . . . . .

66

4.11 Diagramma UML delle classi della pipeline FP . . . . . . . . . . .

68

A.1 Configurazione delle trap per le eccezioni IEEE . . . . . . . . . .

83

A.2 Opzione che maschera le eccezioni sincrone(disabilita tutte le trap)

83

A.3 Finestra che notifica la trap . . . . . . . . . . . . . . . . . . . . .

83

A.4 Registro FCSR in EduMIPS64 . . . . . . . . . . . . . . . . . . . .

85

A.5 Configurazione modalità di arrotondamento . . . . . . . . . . . .

90

VI

Elenco delle tabelle

2.1

Campi delle istruzioni

. . . . . . . . . . . . . . . . . . . . . . . .

11

3.1

Dati di conversione decimale/single . . . . . . . . . . . . . . . . .

26

3.2

Parametri di formato dello standard IEEE 754 . . . . . . . . . . .

26

3.3

Rappresentazione dei valori speciali . . . . . . . . . . . . . . . . .

27

3.4

Istruzioni di trasferimento dati . . . . . . . . . . . . . . . . . . . .

39

3.5

Istruzioni aritmetiche . . . . . . . . . . . . . . . . . . . . . . . . .

39

3.6

Istruzioni di conversione . . . . . . . . . . . . . . . . . . . . . . .

40

3.7

Istruzioni di spostamento degli operandi formattati . . . . . . . .

40

3.8

Istruzioni di salto condizionale . . . . . . . . . . . . . . . . . . . .

40

3.9

Operazioni primitive della pipeline FP dell’R4000 . . . . . . . . .

45

3.10 Operazioni FP dell’R4000 . . . . . . . . . . . . . . . . . . . . . .

45

3.11 Stalli nelle unità funzionali . . . . . . . . . . . . . . . . . . . . . .

45

A.1 Esempi sui tipi di arrotondamento . . . . . . . . . . . . . . . . . .

90

VII

Listati

4.1

Scrittura dei codici condizionali sull’FCSR . . . . . . . . . . . . .

55

4.2

Scrittura dei bit di causa sull’FCSR . . . . . . . . . . . . . . . . .

55

4.3

Metodo che memorizza i dati della GUI sull’FCSR . . . . . . . . .

56

4.4

Porzione della funzione che effettua il confronto tra registri . . . .

63

4.5

Invocazione metodo EX e gestione eccezioni sincrone . . . . . . .

73

4.6

Gestione dello stadio ID . . . . . . . . . . . . . . . . . . . . . . .

76

1

Capitolo 1

Introduzione

1.1

Obiettivo della tesi

Nei corsi universitari in cui si studiano le architetture dei calcolatori si usano,

come ausilio didattico, simulatori che modellano in modo realistico questi sistemi.

In particolare, studiando vari tipi di processori e le istruzioni in codice Assembly

che essi possono elaborare, i simulatori assumono un ruolo preponderante, in

quanto consentono l’ispezione dei valori delle celle di memoria, dei registri e della

pipeline, mentre le istruzioni sono processate; valutano statistiche di calcolo, ed

eseguono diverse altre operazioni.

Di seguito sono elencati alcuni motivi per i quali, tra i vari tipi di processori,

sempre più spesso nei corsi universitari e nelle scuole tecniche si studiano le architetture MIPS. I progettisti hanno realizzato un set di istruzioni ”pulito”: le

istruzioni sono divise in soli tre tipi (R, I e J) che saranno illustrati nei capitoli

successivi. I processori RISC sono intrinsecamente più semplici rispetto ai CISC,

e da non trascurare è il fatto che MIPS è dominante nelle applicazioni embedded,

come fotocamere digitali, TV digitali, consolle da gioco, router di rete e cosı̀ via.

2

CAPITOLO 1. INTRODUZIONE

1.1.1

EduMIPS64

EduMIPS64 è originariamente nato come semplice porting GPL1 a Java Swing

del simulatore WinMIPS64. Il gruppo di sviluppatori di EduMIPS64 aveva deciso,

nella prima metà del 2006, di dar vita ad un progetto per creare un programma

con interfaccia utente molto simile a WinMIPS64, quest’ultimo eseguibile solo

su Microsoft Windows2 , disponibile agli utenti di tutte le piattaforme in quanto

totalmente riprogettato in Java.

Il programma è cresciuto molto rapidamente grazie al continuo supporto dei

vecchi sviluppatori, che lo hanno reso sempre più robusto, e alla crescita del gruppo, alimentato dagli allievi autori di tesine del corso di Laboratorio di Calcolatori.

Tale supporto ha reso, in meno di un anno, il simulatore abbastanza stabile per

essere utilizzato nei corsi di Laboratorio di Calcolatori dell’Università di Catania.

EduMIPS64 non ha ancora raggiunto la versione 1.0 perchè è stata finora assente la FPU (Floating Point Unit), componente essenziale di un simulatore di

CPU. L’obiettivo di questa tesi è la progettazione di un modello che emuli il coprocessore 1 floating point delle moderne architetture MIPS64 e la sua integrazione

in EduMIPS64.

1.2

Contributi

La FPU implementata modella con buona approssimazione concettuale la reale

architettura di un processore MIPS64; tuttavia, per evidenti esigenze di ottimizzazione nei calcoli, sono state impiegate alcune classi già presenti nel Java Runtime

Environment 1.5.

1

2

GPL - General Public License

WinMIPS64 è stato scritto in Microsoft Visual C++

3

CAPITOLO 1. INTRODUZIONE

L’implementazione delle eccezioni sincrone floating point, definite dallo standard IEEE 754, sfrutta il gestore degli interrupt già presente in EduMIPS64 e

sviluppato in un precedente lavoro di tesi.

Tutto il codice scritto per questa tesi sarà integrato nella versione 1.0 del

simulatore, tuttavia, fino all’uscita di questa versione, è possibile provare le nuove

funzionalità apportate scaricando, dal sito ufficiale [3], la versione svn.

1.3

Panoramica della tesi

Nel Capitolo 2 viene discussa l’archittettura delle CPU MIPS64. Si parla,

in particolare, dei dettagli implementativi di registri, memoria e pipeline. Nel

capitolo 3 viene illustrata la floating point unit di questo tipo di CPU e il modo

in cui è implementato lo standard IEEE 754 per che regola l’aritmetica floating

point dei calcolatori. Si approfondiscono le problematiche insite nel pipelining

delle istruzioni floating point, utilizzando come metro di paragone la pipeline del

processore R4000. Nel Capitolo 4 si parla della floating point unit di EduMIPS64

e dei relativi dettagli progettuali. Vengono illustrate le soluzioni alle più comuni

problematiche del pipelining, evidenziando le modifiche apportate al codice del

simulatore per simulare l’esecuzione delle istruzioni floating point. Nell’Appendice

A è presente il manuale utente della floating point unit di EduMIPS64; essa

verrà estratta e inserita, come capitolo, nel Manuale utente di EduMIPS64 per la

versione 1.0 del simulatore.

4

Capitolo 2

L’architettura MIPS64

In questo capitolo viene illustrata l’architettura dei processori MIPS64. Dopo

una breve prospettiva storica che si può approfondire in [12], riguardante l’evoluzione

di queste CPU, vengono illustrati i 32 registri general-purpose e come essi coadiuvano l’indirizzamento in memoria. Nel Paragrafo 2.5 viene fornita una panoramica dell’instruction set ISA MIPS64, mostrando il raggruppamento funzionale delle

istruzioni. Dal Paragrafo 2.6 sono illustrati gli stadi e la struttura di una pipeline a

5 stadi. Successivamente si parla delle problematiche dovute alla sovrapposizione

dell’esecuzione delle istruzioni e come esse vengono risolte limitando parzialmente

la sovrapposizione.

2.1

Storia dei processori RISC

L’architettura dominante nel mercato dei PC è denominata CISC (Complex

Instruction Set Computer): tale nome deriva dalla natura complessa del set di

istruzioni (ISA)1 .

Istruzioni complesse supportano operazioni e strutture dati usate dai linguaggi

1

ISA - Instruction set architecture

5

CAPITOLO 2. L’ARCHITETTURA MIPS64

di alto livello (HLLs)2 , ma la loro lunghezza cresce a dismisura dal momento che

esse devono includere ad esempio gli indirizzi degli operandi in memoria. Tutto

ciò complica la decodifica , lo scheduling e il pipelining delle stesse.

Nei primi anni ’80 si iniziò a pensare a set di istruzioni più semplici e fu coniato

il termine RISC (Reduced Instruction Set Computer), anche se l’obiettivo non era

ridurre il numero di istruzioni, bensı̀ la complessità.

L’origine dei processori RISC si può ricondurre a tre progetti: l’IBM 801, il

RISC di Berkeley, e il MIPS di Standford; essi riscossero grande successo per via

dei vantaggi delle loro performance rispetto alle tradizionali architetture.

L’IBM 801 fu soltanto un progetto sperimentale, mentre gli altri due ebbero

successivi sviluppi. Nel 1980, Patterson e i suoi colleghi dell’Università di Berkeley costruirono due computer chiamati RISC-I e RISC-II, i quali supportavano in

memoria istruzioni a 16 e 32 bit. Nel 1981, Hennessy e i suoi colleghi pubblicarono

una descrizione del MIPS Standford. Quest’ ultimo presentava un efficiente pipelining e uno scheduling compiler-assisted della pipeline, entrambi aspetti originali

dell’architettura MIPS.

L’ISA MIPS si è evoluto nel tempo rispetto all’originale MIPS I, attraverso

l’ISA MIPS V, fino alle attuali architetture MIPS32 e MIPS64. I punti di svolta

si presentarono nel MIPS III, con l’aggiunta di interi e indirizzi a 64 bit, e nelle

versioni MIPS IV-V, con netti miglioramenti delle operazioni floating point, del

codice generato e dello spostamento dati.

L’architettura MIPS32 è basata sull’ISA MIPS II, con l’aggiunta di istruzioni

MIPS III,MIPS IV e MIPS V. Invece l’architettura MIPS64 si basa sull’ISA MIPS

V e gode della compatibilità all’indietro con MIPS32.

2

HLLs - Higher-Level Languages

6

CAPITOLO 2. L’ARCHITETTURA MIPS64

In conclusione, entrambe le architetture forniscono un sostanziale vantaggio nel

compromesso costo/prestazioni risultato dei miglioramenti ottenuti in discipline

contigue: tecnologia VLSI, organizzazione delle CPU, progettazione di sistemi

operativi e compilatori.

2.2

Architettura Load/Store

I processori MIPS usano il design load/store per eliminare i lunghi tempi di

accesso alla memoria. Generalmente occorre più tempo ad eseguire un’operazione

in memoria di quanto ne sia necessario se gli operandi si trovassero già nei registri.

Sfruttando questo principio i processori vengono dotati di diversi registri on-chip

in modo che le operazioni vengano eseguite solo su di essi. L’accesso in memoria

è comunque garantito esclusivamente tramite l’uso di apposite istruzioni di load

e store. Tale tecnica consente di ridurre il numero di accessi alla memoria e

semplificare drasticamente il set di istruzioni.

2.3

Registri

L’architettura MIPS64 è costituita da 32 registri general-purpose (GPR) ognuno di 64 bit, due dei quali vengono usati per funzioni speciali; il registro 0,

chiamato anche $zero, è cablato in hardware e serve a fornire lo zero stesso, mentre il registro 31, detto anche $ra, è usato per memorizzare l’indirizzo di ritorno

di una chiamata a procedura. Altri due registri speciali, LO e HI, vengono usati

nelle operazioni di moltiplicazione e divisione, per memorizzarne i risultati. Nella moltiplicazione tra interi di 64 bit è prodotto un risultato lungo 128 bit, la

cui metà più significativa è posta nel registro HI, e l’altra nel registro LO. Nella

7

CAPITOLO 2. L’ARCHITETTURA MIPS64

divisione intera, invece, il quoziente è memorizzato in LO, e il resto nel registro

HI.

È pratica comune, come si è visto per i registri speciali, usare dei nomi

mnemonici o alias in luogo del numero del registro. Gli alias per i 32 registri

general-purpose sono nell’ordine: zero, at, v0, v1, a0, a1, a2, a3, t0, t1, t2, t3, t4,

t5, t6, t7, s0, s1, s2, s3, s4, s5, s6, s7, t8, t9, k0, k1, gp, sp, fp, ra. Convenzionalmente, si consiglia di usare i registri $v0 e $v1 per ritornare i risultati da una

procedura, e i registri da $a0 ad $a3 per passare, al più, quattro argomenti alle

procedure; i rimanenti argomenti vengono passati mediante stack. I registri da $t0

a $t7 sono temporanei e non dovrebbero essere riservati a chiamate di procedura,

al contrario dei registri da $s0 ad $s7, che, essendo callee-saved, sono riservati a

questo scopo. L’ultimo fra i più importanti è $sp, che punta alla cima dello stack.

Per l’utilizzo degli altri registri consultare [10].

2.4

Indirizzamento

La modalità di indirizzamento si riferisce a come gli operandi sono specificati.

Nelle architetture MIPS l’indirizzo di memoria di un operando è calcolato sommando il contenuto di un registro ad una costante. L’indirizzo si può generalizzare

con la notazione offset(base), dove base è il nome del registro nel formato Rx3 o

$alias, al quale verrà sommato un offset, cioé un numero con segno di 16 bit.

Segue un esempio di un’istruzione dell’ISA MIPS64 che consente il caricamento

dei dati della prima cella di memoria sul registro R8:

LD $t0, 0($zero);per i nomi degli alias vedere 4.2.

L’accesso in memoria è regolamentato dai vincoli di allineamento. La memoria

3

x - intero compreso tra 0 e 31

8

CAPITOLO 2. L’ARCHITETTURA MIPS64

è composta da doubleword (64 bit). Ogni doubleword è composta da due word (32

bit) affiancate, formate a loro volta da due halfword (16 bit) ciascuna. Le halfword,

infine, sono costituite ognuna da due byte. In funzione di queste definizioni, gli

accessi alle doubleword devono prevedere indirizzi divisibili per 8, quelli alle word

divisibili per 4, quelli alle halfword per 2 e quelli ai byte indirizzi qualunque entro

i limiti di dimensione della memoria.

Nonostante ne sia sconsigliato l’utilizzo, se non per applicazioni particolari,

gli istruction set MIPS32 e MIPS64 mettono a disposizione alcune istruzioni di

load-store non allineato che riguardano solo doubleword e word: LWL, LWR, SWL,

SWR, LDL, LDR, SDL, SDR.

2.5

Instruction set

Come accennato in precedenza, i processori RISC hanno degli istruction set

più semplici rispetto alle macchine CISC. Ciò è dovuto a diversi fattori, tra cui:

il fatto che tutte le operazioni sui registri ne cambiano interamente il valore; il

fatto che le sole operazioni che accedono alla memoria sono le load e le store; il

numero limitato di istruzioni e l’uniformità della loro lunghezza, fissata a 32 bit

per i processori MIPS. Tutti questi aspetti consentono di realizzare solo pochi

formati predefiniti per le istruzioni.

2.5.1

Formati delle istruzioni

L’ISA MIPS64 prevede tre formati di istruzioni, illustrati in Figura 2.1:

• Immediate (I-type): È il formato usato da tutte le istruzioni load-store. Il

valore immediato è uno short, e viene usato sia nelle operazioni aritmetiche, alle quali si vuole fornire come operando un piccolo numero senza

9

CAPITOLO 2. L’ARCHITETTURA MIPS64

caricarlo prima in un registro, sia nelle istruzioni di salto, che possono incrementare/decrementare il PC di un offset a 18 bit, ovvero saltare in una

finestra di 128 Kbytes(PC-relative branches). Per evitare questa limitazione

nel salto si usano le istruzioni J-Type.

• Jump (J-type): Un campo di 26 bit di questo formato viene combinato con

i bit di ordine più alto del PC per ottenere l’indirizzo assoluto. Formando

l’indirizzo a cui saltare mediante questa concatenazione, piuttosto che sommare un offset al PC, si ha il vantaggio di muoversi in una regione di 256

MB (PC-region branch).

• Register (R-type): È il formato usato dalle istruzioni aritmetiche e logiche,

nonché dalle istruzioni di salto, che utilizzano un registro contenente l’indirizzo di memoria a cui saltare.

Figura 2.1: Formati dell’ISA MIPS64

10

CAPITOLO 2. L’ARCHITETTURA MIPS64

Campo

Descrizione

Dim. bit

opcode

codice binario dell’istruzione

6

rd

registro di destinazione

5

rs

registro sorgente

5

rt

registro target (sorgente o destinazione)

5

immediate immediato con segno usato per operandi logici,

aritmetici con segno, offset e salti PC-relative

16

inst index fornisce i 26 bit che vengono traslati di due a

sinistra per dare i 28 bit meno significativi

dell’indirizzo di destinazione del salto.

26

sa

entità dello shift

5

function

usato per specificare funzioni all’interno

dell’opcode SPECIAL

6

Tabella 2.1: Campi delle istruzioni

2.5.2

Raggruppamento per funzionalità

Le istruzioni dell’ISA MIPS64 possono anche essere raggruppate secondo questi

gruppi funzionali:

- Load e Store

- Computazionali

- Jump e Branch

- Multiformi

- Coprocessore

per ulteriori approfondimenti sulle singole istruzioni una lista completa è disponibile in [8].

Load e Store

Le istruzioni Load e Store sono le uniche a poter spostare dati dalla memoria ai registri e viceversa. Per ogni unità di dati (si veda il paragrafo 2.4) es11

CAPITOLO 2. L’ARCHITETTURA MIPS64

istono almeno un’istruzione di caricamento con segno, una senza segno, e una di

memorizzazione dell’unità stessa.

Alcune istruzioni speciali consentono di selezionare le modalità di indirizzamento (per esempio, SDXC1 nella FPU) e di effettuare aggiornamenti atomici delle celle di memoria (per esempio, lettura-modifica-scrittura - LL/SC) per

implementare meccanismi di sincronizzazione come semafori e mutex.

Computazionali

A questa categoria appartengono le istruzioni che eseguono l’aritmetica a complemento a 2 su interi rappresentati con questa notazione. Le istruzioni di somma

e sottrazione in cui compare il termine ”unsigned”, contrariamente al significato

del termine, non sono soggette alla verifica dell’overflow.

Sono incluse anche delle versioni unsigned di divisione e moltiplicazione, e una

serie di istruzioni che effettuano operazioni logiche e di shift. Le operazioni logiche

non sono sensibili alla lunghezza del registro.

Le istruzioni computazionali possono essere raggruppate in tre categorie: ALU

immediate, ALU a due operandi, ALU a tre operandi, istruzioni di shift, istruzioni

di divisione e moltiplicazione. L’operando immediato è trattato come un valore

con segno per le istruzioni aritmetiche e di confronto, e come valore logico per le

istruzioni di questo tipo.

Jump e Branch

Le istruzioni che consentono di effettuare un salto PC-relative (si veda il paragrafo 2.5) sono condizionali, in quanto è possibile definire un test la cui verità

dà il via al salto, mentre quelle che saltano in una PC-region sono dette uncon-

12

CAPITOLO 2. L’ARCHITETTURA MIPS64

ditional, e la maggior parte della loro lunghezza è riservata alla memorizzazione

dell’indirizzo di destinazione.

L’ultima tipologia è il salto assoluto, praticato sia sostituendo al PC l’indirizzo

in un registro puntato dall’istruzione, sia eseguendo, oltre a questa azione, il

salvataggio in un registro (di solito R31) del PC, per consentirne successivamente

il recupero a seguito di una chiamata ad una procedura.

I salti hanno un ritardo architetturale di un’istruzione, e l’istruzione immediatamente dopo quella di salto si dice essere nel branch delay slot. Se l’istruzione di

salto è una branch, allora quella nel delay slot verrà anch’essa eseguita; se quella

di salto è un’istruzione branch-likely, l’istruzione nel delay slot non verrà eseguita

se il salto non avverrà (branch not taken).

Varie

Appartengono a questo gruppo le istruzioni di eccezione (SYSCALL, TRAP

e BREAK), quelle di spostamento condizionale, ed infine l’istruzione NOP. Le

istruzioni di eccezione trasferiscono il controllo al gestore delle eccezioni nel kernel.

Esistono due tipi di eccezioni: conditional e unconditional. Le prime vengono

lanciate dalle istruzioni di trap (per esempio TEQ,TGE, TLT), le seconde vengono

lanciate dalle system call e dalle istruzioni di breakpoint (BREAK,SYSCALL).

L’istruzione SYSCALL non definisce con precisione i servizi che il sistema operativo deve fornire, ma essa contiene un codice recuperabile dal gestore delle

eccezioni per invocare un’opportuna system call. Per ulteriori informazioni sulla

SYSCALL implementata in EduMIPS64 consultare [1].

L’ISA MIPS64 include istruzioni per lo spostamento condizionato di un GPR4

4

GPR - General Purpose Register

13

CAPITOLO 2. L’ARCHITETTURA MIPS64

in un altro, basato sul valore di un terzo GPR (per esempio MOVF,MOVZ). Per

gli spostamenti condizionali floating point si veda il Paragrafo A.6.

L’istruzione NOP è attualmente codificata come una istruzione all-zero, ed

effettua una non-operazione. È interpretata dall’hardware come SLL r0,r0,0 e

viene generalmente usata per riempire i delay slots e le sequenze di allineamento.

Coprocessore

I coprocessori sono unità di esecuzione alternative alla CPU. L’architettura

MIPS ne prevede quattro numerati da 0 a 3 (CP0 a CP3); essi vengono abilitati

mediante operazioni privilegiate fornite dal System Control Coprocessor (CP0).

Il coprocessore 0 serve, dunque, al controllo del sistema, mentre gli altri tre sono

usati per la FPU.

Le istruzioni coprocessore si dividono in due gruppi: istruzioni load e store,

che hanno il compito di scrivere e leggere i registri di un dato coprocessore (per

esempio LDCz,SDCz con z=1 o z=2), e le istruzioni coprocessor-specific, definite

interamente dal coprocessore in uso.

2.6

Pipelining

Ciascuna istruzione dell’ISA MIPS64, nell’ipotesi in cui non avvenisse il pipelining, verrebbe elaborata in 5 cicli di clock successivi del processore:

1. Instruction Fetch(IF): il PC viene prima inviato alla memoria per prelevare l’istruzione corrente, poi aggiornato aggiungendo 4 al suo valore (ogni

istruzione è lunga 4 byte).

2. Instruction Decode(ID): L’istruzione è decodificata, e vengono rilevati i registri sorgenti dal register file. In questo ciclo viene effettuato il test di

14

CAPITOLO 2. L’ARCHITETTURA MIPS64

uguaglianza per un eventuale salto; viene inoltre esteso, se richiesto, il segno

dell’offset, e calcolata la destinazione del possibile salto aggiungendo l’offset

al PC già incrementato.

3. Execution(EX): L’ALU lavora sugli operandi preparati nel precedente ciclo.

Se l’istruzione comporta l’accesso in memoria, è calcolato l’ indirizzo effettivo come somma di base e offset; se ha due registri sorgenti, viene letto

l’opcode ed effettuata la relativa operazione sugli operandi; se, infine, presenta un immediato e un registro sorgente, è necessario estendere il segno

dell’immediato prima di effettuare l’operazione.

4. Memory Access (MEM): Se l’istruzione è una load, la memoria effettua una

lettura usando l’indirizzo effettivo calcolato nel ciclo precedente; se è una

store, invece, scrive i dati del registro sorgente nella locazione all’indirizzo

calcolato.

5. Write-back (WB): In questo ciclo, per le istruzioni che implicano la scrittura

sui registri e per quelle di caricamento, si effettua la scrittura dei risultati.

Per l’esecuzione in pipeline di istruzioni che effettuano operazioni aritmetiche

su operandi in virgola mobile, di per sè più complesse rispetto alle operazioni intere, che richiedono un solo ciclo di clock per lo stadio EX, si usufruisce delle varie

unità funzionali della floating point unit residente su un coprocessore dedicato.

In particolare, l’addizionatore esegue lo stadio EX di somme e sottrazioni in 4

cicli, il moltiplicatore esegue il prodotto in 7 cicli, e il divisore effettua la divisione

in 24 cicli (si veda la Figura 2.2). Nel capitolo successivo si approfondiranno le

problematiche del pipelining di istruzioni floating point.

15

CAPITOLO 2. L’ARCHITETTURA MIPS64

Figura 2.2: Pipeline di EduMIPS64

2.6.1

Implementazione di una pipeline a cinque stadi

Nonostante l’esecuzione di ogni istruzione continui ad impiegare 5 cicli per

essere completata, si può apportare un miglioramento all’algoritmo di esecuzione

precedente sfruttando il fatto che, durante ogni ciclo di clock, l’hardware può

iniziare ad eseguire una nuova istruzione, e contemporaneamente delle porzioni

diverse di altre 5, purché le risorse usate non siano le stesse. Ad esempio, l’ALU

non può eseguire il calcolo di un indirizzo di memoria ed effettuare contemporaneamente una sottrazione.

In base a quanto detto, si possono fare le seguenti considerazioni:

- dal momento che gli accessi in memoria avvengono sia nello stadio IF, in cui

vengono prelevate le istruzioni, che in MEM, in cui si opera la scrittura/lettura dei dati, occorre dividere la memoria dati da quella delle istruzioni.

- Il register file, o banco registri, è usato sia in ID che in WB, rispettivamente

in lettura e in scrittura; per tale ragione occorre separare le due operazioni,

16

CAPITOLO 2. L’ARCHITETTURA MIPS64

realizzando nel primo mezzo ciclo di clock la scrittura, e nel secondo mezzo

ciclo la lettura del file.

- Per iniziare una nuova istruzione ad ogni tick di clock, durante lo stadio

IF, si deve incrementare il PC, e calcolare l’indirizzo di destinazione del

salto che si potrebbe verificare in ID. Un altro problema, che sarà affrontato

successivamente, è che, nel caso di istruzione di salto, il PC verrà modificato

soltanto nello stadio ID.

- Per assicurare che le istruzioni in stadi differenti della pipeline non interferiscano tra loro, vengono usati dei pipeline registers (per esempio EX/MEM,

MEM/WB), che riportano i risultati dell’esecuzione di uno stadio come

ingressi per il successivo stadio.

- La realizzazione di una pipeline incrementa il numero di istruzioni completate per unità di tempo, ma non riduce il tempo di esecuzione di una

singola istruzione. L’idea di creare una sovrapposizione nell’esecuzione delle

istruzioni, risalente al 1985, prende il nome di Instruction-Level Parallelism

(ILP); si vedrà tuttavia nel paragrafo 2.6.3 che, per via degli hazard, le

prestazioni ottenute con questa tecnica sono inferiori a quelle che si otterrebbero con una pipeline ideale (un ciclo per istruzione ovvero CPI=1).

2.6.2

Dipendenze

Per comprendere fino a che punto l’Instruction-Level Parallelism può essere

sfruttato, occorre determinare come un’istruzione può dipendere da un’altra.

Soltanto se non c’è alcuna dipendenza le istruzioni possono essere eseguite let-

17

CAPITOLO 2. L’ARCHITETTURA MIPS64

teralmente in parallelo, altrimenti si ha una parziale sovrapposizione e dev’essere

mantenuto l’ordine di esecuzione.

Si hanno tre tipi di dipendenza:

• Dati: quando il risultato prodotto da un’istruzione dev’essere usato da un’altra istruzione, si può allargare questo principio ad n istruzioni, creando una

catena di n-1 dipendenze dati. Nell’esempio sottostante si evince la dipendenza della DSUB dalla DADD: DSUB non può leggere gli operandi (R1,R5)

finché il valore memorizzato in R1 non diventi valido (DADD raggiunge lo

stadio WB e scrive R1).

DADD R1 , R2 , R3

DSUB R4 , R1 , R5

• Nomi: quando due istruzioni usano lo stesso registro o la stessa cella di

memoria nonostante non ci sia un flusso dati tra esse. Si ha un’antidipendenza

dati se un’istruzione deve leggere un registro/cella appena scritto da un’altra istruzione, una dipendenza di output se due istruzioni devono scrivere

sullo stesso registro/cella. In entrambi i casi l’ordine di esecuzione delle

istruzioni dev’essere mantenuto, per garantire, rispettivamente, di aver letto il valore appena aggiornato, e scritto per ultimo il registro/cella. Anche

se molto simile alla dipendenza dati, la dipendenza nomi può essere risolta con una tecnica chiamata register renaming, nella quale si utilizzano dei

registri non permanentemente associati all’architettura, ma dinamicamente

allocati quando richiesto.

Nell’esempio che segue, scritto in pseudocodice assembly MIPS, è illustrata

una dipendenza nomi e come questa può essere risolta rinominando il registro

in conflitto;

18

CAPITOLO 2. L’ARCHITETTURA MIPS64

MUL

ADD

ADD

DIV

R2 , R2 , R3

R4 , R2 , 1

R2 , R3 , 1

R5 , R2 , R4

;

;

;

;

R2

R4

R2

R5

=

=

=

=

R2

R2

R3

R2

∗

+

+

/

R3

1

1

R4

L’istruzione 3 non può andare avanti finché la 1 non ha terminato, perchè

c’è una dipendenza di output fra le istruzioni 1 e 3 (entrambe scrivono su

R2). Esiste anche un’antidipendenza dati tra le istruzioni 2 e 3 (l’istruzione

3 sovrascrive uno degli argomenti della 2). Se rinominasse il registro R2,

creandone tre versioni cronologiche diverse (R21,R22,R23)

MUL

ADD

ADD

DIV

R21 , R20 , R3

R4 , R21 , 1

R22 , R3 , 1

R5 , R22 , R4

l’istruzione 3 potrebbe eseguire subito, perchè si servirebbe di un registro diverso da quello delle istruzioni 1 e 2. Per ulteriori approfondimenti sui metodi di implementazione di questa tecnica, come i buffer di riordino, consultare

[2]

• Controlli: quando l’esecuzione di un’istruzione dipende dal verificarsi di

qualche condizione. Un semplice esempio usato in [5] ne agevola la comprensione:

i f p1 {

S1 ;

}

i f p2 {

S2 ;

}

S1 è control dipendent da p1, ed S2 è control dipendent da p2, ma non da p1.

L’esecuzione delle istruzioni nell’ordine assicura, dunque, che un’istruzione

che si trova prima di un salto condizionato (branch) venga eseguita prima

19

CAPITOLO 2. L’ARCHITETTURA MIPS64

del salto stesso; analogamente, un’istruzione che è control dipendent da un

branch non viene eseguita finché il salto non va nella sua direzione.

2.6.3

Hazard

Un hazard si può definire come una situazione di allarme per cui, essendosi

verificata una dipendenza fra istruzioni molto vicine, se si continua ad eseguire le

istruzioni con la massima sovrapposizione prevista dal pipelining c’è il rischio di

un errore durante il flusso di esecuzione del programma

In queste circostanze può essere necessario introdurre uno stallo per alcune

istruzioni fino a quando l’hazard non venga risolto. Quando un’istruzione subisce

uno stallo, anche quelle emesse successivamente devono essere fermate, mentre le

istruzioni emesse prima possono continuare l’esecuzione.

Hazard strutturale

Un hazard strutturale si verifica quando due o più istruzioni si contendono

una risorsa non duplicabile, per cui la pipeline deve fermare alcune istruzioni

finchè l’unità richiesta non diventi disponibile. Questo tipo di hazard si verifica

sia per le unità funzionali che non sono fully-pipelined, ovvero non applicano il

pipelining delle istruzioni in quanto ne possono elaborare una alla volta (il divisore

floating point ne è un esempio), sia per i riferimenti contemporanei alla memoria

condivisa. Nel paragrafo 4.4 vengono approfonditi i dettagli progettuali della

pipeline, tenendo in grande considerazione l’eventualità di hazard strutturali.

Data hazard

Un data hazard si verifica quando, in presenza di una dipendenza dati, potrebbe

essere cambiato l’ordine di accesso agli operandi coinvolti nella dipendenza. Se

20

CAPITOLO 2. L’ARCHITETTURA MIPS64

questo si verificasse, l’ordine di esecuzione delle istruzioni differirebbe rispetto a

quello di un processore che non implementa la pipeline. I data hazard, a seconda

dell’ordine di lettura o scrittura degli operandi, si distinguono in tre categorie:

1. RAW (read after write): è l’hazard più comune, corrispondente ad una

dipendenza dati. Si verifica quando un’istruzione legge una sorgente prima

che questa venga scritta, ottenendone cosı̀ il valore non aggiornato.

2. WAW (write after write): Un’istruzione scrive un operando non attendendo

che lo faccia prima un’altra istruzione che la precede, nel registro viene

scritto cosı̀ il valore più obsoleto.

Questo hazard corrisponde ad una dipendenza di output e si verifica, come

si vedrà nel capitolo successivo, con l’utilizzo delle unità funzionali della

floating point unit. Un altro caso è quando si applica il riordinamento delle

istruzioni, approfondito in [5].

3. WAR (write after read): Si verifica quando un’istruzione scrive una destinazione prima che questa venga letta da un’istruzione che la precede:

quest’ultima legge cosı̀ il nuovo valore. Tale hazard corrisponde al caso

di antidipendenza, ma non può mai verificarsi nelle pipeline che prevedono

le letture in ID e le scritture in WB.

Control hazard

Quando un’istruzione di branch viene eseguita, il valore del PC potrebbe essere incrementato soltanto di 4 (branch not taken - salto non avvenuto); oppure,

potrebbe assumere il valore dell’indirizzo dell’istruzione puntata dal salto (branch

taken). Se il branch è taken si effettua il fetch dell’istruzione puntata5 ; ciò in5

L’esecuzione dello stadio IF è in sè uno stallo

21

CAPITOLO 2. L’ARCHITETTURA MIPS64

vece non è necessario se il branch è not taken, in quanto il fetch dell’istruzione

successiva è implicito nella dinamica della pipeline.

22

Capitolo 3

La floating point unit dei

processori MIPS64

In questo capitolo, dopo una breve panoramica sull’aritmetica floating point,

che può essere approfondita in [9, 11, 4], e dello standard IEEE 754, si discute

dell’architettura della floating point unit di un processore MIPS64, e il modo in

cui essa si adegua al suddetto standard. Nel Paragrafo 4.2 si parla dei registri

floating point, del registro di controllo FCSR e di altri registri speciali della FPU.

Nel Paragrafo 3.5 vengono illustrate solo le istruzioni floating point di interesse

per questa tesi, raggruppate secondo categorie funzionali. Dopo questa panoramica, nel Paragrafo 3.6, vengono introdotte le problematiche relative al pipelining

delle istruzioni floating point. Alla fine del capitolo si fa cenno alla pipeline del

processore MIPS R4000 [6].

3.1

Numeri in virgola mobile

In ambito scientifico si è soliti trattare numeri molto grandi o molto piccoli,

che non possono essere manipolati con l’aritmetica in virgola fissa1 . Mediante

la notazione scientifica, lo stesso numero può essere scritto in modi diversi: per

1

Quella che prevede la virgola a destra della cifra meno significativa

23

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

esempio la distanza della Luna dalla Terra in Km si può esprimere sia come

38.44 × 104 , che come 3.844 × 105 (3.844 è la mantissa e 5 l’esponente);

quest’ultima forma è detta normalizzata. I calcolatori memorizzano i numeri in

virgola mobile in un’equivalente notazione scientifica con base 2; lo stesso numero

viene dunque arrotondato e trattato da un computer come 1.4663696 × 218 .

Dal momento che, in decimale, la mantissa si può espandere in serie di potenze

P∞

( n=0 an xn ), ponendo la variabile argomento x = 10−1

1.4663696 = 1 + 4 × 10−1 + 6 × 10−2 + 6 × 10−3 + 3 × 10−4 + 6 × 10−5 + ...

analoga cosa si può fare per scriverne l’equivalente binario, ponendo x = 2−1 .

1.01110111011001 = 1 + 0 × 2−1 + 1 × 2−2 + 1 × 2−3 + 1 × 2−4 + 0 × 2−5 + ...

Nel paragrafo successivo si vedrà la rappresentazione di questo numero secondo

lo standard IEEE 754.

3.2

Standard IEEE 754-1985

Circa trent’anni fa, nell’ambito dell’aritmetica floating point implementata

nel software dei microprocessori, regnava la totale anarchia. Venivano utilizzate

numerose rappresentazioni dei numeri in virgola mobile, con diverse grandezze,

precisioni, modi di arrotondamento ed eccezioni. Nel 1977 il Prof. W.Kahan

dell’università di Berkeley, ottenne il permesso a partecipare alla realizzazione

di uno standard che mettesse fine a tale confusione, preparò una bozza chiamata ”K-C-S”. Dopo un’estenuante battaglia con la DEC, che aveva già messo sul

mercato i processori VAX, la bozza fu sottoposta a varie revisioni di compromesso, fino a quando il gruppo di lavoro 754 la inviò al comitato degli standard

24

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

dei microprocessori della IEEE. Denominata IEEE 754-1985 for Binary FloatingPoint Arithmetic, la bozza rettificata divenne lo standard de facto, usato tuttora

nell’aritmetica floating point.

3.2.1

Memorizzazione di un numero floating point

Lo standard IEEE 754 specifica tre formati di numeri floating point: single

(32 bit), double (64 bit) e double-extended (maggiore di 10 byte). Come visto nel

precedente paragrafo, ogni numero è rappresentato con la notazione

mantissa × 2esponente

ma l’esponente non è mai memorizzato come numero con segno, bensı̀ polarizzato.

Con tale tecnica viene aggiunta all’esponente una costante di polarizzazione(bias),

che consente di traslare nel semiasse positivo dei numeri interi l’intervallo di valori

che l’esponente può assumere2 . Cosı̀ facendo, il confronto fra numeri floating point

può essere realizzato con lo stesso hardware che manipola i numeri interi.

Figura 3.1: Formato dei numeri FP in doppia precisione

Figura 3.2: Formato dei numeri FP in singola precisione

I numeri nel formato IEEE normalizzati soddisfano la relazione 1 ≤ mantissa < 2.

Sfruttando tale proprietà, la mantissa si presenta sempre nella forma 1, xx..x3 , per

cui si può non salvare il suo bit più significativo poiché vale sempre 1(hidden bit).

2

Il valore di esponente 1 è il più negativo assumibile con lo spazio dati a disposizione

Per errori di traduzione mantissa è intesa sia col suo vero significato (significand ), sia come

la sua parte decimale che è quella memorizzata nei formati IEEE754(fraction)

3

25

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

Campo della mantissa

Campo dell’esponente

Campo del segno

Numero memorizzato

Valore decimale Valore binario

0.4663696

01110111011001000000000

18 + 127

10010001

0

0

1.4663696 × 218

0 10010001 01110111011001000000000

Tabella 3.1: Dati di conversione decimale/single

Per scrivere in formato single il numero del precedente esempio, la cui mantissa binaria è 1.01110111011001 e l’esponente 18, tenendo conto che la costante

di polarizzazione per i single è 127 e il numero dev’essere espresso nella forma

1.mantissa × 2esponente−127 , si hanno i risultati della Tabella 3.1.

Bit di precisione

Esponente massimo (Emax )

Esponente minimo (Emin )

Bias

Single Single extended

24

≥ 32

127

≥ 1023

-126

≤ −1022

127

Double

53

1023

-1022

1023

Double extended

≥ 64

≥ 16383

≤ −16382

Tabella 3.2: Parametri di formato dello standard IEEE 754

3.2.2

Valori speciali

I numeri più piccolo e più grande assumibili dall’esponente polarizzato4 (per i

single 0 e 255) vengono usati per rappresentare valori speciali. Quando l’esponente

polarizzato vale 255, se il campo mantissa contiene solo zeri, il numero rappresenta l’infinito positivo o negativo a seconda del segno, mentre se esso contiene un

valore diverso da zero, il numero rapprenta un NaN (Not a Number), usato per

fornire un risultato alle operazioni matematiche non valide (per esempio 0 × ∞

oppure 00 ). Nei processori MIPS il bit più significativo della mantissa ne determina la tipologia (Quit NaN oppure Signalling NaN). Quando entrambi i campi

4

L’esponente polarizzato è detto biased in quanto è ottenuto dalla somma tra l’esponente e

la costante di polarizzazione(bias)

26

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

dell’esponente polarizzato e della mantissa valgono zero il numero rappresenta lo

zero5 . Ii numeri denormals rappresentano un ultimo tipo di valore speciale. In

molti sistemi floating point, un numero più piccolo di 1.0 × 2Emin non può essere rappresentato, e dunque considerato uguale a zero. Lo standard IEEE 754

prevede la rappresentazione di questi numeri, la cui mantissa è minore di uno,

per avvicinarsi all’eccezione di underflow (si veda il paragrafo 3.2.3) in modo

graduale.

I numeri denormals vengono rappresentati con la notazione 0.mantissa × 2Emin ,

in essi il campo dell’esponente vale zero, mentre la mantissa qualunque valore

diverso da zero.

È da notare che, se l’esponente non polarizzato appartiene all’intervallo [Emin , Emax ],

la mantissa è normalizzata, (scritta nella forma 1,xx..x) e il bit nascosto vale 1;

mentre per poter rappresentare i numeri denormals, il bit nascosto è 0 e il campo

dell’esponente assume il valore più piccolo in assoluto (Emin − 1), che polarizzato

equivale a zero.

Campo esponente Campo mantissa Valore rappresentato

e = Emin − 1

m=0

±0

e = Emin − 1

m 6= 0

0.m × 2Emin

Emin ≤ e ≤ Emax

–

1.m × 2e

e = Emax + 1

m=0

±∞

e = Emax + 1

m = 0xx..x, m 6= 0

Quiet NaN

e = Emax + 1

m = 1xx..x

Signalling NaN

Tabella 3.3: Rappresentazione dei valori speciali

5

Anche se ciò può sembrare banale si rifletta sul fatto che non esiste soluzione all’equazione

1, .. × 2x = 0

27

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

3.2.3

Eccezioni

Una delle più importanti regole fornite dallo standard IEEE 754 è che il

calcolo, se espressamente voluto, può continuare nonostante sia stato prodotto un

risultato ”eccezionale”:

- Indeterminato: prodotto, per esempio, da operazioni del tipo

0

0

oppure 0×∞

- Infinito: come per il risultato di una divisione per zero

- Troppo grande in valore assoluto: una moltiplicazione tra numeri grandi

potrebbe avere per risultato un numero non rappresentabile data la sua

grandezza (overflow)

- Troppo piccolo in valore assoluto: la rappresentazione di un tale numero è

problematica per via della perdita di precisione (underflow)

- Inaccurato: come per la rappresentazione di

1

3

che necessita di un arroton-

damento tra i vari possibili

Le cinque eccezioni previste dallo standard sono: operazione non valida, divisione

per zero (Divide by zero), underflow, overflow e numero inesatto(Inexact).

Operazione non valida

Alcune delle operazioni aritmetiche non valide che forniscono come risultato

NaN sono:

√

x, x < 0

0×∞

∞

∞

0.0

0.0

∞−∞

Nella floating point unit dei processori MIPS64 è utilizzato uno speciale registro chiamato FCSR, descritto nel paragrafo 3.4.1, il quale memorizza delle

28

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

informazioni sullo stato delle eccezioni. In esso si trovano le flag di abilitazione

delle trap relative alle 5 eccezioni, e le flag che indicano se qualcuna di queste si

è mai verificata e non è stata ancora rimossa. Quando la flag dell’FCSR relativa

all’attivazione della trap dell’eccezione Operazione non valida è posta a 0, nessuna

trap si verifica, e il valore QNaN dev’essere fornito come risultato.

Divisione per zero

Questa eccezione si verifica quando, in una divisione, il divisore è zero e il

dividendo diverso da zero. Se la relativa trap non è attiva viene generato un

valore infinito con segno.

Underflow

Come visto nella precedente sezione, i numeri dell’intervallo ±1.0 × 2Emin sono

rappresentati usando mantisse minori di uno. Tale processo, che inizia con la

formazione di numeri denormals, è chiamato underflow graduale e termina con

l’eccezione stessa quando si raggiunge il più piccolo numero rappresentabile in

valore assoluto.

Overflow

L’eccezione di overflow è segnalata quando il risultato di un’operazione è più

grande di quello che può essere rappresentato, ciò è dovuto all’intervallo ristretto

dell’esponente. Tale eccezione non viene segnalata quando uno degli operandi è

infinito per via della correttezza dell’aritmetica tra infiniti.

Numero inesatto(Inexact)

Viene segnalata quando il risultato di un’operazione aritmetica ha infinite

cifre decimali (per esempio 13 ), esso dunque dev’essere arrotondato. La trap del29

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

l’eccezione inexact è disabilitata e la relativa flag ignorata dalla maggior parte del

software che lavora con numeri floating point, per tale ragione è stato ritenuto

non necessaria la sua implementazione in EduMIPS64.

3.2.4

Arrotondamenti

Le rappresentazioni floating point hanno una base β e una precisione p. Se

β = 10 e p = 3 il numero 0.1 verrebbe rappresentato come 1.00 × 10−1 . Se β = 2

e p = 24 lo stesso numero non può essere rappresentato esattamente, ma in modo

approssimato (1.10011001100110011001101 × 2−4 ), dove per approssimazione si

intende una funzione che dipende dalla modalità di arrotondamento e dalle cifre

successive alla p-esima della mantissa.

Lo standard IEEE 754 prevede 4 modalità di arrotondamento (Hp:β = 10, p = 1):

- Al più vicino: arrotonda al più vicino valore rappresentabile. Se la distanza

da due valori rappresentabili è la stessa, il risultato è arrotondato a quello

pari (2.6 ∼

= 3, 3.4 ∼

= 3, 4.5 ∼

= 4, 5.5 ∼

= 6).

- Verso lo zero: arrotonda al numero, preso in valore assoluto, più vicino

allo zero; ciò equivale a troncarne la parte decimale (−3.9 ∼

= −3, −3.1 ∼

=

−3, 4.1 ∼

= 4, 4.9 ∼

= 4)

- Verso l’infinito positivo: arrotonda al valore rappresentabile più vicino ma

non più piccolo del numero da arrotondare (−2.8 ∼

=

= −2, 6.1 ∼

= −2, −2.1 ∼

7, 6.9 ∼

= 7).

- Verso l’infinito negativo: arrotonda al valore rappresentabile più vicino ma

non più grande del numero da arrotondare (−2.8 ∼

= −3, −2.1 ∼

= −3, 6.1 ∼

=

6, 6.9 ∼

= 6)

30

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

3.2.5

Operazioni floating point

Le operazioni possono essere eseguite soltanto fra numeri floating point dello

stesso tipo, altrimenti il risultato è UNPREDICTABLE. Supponiamo di rappresentare il generico numero floating point in base 2 con la notazione

Fi = (−1)Si · 1.f · 2Ei −bias

dove Si è il segno del numero floating point, f è la parte decimale (fraction)

della mantissa Mi , ed Ei = Eisign + bias è l’esponente polarizzato. Si noti che

Eisign è l’esponente naturale (con segno). Infine sia p il numero di bit necessario

a rappresentare la mantissa, compreso il bit nascosto.

Moltiplicazione

Si vuole calcolare il prodotto

F3 = F1 × F2 = (−1)S1 · (−1)S2 · (M1 · M2 ) × 2E1 +E2 −bias

Si calcola E3 sommando gli esponenti polarizzati E1 ed E2 , si sottrae successivamente la costante di polarizzazione (per i single 127, per i double 1023). Ci si può

convincere di tale operazione in quanto

E3 = E3sign + bias = E1sign + E2sign + bias = E1sign + bias + E2sign + bias − bias = E1 + E2 − bias

Se i segni S1 ed S2 concordano allora S3 è positivo, altrimenti è negativo. Si

moltiplicano le due mantisse M1 ed M2 , ottenendo una mantissa di 2p bit che

dovrà essere arrotondata a p bit.

Si normalizza il prodotto se il bit più significativo (carry out bit o Cout ) è 1,

ovvero si sposta la virgola a sinistra6 incrementando l’esponente. Si valuta dunque

se si è verificata una condizione di eccezione.

6

Ciò equivale a traslare i bit a destra (right shift)

31

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

Si arrotonda il prodotto se l’espressione logica R(M0 +S) è vera, dove M0 ed R

rappresentano il p−esimo e il (p + 1)esimo bit del prodotto normalizzato partendo

dall’estrema sinistra della mantissa, e il bit S (sticky) è la somma logica di tutti

i bit alla destra di R. Se la condizione di arrotondamento è vera, viene aggiunto

1 al p−esimo bit del prodotto normalizzato. In quest’ultimo caso, se i bit più

significativi sono pari a 1, l’arrotondamento può generare un riporto, quindi si

deve rifare la normalizzazione.

Figura 3.3: Mantisse prima della moltiplicazione

Figura 3.4: Risultato del prodotto fra le mantisse prima della normalizzazione

Figura 3.5: Prodotto normalizzato prima dell’arrotondamento

Addizione o sottrazione

Si effettua il confronto degli esponenti e se ne calcola il valore assoluto della

differenza. Si tiene conto che l’esponente più grande è quello più probabile per il

risultato.

32

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

Si sposta il punto decimale della mantissa del numero col minore esponente di

un numero di posti pari alla differenza tra i due esponenti. Due dei bit traslati e

non più visibili della mantissa allineata vengono chiamati guardia (G) e round (R).

Cosı̀ per mantisse di p bit, l’effettiva grandezza delle mantisse allineate dev’essere

p + 2 bit. Si aggiunge un terzo bit chiamato sticky (S) all’estrema destra della

mantissa allineata; questo bit è dato dalla somma logica di tutti i bit alla destra

di R.

Si sommano (sottraggono per la sottrazione) le due mantisse usando un sommatore di p + 3 bit. Si chiami il risultato di tale operazione SOMMA.

Si controlla il bit più significativo di SOMMA per un eventuale riporto durante

l’addizione. In questo caso, si sposta la virgola di SOMMA incrementando l’esponente di 1. Per la sottrazione si deve controllare se ci sono zeri non significativi

alla sinistra del bit più significativo, in questo caso si deve traslare SOMMA verso

sinistra fino a che il bit più significativo del risultato è 1, sottraendo il relativo

valore dall’esponente. Si valutano le condizioni di eccezione.

Si arrotonda il risultato se la condizione logica R(M0 + S) è vera, dove le tre

variabili hanno lo stesso significato illustrato per la moltiplicazione. Nel caso in

cui i p bit più significativi fossero 1 si ha lo stesso epilogo della moltiplicazione.

Figura 3.6: Mantisse prima dell’addizione

33

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

Figura 3.7: Risultato della somma delle mantisse prima della normalizzazione

Figura 3.8: Mantissa normalizzata prima dell’arrotondamento

3.3

Floating point unit e standard IEEE 754

L’implementazione dello standard IEEE 754 nelle architetture di CPU presenta

due grosse problematiche.

La prima è che il pipelining diventa molto difficoltoso dal momento che devono essere intercettati i risultati ”eccezionali”. Nel normale funzionamento di

una CPU, quando si verifica una condizione di eccezione IEEE vengono prodotti

i relativi risultati speciali, o eventualmente si può verificare una trap; successivamente è richiesto che tutte le istruzioni precedenti a quella che ha provocato

l’eccezione forniscano i risultati, e che tutte le istruzioni successive eseguano come

se niente fosse accaduto. Tali requisiti pongono un limite all’implementazione

dell’ILP per le istruzioni floating point, e ciò è dovuto al fatto che esse non possono affrontare lo stadio di esecuzione in un solo ciclo di clock. Quindi prima di

eseguirne una si deve essere a conoscenza del fatto che essa non provocherà un’eccezione, nel caso contrario i risultati di un’altra istruzione, che nel frattempo ha

iniziato o sta finendo di usare una qualunque unità funzionale, verrebbero corrotti.

In fase di fetch degli operandi, l’istruzione che provocherà l’eccezione dev’essere

fermata finchè il conflitto termina. Per risolvere tale inconveniente l’ISA MIPS

34

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

IV introduce un meccanismo di ”rilassamento” delle eccezioni sincrone. Ciò rende

il modello computazionale non completamente compatibile con i dettami dello

standard.

La seconda problematica è dovuta al fatto che i risultati eccezionali possono

essere riutilizzati come operandi. Le floating point unit MIPS hanno grossi problemi a gestire questi valori in quanto esse sono costituite da una componente di

hardware che gestisce la maggior parte delle operazioni, e soltanto nei pochi casi

in cui essa fallisce interviene il software. Quest’ultimo viene richiamato mediante

un’eccezione non IEEE chiamata unimplemented operation, dopodichè il codice

dell’eccezione passa ad un relativo gestore per le applicazioni floating point. Nella

maggior parte dei casi, l’eccezione unimplemented operation si ha al verificarsi di

un’eccezione IEEE.

3.4

Registri floating point

Le CPU MIPS64, oltre ad essere dotate di 32 registri general-purpose, possiedono

32 registri floating point (FPR) da 64 bit ciascuno, i cui nomi vanno da F0 a F31.

Ogni registro può memorizzare numeri sia in formato single, occupando i 32 bit

più bassi, che numeri double usando l’intero registro. Un’ulteriore tipologia di

dati memorizzati è chiamata paired-single, costituita da due single affiancati in un

unico registro.

3.4.1

FCSR

Come già accennato nel Paragrafo 3.2.3, i processori MIPS64 sono dotati di

uno speciale registro chiamato FCSR(Floating Point Control and Status Register)

di 32 bit che controlla le operazioni della floating point unit.

35

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

Il registro FCSR ha le seguenti funzioni: seleziona la modalità di arrotondamento, abilita le trap per le eccezioni IEEE, riporta qualunque eccezione IEEE si

sia verificata durante l’esecuzione delle ultime istruzioni e indica i risultati delle

istruzioni di confronto.

Figura 3.9: Registro FCSR

Di seguito sono elencate le funzioni dei singoli campi di questo registro:

FCC : Codici condizionali floating point. Essi memorizzano il risultato delle

istruzioni di confronto (per esempio C.LT.D) e vengono verificati dalle istruzioni di

branch (per esempio BC1F) e da quelle di spostamento condizionale (per esempio

MOVT). Si veda il Paragrafo A.6 per comprenderne l’utilizzo con queste istruzioni.

FS(Flush to Zero): Quando vale uno, i risultati denormalizzati vengono ”portati a zero” invece di essere rappresentati con la relativa notazione speciale.

Impl : Disponibile per funzionalità aggiuntive della floating point unit.

0 : Riservato per utilizzi futuri. Non presente in EduMIPS64.

Cause: Bit di causa. Indicano se durante l’esecuzione dell’ultima istruzione

si è verificata una condizione di eccezione IEEE. Tali bit vengono scritti per ogni

operazione floating point appena eseguita. Il bit relativo all’eccezione viene posto

a uno se si è verificata quella condizione di eccezione, avviando, se abilitata, la trap

corrispondente. Il bit viene posto a zero se non c’è alcuna condizione di eccezione.

Se si è verificata una trap, prima di continuare l’esecuzione del programma, si

deve riportare a zero il relativo bit. I nomi mnemonici dei bit, usati anche per i

36

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

campi Enables e Flags, sono i seguenti: V (Operazione non valida), Z (Divisione

per zero), O (Overflow), U (Underflow), I (Inexact).

Enables: Bit di abilitazione trap. Gestiscono l’attivazione o la disattivazione

delle trap relative alle condizioni di eccezione IEEE. La trap si verifica solo se

entrambi i bit del campo Cause e del campo Enables appartenenti alla stessa

eccezione sono posti a uno.

Flags: Bit di eccezione mascherata. Questo campo mostra le condizioni di

eccezione che si sono verificate per le istruzioni completate. I bit vengono posti a

uno solo quando si è appena verificata una condizione di eccezione IEEE, ma non

si è avuta alcuna trap in quanto questa era disabilitata dal campo Enables.

RM :Modalità di arrotondamento. I due bit di questo campo vengono usati per

definire quale delle quattro modalità di arrotondamento, viste nel Paragrafo 3.2.4,

è usata, codificandola con un numero da 0 a 3.

Riassumendo l’attività di gestione delle eccezioni di una cpu MIPS64, al verificarsi di una condizione di eccezione IEEE vengono attivati i relativi bit del campo

Cause. Si effettua il controllo del campo Enables; se il bit dell’eccezione è attivo

si disabilita nuovamente il bit del campo Cause e si ha una trap, se al contrario il

bit dell’eccezione non è attivo si disabilita nuovamente il bit del campo Cause, e

si pone a 1 il bit del campo Flag in quanto non si ha la trap. Per ulteriori dettagli

sul registro FCSR consultare [7].

3.4.2

Altri registri

Esistono altri registri che costituiscono un’alternativa al registro FCSR. Tuttavia non è stata ritenuta necessaria la loro presenza nel simulatore.

- FCCR (Floating point Condition Code Register): è un modo alternativo per

37

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

leggere e scrivere i codici condizionali che appaiono nel registro FCSR.

- FEXR (Floating point Exceptions Register): è un registro in cui compaiono

soltanto i campi Cause e Flags del registro FCSR.

- FENR(Floating point ENables Register): presenta le flag di abilitazione delle

trap relative alle eccezioni IEEE, il campo FS e quello per impostare gli

arrotondamenti.

3.5

Instruction set

Le istruzioni dell’ISA MIPS64 possono essere raggruppate secondo i sei gruppi funzionali elencati di seguito. Per ragioni di brevità, verranno menzionate

soltanto le istruzioni implementate in EduMIPS64, i cui dettagli progettuali sono

approfonditi nel Paragrafo 4.3. Per un elenco completo consultare [8].

3.5.1

Trasferimento dati

L’architettura della FPU è anch’essa load/store, ovvero tutti i calcoli vengono

eseguiti sui valori presenti nei registri. I dati sono trasferiti senza che ne venga

effettuato alcun controllo di formato, per cui non è possibile alcuna eccezione

IEEE. Si hanno diversi tipi di trasferimento: dagli FPR alla memoria, e viceversa,

vengono trasferite solo word e doubleword. Lo stesso vale anche per i trasferimenti

tra gli FPR e i GPR, mentre per i trasferimenti tra i registri di controllo della

FPU (per esempio l’FCSR) e i GPR sono implicate soltanto word. Come per

le istruzioni intere di caricamento, anche quelle floating point devono riferirsi a

dati ”naturalmente allineati”, altrimenti si verifica l’eccezione Address Error. La

FPU, oltre ad utilizzare l’indirizzamento register+offset visto nel Paragrafo 2.4,

può utilizzare anche una modalità diversa chiamata register+register.

38

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

Nome

LDC1

LWC1

SDC1

SWC1

DMFC1

DMTC1

MFC1

MTC1

Descrizione

Carica una cella di memoria (doubleword) in un FPR

Carica una semicella (word) di memoria in un FPR

Memorizza una doubleword da un FPR alla memoria

Memorizza una word da un FPR alla memoria

Copia una doubleword da un FPR ad un GPR

Copia una doubleword da un GPR ad un FPR

Copia una word da un FPR ad un GPR

Copia una word da un GPR ad un FPR

Tabella 3.4: Istruzioni di trasferimento dati

3.5.2

Aritmetiche

Operano su unità dati formattate, e i risultati della maggior parte delle operazioni floating point è soggetta al rispetto dello standard IEEE 754. I calcoli sono

eseguiti con precisione infinita, e successivamente i risultati vengono arrotondati

al formato specificato usando la modalità di arrotondamento corrente.

Nome

ADD.D

DIV.D

MUL.D

SUB.D

C.cond.D

Descrizione

Addizione double

Divisione double

Moltiplicazione double

Sottrazione double

Verifica il predicato cond tra due FPR

Tabella 3.5: Istruzioni aritmetiche

3.5.3

Conversione

Eseguono conversioni da numeri in virgola mobile a numeri in virgola fissa

e viceversa. Ciascuna istruzione converte valori da uno specifico formato ad un

altro (per esempio CVT.L.D converte un double in un long). Alcune istruzioni consentono di specificare la modalità di arrotondamento da utilizzare, altre prelevano

tale informazione dal registro FCSR.

39

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

Nome

Descrizione

CVT.D.formato Converte numeri a virgola fissa in double

(f ormato ∈ {L, W }, L = Long, W = int)

CVT.L.D

Converte un double in un long

CVT.W.D

Converte un double in un int

Tabella 3.6: Istruzioni di conversione

3.5.4

Spostamento operandi formattati

Copiano valori tra gli FPR. Alcune istruzioni di questa categoria ( spostamento

condizionale) effettuano la copia verificando prima una condizione (zero di un

registro, condizione booleana); altre la effettuano in modo incondizionato. Nessun

controllo viene eseguito sul formato del registro sorgente, che può quindi non essere

formattato secondo uno dei tipi floating point.

Nome

MOV.D

MOVF.D

MOVT.D

MOVN.D

MOVZ.D

Descrizione

Sposta valori

Sposta valori

Sposta valori

Sposta valori

Sposta valori

double

double

double

double

double

tra FPR

se il codice condizionale è vero

se il codice condizionale è falso

tra FPR se un GPR è diverso da 0

tra FPR se un GPR è uguale a 0

Tabella 3.7: Istruzioni di spostamento degli operandi formattati

3.5.5

Salto condizionale

Anche la FPU è dotata di istruzioni che effettuano salti PC-relative (si veda

il Paragrafo 2.5.1) dopo aver verificato i codici condizionali del registro FCSR.

Nome

BC1F

Descrizione

Salta se il codice condizionale dell’FCSR è falso

(F CSR(cc) = f also, cc ∈ [0, 7])

BC1T Salta se il codice condizionale dell’FCSR è vero

Tabella 3.8: Istruzioni di salto condizionale

40

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

3.6

Pipelining

Nella Figura 3.10 è illustrata la struttura di una pipeline a 5 stadi che supporta il pipelining delle istruzioni floating point. Il moltiplicatore (M) e l’addizionatore (A) floating point sono ”fully pipelined” poichè possono praticare l’ILP sulle

istruzioni che li occupano; queste unità funzionali hanno una latenza rispettivamente di 7 e 4 stadi. Il divisore (DIV) non esegue il pipelining, ma necessita

comunque di 24 cicli per completare il calcolo.

A causa della diramazione nello stadio ID, occorre realizzare connessioni separate con gli stadi EX,A1,M1 e DIV; per cui si utilizzano i pipeline registers ID/EX,

ID/A1, ID/M1 e ID/DIV. Come accennato nel Paragrafo 3.3, l’ILP delle istruzioni

Figura 3.10: Pipeline a 5 stadi

floating point è difficile da realizzare; si possono verificare stalli strutturali perchè

le unità funzionali che non effettuano il pipelining (divisore) potrebbero non essere

disponibili, o anche per altri motivi illustrati nel paragrafo 3.6.1. Inoltre, poichè

le istruzioni floating point hanno un tempo di esecuzione differente, lo stadio WB

41

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

potrebbe essere raggiunto in modo disordinato rispetto al flusso di esecuzione;

sono possibili quindi dipendenze di output con successivi stalli WAW. Il numero

di stalli RAW, infine, è considerevole per via della lunga latenza delle operazioni

floating point.

3.6.1

Concorrenza sul register file

Il register file di un processore MIPS64, illustrato nella Figura 3.11, comprende

il set di 32 registri da 64 bit e la logica che controlla le operazioni di scrittura e

lettura. Ipotizzando che esso abbia solamente una porta di scrittura, le operazioni

floating point che scrivono su un registro nello stesso ciclo di clock andranno in

conflitto. Aumentare il numero di porte di scrittura non è una soluzione adeguata

perchè esse sarebbero raramente utilizzate. Il problema viene risolto in due modi

differenti: il primo è quello di prevedere, nello stadio ID, se si verificherà un

conflitto di questo tipo, ed eventualmente fermare un’istruzione nel secondo stadio

della pipeline. Il vantaggio è aver seguito il principio secondo cui tutti gli hazard

devono essere prevenuti nello stadio ID. Lo svantaggio è l’utilizzo di uno shift

register e della logica di controllo dei conflitti sul register file.

Figura 3.11: Register file di un processore MIPS64

42

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

Il secondo metodo consiste nell’inserire uno stallo quando le istruzioni in conflitto accedono allo stadio MEM o WB. Generalmente viene data maggiore priorità all’istruzione che ha latenza maggiore; l’ordine di priorità è dunque divisione,

moltiplicazione, addizione/sottrazione e istruzione intera. Il vantaggio è la facilità

di verificare l’hazard strutturale direttamente all’uscita dello stadio di esecuzione,

e di concedere l’ingresso allo stadio successivo solo all’istruzione con maggiore

priorità. Lo svantaggio è introdurre una maggiore complessità nel controllo della

pipeline, questo perchè gli hazard strutturali possono ora verificarsi in due punti

differenti di essa. La complicazione è dovuta al fatto che, fermando le istruzioni

che occupano gli stadi EX,M7 o A4, si devono fermare anche quelle che le seguono.

3.6.2

Rilevamento degli hazard

Se la pipeline rileva gli hazard nello stadio ID, prima che un’istruzione possa

essere ”emessa”, devono essere eseguiti dei controlli sui tre hazard che possono

verificarsi:

- Hazard strutturali: non considerando il caso di stallo strutturale visto nel

paragrafo precedente, l’unico altro caso che si possa verificare riguarda il

divisore. Prima di fare avanzare una divisione, si deve attendere che questa

unità funzionale non sia occupata, e la porta di scrittura del registro di

destinazione disponibile quando richiesto.

- Hazard RAW: si deve attendere affinchè i registri sorgenti dell’istruzione

diventino validi.

- Hazard WAW: si deve attendere affinchè il registro di destinazione venga

scritto da un’altra istruzione che sta ancora affrontando gli stadi A1..A4 e

M1..M7.

43

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

3.6.3

Pipeline FP del MIPS R4000

Il processore R4000 implementa l’ISA MIPS64, ma non usa una pipeline a 5

stadi, bensı̀ a 8. Gli stadi supplementari, oltre a permettere frequenze di clock

elevate, servono a ”spalmare” su due cicli la lentezza nell’accesso alla cache; questa

strategia, usata nelle moderne pipeline, è chiamata superpipelining.

La FPU è composta dalle tre unità funzionali illustrate nella Figura 3.10.

L’addizionatore, oltre ad essere impiegato per le somme e le sottrazioni, è usato

nello stadio finale di moltiplicazione e divisione.

La generica unità funzionale può eseguire una varietà di 8 operazioni primitive,

le quali vengono combinate in vari modi per realizzare le operazioni floating point.

Nella tabella 3.11 sono illustrate le fasi del pipelining di una MUL.D seguita da

una ADD.D.

Si supponga che le due istruzioni non presentino alcuna dipendenza; nonostante ciò, la moltiplicazione, nel suo settimo stadio di esecuzione (N+A), che

avviene nel ciclo 6, usa l’addizionatore. La ADD.D, dovendo anch’essa farne uso

(stadi A+R ed S+A), deve attendere per due cicli fino a che la MUL.D abbia

terminato anche lo stadio R.

44

CAPITOLO 3. LA FLOATING POINT UNIT DEI PROCESSORI MIPS64

Stadio

A

D

E

M

N

R

S

U