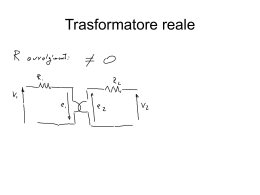

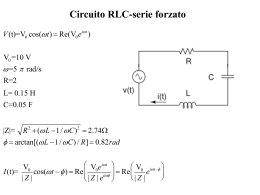

Università degli studi di Pavia Facoltà di Ingegneria Dipartimento di Elettronica PROGETTAZIONE IN TECNOLOGIA CMOS 0.18µm DEL SISTEMA DI ALIMENTAZIONE DI UN CHIP RFID A 13.56 MHz Relatore: Chiar.mo Prof. Piero Malcovati Correlatore: Dott. Ing. Andrea Lombardi Tesi di Laurea di Davide Cartasegna Anno Accademico 2007/2008 Indice 1 Introduzione 1.1 Generalità del progetto . . . . . . . . . . . . . . . . . . . . . . 1.2 Descrizione dei capitoli . . . . . . . . . . . . . . . . . . . . . . 3 3 6 2 Sistemi RFID 2.1 Definizione e principio di funzionamento . . . . . . . . . . . . 2.2 Classificazione delle tipologie . . . . . . . . . . . . . . . . . . 2.2.1 La normativa ISO 15693 . . . . . . . . . . . . . . . . . 7 7 8 11 3 Ricevitore, rettificatore e relative protezioni 3.1 Campo magnetico e accoppiamento induttivo . . . 3.1.1 Auto-induttanza e mutua-induttanza . . . . 3.1.2 Legge di Faraday . . . . . . . . . . . . . . . 3.1.3 Calcolo di L2 . . . . . . . . . . . . . . . . . 3.1.4 Risonanza . . . . . . . . . . . . . . . . . . . 3.1.5 Calcolo del campo magnetico minimo Hmin 3.2 Rettificatore . . . . . . . . . . . . . . . . . . . . . . 3.2.1 Principio di funzionamento teorico . . . . . 3.2.2 Principali tipologie e relative caratteristiche 3.2.3 Raddrizzatore CMOS con gate incrociati . . 3.3 Circuito di protezione . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 13 14 17 18 19 21 21 22 23 26 27 . . . . . . 30 30 32 34 38 40 41 4 Pompa di carica e Regolatore di Tensione LDO 4.1 Generalità e principio di funzionamento . . . . . 4.2 Tipologie di base . . . . . . . . . . . . . . . . . . 4.3 Pompa di carica ad inverter CMOS . . . . . . . . 4.4 Sistema di controllo retroazionato . . . . . . . . . 4.4.1 Amplificatore operazionale integrato . . . 4.5 Regolatore di tensione LDO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Simulazioni ed ottimizzazione 44 5.1 Rettificatore e protezioni . . . . . . . . . . . . . . . . . . . . . 44 5.2 Pompa di carica . . . . . . . . . . . . . . . . . . . . . . . . . 48 5.3 Amplificatore operazione e regolatore di tensione LDO . . . . 51 1 5.4 Sistema completo . . . . . . . . . . . . . . . . . . . . . . . . . 54 6 Conclusioni 58 Bibliografia 60 2 Capitolo 1 Introduzione I processi di stoccaggio, managment e controllo dei prodotti durante tutto il percorso di produzione e post-produzione, sono per qualsiasi azienda un aspetto molto critico. Infatti, mantenere inventari di magazzino costantemente aggiornati, o tracciare l’esatta posizione e lo stato di conservazione di una specifica spedizione in tempi brevi, sono i modi migliori per rendere minimi sia i costi che i ritardi di consegne e produzioni. Da quando, negli ultimi 15 anni, elettronica e informatica hanno preso piede praticamente in ogni campo, il comune inventario manuale è diventato immediatamente obsoleto ed ha lasciato il posto a sistemi più tecnologici ed efficienti. Grazie alla continua ricerca nei campi dell’elettronica e delle telecomunicazioni e alla pressante richiesta da parte delle aziende allo scopo di migliorare queste operazioni, tanto gravose quanto imprescindibili, si è arrivati alla creazione della tecnologia RFID (Radio-Frequency IDentification). Fanno parte di questa categoria tutti quegli apparati elettronici, single o multi chip, che, grazie a dispositivi integrati quali antenne patch, microprocessori, memorie e sensori a bassissimo consumo di potenza, riescono ad essere incorporati in qualsiasi tipo di prodotto, rendendo più agevole la manipolazione dei dati ad esso associati. Una panoramica sugli RFID è presente nel Capitolo 2 ad essi dedicato. 1.1 Generalità del progetto Gli argomenti trattati in questa tesi sono da inserire in un progetto più ampio, che mira alla realizzazione di dispositivi miniaturizzati per il monitoraggio delle condizioni di conservazione degli alimenti [4]. Il sistema in questione è volto alla realizzazione di una sorta di “etichetta intelligente” provvista di sensori, circuiti per l’elaborazione dati e memoria interna, che riesca a identificare il prodotto, tracciarne la posizione e tenere conto del suo stato di conservazione lungo tutta la filiera produzione-trasporto-consegna. 3 Figura 1.1: Schema a blocchi del sistema completo In particolare il progetto, come mostrato schematicamente in Fig. 1.1, prevede lo sviluppo di: • sensori di temperatura, umidità e intensità luminosa; • circuiti integrati di interfaccia per sensori di temperatura, umidità e intensità luminosa; • un circuito di gestione e conversione dell’energia; • un convertitore A/D; • un circuito integrato per la trasmissione dati; • una microbatteria a ioni litio. I sensori monitorano costantemente lo stato del prodotto e inviano i segnali rilevati ai circuiti di interfaccia. Mediante il convertitore A/D i segnali analogici vengono poi convertiti in digitale e memorizzati. Ogni volta che il reader interroga il tag, inizia una trasmissione dati bidirezionale, mentre il sistema di gestione dell’energia alimenta l’intero chip e ricarica la batteria. Quest’ultima viene utilizzata sia come buffer di corrente per le situazioni più critiche, sia come alimentazione del chip quando esso non iteragisce con il reader. Tutti questi dispositivi devono essere progettati in modo da essere inseriti all’interno di una etichetta flessibile e quindi dovranno avere bassissimi consumi di potenza e dimensioni alquanto ridotte. In questo lavoro di tesi, in particolare, è stata svolta la progettazione del circuito di gestione e conversione dell’energia a bassissimo consumo di 4 potenza che, sfruttando l’energia del campo magnetico fornita dal reader, deve provvedere all’alimentazione di tutto il sistema RFID precedentemente descritto. Le specifiche di progetto per il sistema di alimentazione sono riassunte in Tab. 1.1, per essere poi riprese e trattate con maggior dettaglio nei prossimi capitoli. Vale la pena di anticipare come la ricarica della batteria avvenga in una fase diversa dalla trasmissione dati: si è giunti a questo compromesso valutando il fatto che, con i minimi valori della tensione indotta imposti da specifica, risulta impossibile riuscire a fornire la corrente (Iload ) necessaria per eseguire entrambe le operazioni contemporaneamente. Specifica Specifiche di progetto Valore Range tensione indotta Frequenza tensione indotta Vout Ricarica Vout Data Transmission Iload max Ricarica Iload max Trasmissione Dati 0.1 ÷ 10 V 13.56 MHz±7 KHz 3.3V 1.8V ≤100µA ∼150µA Tabella 1.1: Specifiche di progetto Come schematizzato in Fig. 1.2, il sistema in questione è composto da quattro blocchi principali: • antenna; • raddrizzatore; • pompa di carica; • controllo retroazionato. L’antenna è di tipo patch e serve a collegare in maniera wireless il reader al tag RFID; essa viene utilizzata sia in ricezione che in trasmissione e poiché nel caso considerato si sfrutta un accoppiamento esclusivamente magnetico, essa è formata da una serie di spire concentriche che racchiudono un’area delle dimensioni di una carta di credito. Il raddrizzatore viene utilizzato per trasformare la tensione sinusoidale indotta sull’antenna dal campo magnetico H in una tensione continua che, pur presentando una notevole oscillazione, fornisce una prima grossolana alimentazione al sistema e ne permette l’accensione. Per raggiungere i livelli di tensione desiderati durante il normale funzionamento del dispositivo, invece, è necessario l’utilizzo di una pompa di carica, la quale, stabilizzata dal contollo retroazionato, deve mantenere costante la tensione in uscita in qualunque condizione di corrente di carico richiesta dalle specifiche. 5 Figura 1.2: Schema a blocchi del circuito per la gestione energetica 1.2 Descrizione dei capitoli Nei prossimi capitoli verrà descritto il funzionamento dei vari blocchi costituenti il sistema di gestione dell’energia. Partendo da alcune considerazioni sul range di lettura legate ai campi magnetici, si arriverà a trattare le scelte progettuali effettuate, per terminare presentando i risultati ottenuti dalle simulazioni. In particolare, nel Capitolo 3, verranno trattati in dettaglio i principi fondamentali dei campi magnetici e delle loro interazioni con gli elementi circuitali, in modo da spiegare in che modo, e con quali risultati, avvengono gli accoppiamenti tra reader e tag in un sistema RFID come quello considerato; il capitolo si conclude con la presentazione del circuito raddrizzatore adottato e del relativo dispositivo di protezione, atto a prevenire ogni pericolo di danneggiamento. Nel Capitolo 4 verrà presentata la pompa di carica: dopo una breve introduzione teorica, saranno presentati gli schemi elettrici più comuni e quello da noi utilizzato con i relativi principi di funzionamento, ponendo particolare attenzione sul sistema di controllo retroazionato e sull’amplificatore operazionale ideato per eseguire tale controllo. Nell’ultima parte, inoltre, sarà illustrato il circuito LDO. Nel Capitolo 5 verranno presentate e motivate tutte le scelte progettuali effettuate, partendo dalle topologie circuitali per arrivare sino alle dimensioni dei componenti, sia dei singoli blocchi, sia del sistema di alimentazione completo. Infine, nel Capitolo 6, si trarranno le conclusioni di tutto il lavoro di tesi. Viene inoltre introdotto un capitolo, in particolare il Capitolo 2, che fornisce una panoramica abbastanza esaustiva sulla tecnologia RFID: un confronto tra le principali tecnologie esistenti nel campo dell’Auto-ID all’attuale stato dell’arte. 6 Capitolo 2 Sistemi RFID In questi anni le procedure automatiche di identificazione, le cosiddette Auto-ID, hanno riscosso un crescente successo in svariati settori industriali. A partire dalla catalogazione dei prodotti delle aziende manifatturiere, per arrivare al monitoraggio della merce di una specifica spedizione da parte delle compagnie di trasporto, si presenta la necessità di fornire in modo rapido e preciso alcune informazioni rilevanti su un determinato prodotto. La svolta in questo settore è stata apportata una ventina di anni fa dagli ormai famosi codici a barre, grazie ai quali i processi di stoccaggio iniziarono a velocizzarsi. Ciononostante, pur essendo economicamente favorevoli, essendo formati da una semplice etichetta stampata, necessitano comunque di operatori che, a distanze non superiori ai 15 cm, eseguano una lettura ottica. Inoltre, essi non possono essere riprogrammati e portano una quantità alquanto limitata di informazioni. Una soluzione tecnicamente ottima è stata trovata con le smart-card, nelle quali ogni informazione viene memorizzata all’interno di un microchip: in questo modo infatti si ottengono una memoria più capiente e la facile sovrascrittura dei dati preinseriti. A discapito di questa tecnologia c’è però il fatto che la lettura avviene mediante contatti ’elettro-meccanici’ (contatti superficiali tenuti in pressione da molle), che, non solo si usurano facilmente, ma molto spesso risultano impraticabili. Per superare questi e ad altri inconvenienti è stata sviluppata la tecnologia RFID, qui di seguito brevemente illustrata. Le principali differenze tra le tecnologie dell’Auto-ID sono sintetizzate in Tab. 2.1. 2.1 Definizione e principio di funzionamento L’acronimo RFID, come già accennato nell’introduzione di questa tesi, sta per Radio Frequency IDentification e comprende tutta una serie di dispositivi che sfruttano alcune delle principali qualità delle smart card classiche, quali la capiente memoria e la riprogrammazione, aggiungendovi la pratica 7 possibilità della comunicazione senza fili. Le due parti fondamentali di un sistema RFID sono (Fig. 2.1): • il dispositivo, o tag, posto sull’oggetto da identificare; • il lettore (reader ) che, dipendentemente dalla tecnologia utilizzata, può operare in lettura o in lettura/scrittura sui dati contenuti nel tag. Figura 2.1: Generico sistema RFID Tipicamente il reader contiene un modulo per l’alta frequenza (trasmettitore/ricevitore), un’unità di controllo e un elemento di accoppiamento con il tag. Molto spesso possiede inoltre un’interfaccia che lo rende idoneo allo scambio di dati con altri sistemi specifici (PC, sistemi di controllo, ecc). Il tag invece è generalmente composto da un elemento di accoppiamento e da un microchip. 2.2 Classificazione delle tipologie Considerate le innumerevoli tipologie di RFID esistenti sul mercato, la base più logica sulla quale redigere una sorta di classificazione risulta essere quella delle differenti caratteristiche tecniche che i vari sistemi presentano [1]. I sistemi RFID, ad esempio, possono operare in accordo con due differenti procedure di base: Half Duplex (HDX)/ Full Duplex (FDX) oppure quella sequenziale (SEQ). Una prima suddivisione può quindi essere effettuata tra gli apparati che appartengono ad una o all’altra tipologia. Per quanto riguarda i primi, la trasmissione dei dati da parte del tag avviene esclusivamente durante il periodo di funzionamento del reader. Visto che il segnale proveniente dal tag risulta essere sempre più debole rispetto a quello del reader, è solitamente necessario, in questo caso, ricorrere a particolari accorgimenti per ottenere una corretta comunicazione. Nei sistemi sequenziali, invece, vengono introdotte, sul segnale del reader, brevi pause a intervalli regolari, durante le quali il tag viene abilitato alla trasmissione. L’unico 8 System parameters Typical data quantity(bytes) Data density Machine readability Readability by people Influence of dirt/damp Influence of direction and position Degradation/wear Purchase cost/reading electronics Unauthorised copying/modification Reading speed Maximum operation range Barcode Smart Card RFID system 1-100 Low Good Limited Very high 16-64k Very high Good Impossible Possible(contacts) 16-64k Very high Good Impossible No influence Low Limited Unidirectional Contacts No influence No influence Very low Low Medium Slight Low Impossible Low Impossible Very fast 0-50cm Direct contact 0-5m(µwaves) Tabella 2.1: Differenze tra vari sistemi Auto-ID inconveniente in questo caso è la diminuzione drastica della potenza disponibile durante la trasmissione del tag, che quindi necessita di un opportuno dispositivo di immagazzinamento dell’energia. Un altro aspetto molto importante riguarda la capacità di memoria interna al tag. Da questo punto di vista si distinguono in primo luogo gli RFID a 1 bit da quelli multi-bit. I primi non necessitano di un chip integrato in quanto possono comunicare solamente due stati: “tag in the field ” oppure “no tag in the field ”. Per questo, possono raggiungere dimensioni estremamente piccole ed il loro uso consiste principalmente in semplici operazioni di monitoraggio antitaccheggio. Tra quelli multi-bit, con la memoria che può andare da qualche bytes a parecchi kilobytes, possiamo discernere tra i vari tipi di memoria interna utilizzati. La maggior parte dei sistemi RFID utilizza delle EEPROM (electrically erasable programmable read-only memory), anche se queste ultime presentano alcuni inconvenienti, tra cui la notevole potenza dissipata in scrittura e un numero limitato di cicli di sovrascrittura. Le altre memorie utilizzate sono le FRAM (ferromagnetic random access memory) e le SRAM (static random access memory). Le prime pur avendo un processo costuttivo complicato, che rende difficile la loro diffusione, presentano, rispetto alle EEPROM, una potenza dissipata 100 volte inferiore e una riduzione dei tempi di scrittura di un fattore 1000. Le seconde invece hanno l’inconveniente di essere completamente volatili e quindi di dover essere supportate da una 9 batteria ausiliaria, che le mantenga accese anche in assenza del reader. Tutte le trasmissioni dati devono comunque essere protette ed autorizzate; quindi, sempre per quanto riguarda la categoria multi-bit, è necessaria una logica elettronica più o meno complessa, che svolga la funzione di controllo e fornisca le licenze necessarie al corretto funzionamento del sistema. Per i casi più semplici, la logica può essere implementata come macchina a stati, che risulta facile e di rapida progettazione, anche se, in caso di modifiche funzionali, il layout del chip va completamente ridisegnato. D’altra parte, per svolgere funzioni più complesse o non meglio definite in fase di progettazione, è quasi d’obbligo l’utilizzo di un microprocessore integrato che, pur essendo più complesso a livello circuitale, ha il pregio di presentare una maggior flessibilità d’uso, in quanto può essere abilitato a svolgere qualsiasi operazione necessaria, semplicemente sostituendo il software o il firmware. Un’altra suddivisione fondamentale tra i vari RFID si presenta tra quelli passivi e quelli attivi. Gli RFID passivi non incorporano alcuna batteria interna e vengono attivati ed alimentati direttamente tramite il segnale emesso dal reader ; segnale che allo stesso tempo, funge anche da portante per la trasmissione dei dati. Gli RFID attivi, invece, possiedono una batteria interna, che li rende indipendenti dal reader per un tempo più o meno lungo. In questi ultimi la batteria viene ricaricata ad ogni interrogazione, sfruttando lo stesso principio degli RFID passivi. Da notare è la versatilità dei primi: non dipendendo dalla carica di una batteria, possono essere disposti su qualsiasi oggetto per un tempo indeterminato e riescono a mantenere in memoria tutte le informazioni in essi contenuti al momento dell’ultima scrittura, per poi fornirle nuovamente al reader non appena necessario. Esiste inoltre una categoria ibrida di RFID, che possiede una batteria, ma, quando è possibile, sfrutta il campo proveniente dal reader per l’alimentazione. È questo il caso del sistema trattato in questa tesi: la batteria viene utilizzata per mantenere in funzione i sensori integrati e i circuiti per l’immagazzinamento dati solo quando il tag è fuori dal campo del reader, altrimenti, il circuito risulta per molti aspetti un RFID passivo. Altre caratteristiche peculiari che contraddistinguono un sistema da un altro sono la frequenza di utilizzo, il range di funzionamento e il tipo di accoppiamento tra reader e tag. Queste tre specifiche però variano quasi sempre di pari passo, in quanto esistono dei limiti fisici che non possono essere in alcun modo superati, se non realizzando apparati che non rispettino i limiti di sicurezza imposti dalla normativa esistente. Ad esempio, i sistemi RFID con un range di lettura fino al cm vengono detti close coupling systems. Per l’accoppiamento essi possono utilizzare indifferentemente i campi elettrico e magnetico e lavorano nominalmente con frequenze che vanno dalla DC ai 30 MHz. Per questa categoria di RFID non esistono problemi di potenza dissipata, in quanto, essendo la regione in cui il reader deve agire ben circoscritta, l’operatore ne è sempre tagliato fuori e il campo può 10 assumere anche valori molto elevati. La classe successiva è quella dei remote coupled systems, nei quali l’accoppiamento avviene quasi esclusivamente per via induttiva, a distanze non superiori al metro e con frequenze di utilizzo che vanno dai 135 kHz ai 13.56 MHz. Fanno parte di questa categoria anche i proximity coupling systems gestiti dalla normativa ISO 14443 e i vicinity coupling systems, dei quali fa parte il sistema descritto in questa tesi, gestiti dalla normativa ISO 15693 [6], che tratta le smart label. L’ultimo gruppo comprende gli RFID con range superiore al metro e frequenze di lavoro sia nella banda delle UHF (868 MHz in Europa e 915 MHz in USA), sia nelle microonde tra i 2.5 GHz e i 5.8 GHz. In questo caso l’accoppiamento avviene tramite campo elettromagnetico, mediante l’uso di antenne adatte a lavorare in quel range di frequenze. 2.2.1 La normativa ISO 15693 La normativa ISO 15693 intitolata “Identification Cards – Contactless Integrated Circuit(s) Cards – Vicinity Circuit(s) Card ” descrive il metodo di funzionamento ed i parametri operativi delle vicinity coupling smart cards senza contatti [6]. Queste sono smart card con un range di funzionamento fino a 1 m che tipicamente utilizzano delle unità di memoria piuttosto economiche, controllate da semplici macchine a stati. La normativa si articola in tre parti fondamentali: Parte 1: Caratteristiche fisiche; Parte 2: Livelli di potenza e interfaccie per il segnale a radio frequenza; Parte 3: Protocolli per la trasmissione e l’anti-collisione. La Parte 1 definisce le proprietà meccaniche di questo tipo di smart card. Le dimensioni geometriche coincidono esattamente con quelle specificate nella normativa ISO 7810 [7] e sono: 85.72 mm × 54.03 mm × 0.76 mm. Inoltre, in questa parte, vengono specificate le massime sollecitazioni meccaniche, quali torsione o flessione, alle quali la card deve resistere. La Parte 2 definisce i parametri che il campo magnetico di accoppiamento può assumere. In particolare il campo deve essere alternato ad una frequenza di 13.56 MHz ± 7 kHz e deve avere un modulo compreso tra 115 mA/m e 7.5 A/m. Qui viene inoltre specificata la tipologia dell’antenna che, dato il tipo di accoppiamento, risulta essere un avvolgimento con un numero di spire compreso tra 3 e 6. La Parte 3 descrive i protocolli da utilizzare in trasmissione, specificando la trasmissione reader -to-tag e quella tag-to-reader. Nel primo caso il protocollo cerca di massimizzare l’energia trasportata dal segnale, in modo da riuscire a fornirne quanta più energia possibile al tag: viene consigliata 11 perciò una modulazione ASK (Amplitude-Shift Keying) al 10%. Nel secondo caso, invece, è importante sfruttare al meglio l’energia immagazzinata nel tag e quindi viene consigliata una modulazione ASK al 100%, altrimenti chiamata OOK (On-Off Keying). Per quanto riguarda le codifiche possibili, vengono utilizzate in genere codifiche basate sulla durata degli impulsi come la PIE (Pulse Interval Encoding), oppure basate sulle transizioni come la Manchester o la Miller. Per massimizzare l’energia disponibile sono di grande interesse la codifica PIE e la Manchester, codifiche che, inoltre, consentono di ridurre al minimo la circuiteria per la sincronizzazione all’interno dei tag, in quanto forniscono una sequenza “auto-temporizzata”. D’altra parte il metodo di Miller è molto indicato per la trasmissione tag-to-reader data la sua principale peculiarità di avere nulla la componente spettrale in DC. 12 Capitolo 3 Ricevitore, rettificatore e relative protezioni Il fatto di dover utilizzare l’energia del segnale RF emesso dal reader come fonte di alimentazione per il tag richiede la realizzazione di un convertitore RF/DC che riesca a fornire tensioni e correnti idonee al corretto funzionamento del sistema. Siccome i campi RF decrescono velocemente all’aumentare della distanza dalla sorgente e la tecnologia RFID su cui si basa questo progetto coinvolge distanze fino al metro e un accoppiamento esclusivamente magnetico, è molto probabile arrivare ad avere a disposizione solo poche centinaia di microwatt di potenza da trasformare. Per riuscire a lavorare al meglio, anche nelle condizioni più critiche, l’efficienza del convertitore RF/DC deve essere massimizzata, scegliendo la topologia circuitale più opportuna. In questo capitolo vengono descritti i principi dell’induzione magnetica sui quali si basa l’accoppiamento reader -tag e i rispettivi limiti, per quanto riguarda la distanza e la potenza disponibile. Verrà poi analizzato il circuito rettificatore, realizzato in tecnologia CMOS, e si concluderà trattando il circuito di limitazione della tensione di ingresso che funge da sistema di protezione. 3.1 Campo magnetico e accoppiamento induttivo Qualunque carica in movimento, singola o all’interno di un flusso di corrente I, può essere associata ad un campo magnetico H definibile nel seguente modo: I X ~ I= H (3.1) S dove S denota una linea chiusa. ~ per qualsiasi Grazie a questa relazione è possibile calcolare il campo H tipo di conduttore percorso da corrente [1]. L’andamento trovato con questo 13 metodo è detto di “near-field” (NF) poiché tratta il campo in una regione molto vicina alla sorgente che lo emette. È da notare come tutti gli accoppiamenti induttivi siano da considerarsi in NF e non tengano conto del comportamento dello stesso campo in zone, indicate come zone di “far-field”, che invece superano la cosiddetta distanza di Fresnel, e sono caratterizzate da comportamenti completamente differenti. Molto interessanti, in questo contesto, sono gli avvolgimenti cilindrici, detti anche antenne a spira, poiché è con essi che si vanno a creare gli accoppiamenti induttivi presenti nella maggior parte dei sistemi RFID. ~ Sfruttando la (3.1) è possibile trovare l’andamento del modulo di H prodotto da un avvolgimento circolare di raggio R percorso da una corrente I, in funzione della distanza dal centro: IN R2 H= p 2 (R2 + x2 )3 (3.2) In questo caso N è il numero di spire e x rappresenta la distanza dal centro. Dalla (3.2) si può notare la dipendenza cubica del campo H rilevato ad una distanza x dalla sorgente, relazione che per altro identifica il tipico comportamento di NF. Tenendo costanti I ed N , è possibile tracciare un grafico andando ad osservare il comportamento di H al variare di R e della distanza x. Come si può notare in Fig. 3.1, avvolgimenti aventi raggi piccoli forniscono un elevato valore di campo al loro interno, che però decresce rapidamente allontanandosi dal centro spira, a dispetto degli avvolgimenti con raggio più grande che, pur avendo un valore al centro più modesto, riescono a mantenere il livello di campo costante per distanze maggiori. È di vitale importanza che questi comportamenti siano ben valutati per la progettazione dell’antenna, poiché da essi dipenderà il range di funzionamento dell’intero sistema. 3.1.1 Auto-induttanza e mutua-induttanza Per definire correttamente l’accoppiamento induttivo bisogna passare prima per il concetto di flusso magnetico Φ. Quest’ultimo è definito come ZZ ~ B (3.3) Φ= A e rappresenta, come mostrato in Fig. 3.2, la quantità di campo di induzione ~ passante attraverso una superficie di area A e perpendicolare magnetica B, ~ è definito a sua volta come alle linee di campo. Il campo B ~ = µH ~ ~ = µ0 µr H B (3.4) in cui µ0 è la permeabilità magnetica del vuoto e µr rappresenta la permeabilità magnetica relativa del materiale in cui il campo sussiste. 14 Figura 3.1: Andamento del modulo del campo H vicino all’avvolgimento che lo genera, al crescere della distanza Figura 3.2: Flusso magnetico 15 Considerando un circuito formato da un numero di spire N di materiale conduttore interamente percorso da una corrente I, si definisce il flusso totale Ψ come Ψ= X ΦN = N Φ = N µHA (3.5) N in cui le variabili hanno il solito significato, per poi riuscire ad esplicitare correttamente il concetto di induttanza L come Ψ NΦ N µHA = = (3.6) I I I L’induttanza è dunque uno dei parametri variabili di un avvolgimento elettrico e dipende solamente dal materiale attraverso il quale scorre il flusso Φ e dalla geometria della spira. Considerando il caso in cui un secondo avvolgimento sia posto nelle vicinanze del primo (Fig. 3.3), è possibile definire un parametro detto di mutua induttanza, che rappresenta l’effetto di accoppiamento induttivo dovuto al flusso prodotto dalla prima spira percorsa dalla corrente I1 e raccolto dalla seconda di area A2 (Ψ21 ). Similmente all’induttanza L, il parametro di mutua induttanza è definibile come ZZ ~ Ψ21 B2 M21 = = (3.7) I1 A2 I1 L= ~ 2 denota il campo di induzione magnetica in corrispondenza della in cui B seconda spira e dipende dalla corrente I1 [1]. Figura 3.3: Definizione di mutua induttanza Proprietà fondamentale della mutua induttanza è che essa dipende solamente dalla geometria e dalla posizione reciproca degli avvolgimenti, perciò M21 = M12 = M (3.8) Per descrivere in modo qualitativo il livello di accoppiamento tra due induttanze L1 e L2 si definisce il coefficiente di accoppiamento k come 16 k=√ M L1 L2 (3.9) coefficiente che varia tra due casi estremi 0 6 k 6 1: 1 per il massimo accoppiamento e 0 per il minimo. 3.1.2 Legge di Faraday Ogni variazione di flusso magnetico Φ genera un campo elettrico E associato, il cui comportamento dipende dalle proprietà del sistema in cui ha luogo la variazione: • Vuoto: qui la presenza di E genera un campo elettromagnetico che si propaga nello spazio circostante • Spira aperta di conduttore di circonferenza S: in questo caso si genera una tensione ai capi del conduttore, detta tensione indotta e definita come: I Ei = − ui = S dΨ(t) dt (3.10) Se l’avvolgimento è composto da N spire la tensione indotta sarà N volte più grande della tensione che si avrebbe con una sola spira. Inoltre, tornando all’esempio con i due induttori accoppiati L1 ed L2 , le variazioni di Φ1 attraverso L2 , produrranno variazioni di tensione ai capi di quest’ultimo, rendendo perciò possibile quello scambio di informazioni su cui si basano normalmente i collegamenti wireless per induzione magnetica dei sistemi RFID. Figura 3.4: Circuito equivalente di un accoppiamento induttivo tra due avvolgimenti In particolare, è possibile rappresentare l’accoppiamento induttivo attraverso lo schema circuitale mostrato in Fig. 3.4, e da lı̀, iniziare a progettare la parte di ricezione del sistema oggetto di questa tesi. 17 3.1.3 Calcolo di L2 Nello schematico di Fig. 3.4, L1 rappresenta l’antenna del reader, L2 quella del tag, R2 schematizza l’effetto della resistenza di avvolgimento e RL quella di carico. In particolare, il valore di L1 non rientra tra le specifiche del progetto, in quanto non interviene in nessun modo nella caratterizzazione del tag, mentre è possibile calcolare il valore di L2 attraverso la formula che definisce l’induttanza di un’antenna patch a spirale. Nella realtà, l’antenna del sistema considerato è un avvolgimento che segue a grandi linee il perimetro di una smart card (vedi Parag. 2.2.1) ed è quindi rettangolare: è comunque possibile in prima approssimazione considerare un avvolgimento quadrato di uguale area, in modo da ottenere un’approssimazione del valore di induttanza. Forma Quadrata Esagonale Ottagonale Circolare c1 c2 c3 c4 1.27 1.09 1.07 1.00 2.07 2.23 2.29 2.46 0.18 0.00 0.00 0.00 0.13 0.17 0.19 0.20 Tabella 3.1: Coefficienti per il calcolo dell’auto-induttanza di antenne patch a spirale. L’equazione da utilizzare è µN 2 Rc1 c2 2 L= ln + c3 ρ + c4 ρ 2 ρ (3.11) in cui i cn sono coefficienti precalcolati in funzione della geometria [8], µ è la permeabilità magnetica, approssimabile con quella del vuoto, e ρ è il fattore di riempimento definito come ρ= dext − dint dext + dint (3.12) con dext e dint rappresentati in Fig. 3.5. Come previsto dalla normativa, l’area dell’antenna deve essere pari a: AS = (85.72 × 54.03) mm = 46.31 cm2 (3.13) per cui il lato del spira quadrata equivalente è pari a D= √ 46.31 = 6.8 cm 18 (3.14) Figura 3.5: Antenna patch del tag Ipotizzando un numero di spire pari a N = 3, utilizzando come raggio R metà del lato D appena calcolato, i coefficienti cn presi dalla Tab. 3.1 e un ρ pari a 3 · 10−2 otteniamo: L2 = 12.56 · 10−7 × 9 × 6.8 · 10−2 × 1.27 × 2 2.07 −2 −4 × ln + 0.18 × 3 · 10 + 0.13 × 9 · 10 3 · 10−2 (3.15) = 4.88 · 10−7 × [4.23 + 0.0054 + 0.00012] = 2.1 · 10−6 H = 2.1 µH 3.1.4 (3.16) Risonanza Ricavato il valore di L2 , è possibile applicare il principio di Kirchoff alla maglia contenente il tag e ottenere: di1 di2 dΨ2 =M − L2 − i2 R2 (3.17) dt dt dt che, una volta definiti i valori di induttanza del reader, ci può fornire la tensione indotta sul tag [1]. Tenendo conto del fatto che il sistema lavora in regime sinusoidale, la (3.17) può essere riscritta utilizzando la notazione complessa come u2 = + 19 u2 = ωM i1 − ωL2 i2 − R2 i2 (3.18) dalla quale, sostituendo i2 con u2 /RL possiamo ottenere u2 = ωM i1 1+ ωL2 +R2 RL (3.19) Siccome tutto il sistema lavora con una frequenza prefissata e ben definita (vedi specifiche di progetto in Tab. 1.1), è stato inserito un condensatore in parallelo all’antenna del tag, in modo da creare un filtro risonante che amplificasse passivamente il segnale in ingresso. Grazie a questo accorgimento si ottiene una tensione indotta pari a: u2 = ωM i1 1 + (ωL2 + R2 )( R1L + ωC2 ) (3.20) Il dimensionamento dei componenti è stato effettuato tramite la formula di Thomson f= 1 √ 2π L2 C2 (3.21) dalla quale, avendo già calcolato il valore di L2 , è stata ricavata la capacità necessaria alla risonanza C2 = 1 1 = 65 pF = 2 (2πf ) L2 (6.28 × 13.56 · 106 )2 × 2.1 · 10−6 (3.22) Agendo in questo modo, però, non si tiene conto di due aspetti importanti: • la capacità parassita introdotta dal condensatore stesso; • il range di funzionamento del sistema. Per quanto riguarda il primo aspetto, il parassita risulta in parallelo a C2 e perciò, quando si andranno a considerare i componenti reali, il valore di C2 dovrà essere diminuito del valore del parassita, in modo da non far variare la risonanza (C2 è comunque una capacità esterna al chip). Per quanto riguarda il range di funzionamento del sistema, in questo lavoro non sono state affrontate considerazioni al riguardo, in quanto i valori massimi di campo sono forniti da normativa, ma la distanza alla quale il campo risulta ancora utilizzabile dipende soprattutto dalla struttura del reader. Di quest’ultimo non sono presenti al momento specifiche e perciò, in questa sede, ci si limita a fornire il campo H minimo che dovrà essere fornito al tag, calcolato in base alla tensione minima di funzionamento del circuito di gestione dell’energia con rispettivo carico, ottenuta dalle simulazioni. 20 3.1.5 Calcolo del campo magnetico minimo Hmin Ipotizzando in ingresso al sistema un campo magnetico omogeneo e sinusoidale, possiamo definire la tensione indotta ui sull’antenna del tag come ui = µ0 AN ωHeff (3.23) in cui Heff è il valore efficace del campo magnetico sinusoidale, ω è la sua pulsazione ed N e A sono rispettivamente il numero di spire e l’area della sezione di L2 [1]. Se ora si sostituisce la (3.23) al posto di ωM i1 al numeratore della (3.20) si ricava u2 = ωµ0 Heff AN 1 + (ωL2 + R2 )( R1L + ωC2 ) (3.24) A questo punto, risolvendo per Heff si ricava la formula del campo minimo q R2 2 2 2 2 u2 ( ωL RL + ωR2 C2 ) + (1 − ω L2 C2 + RL ) (3.25) Hmin = ωµ0 N A Utilizzando i valori di L2 , C2 e A precedentemente calcolati, utilizzando sempre N = 3, ω = 2π · 13.56 · 106 , ipotizzando R2 = 5 Ω, RL = 200 Ω e imponendo come minima tensione di funzionamento 500 mV per avere un buon margine, riusciamo a calcolare: Hmin = 310 mA/m (3.26) valore che risulta essere di poco superiore al minimo valore di campo permesso da normativa (150 mA/m) e di molto inferiore al valore massimo (5 A/m): a prescindere dall’antenna del reader, perciò, il circuito sfrutta al meglio tutto il range di valori di campo magnetico normalmente disponibili durante il suo funzionamento. 3.2 Rettificatore La tensione indotta, prelevata ai capi dell’antenna, può essere scritta come 2πt vin (t) = Vp sin(2πf t) = Vp sin (3.27) T in cui f è la frequenza della portante (13.56 MHz) e T è il periodo corrispondente. Il passo successivo, per la creazione dell’alimentatore, è quello di riuscire a trasformare la sinusoide sopra citata in una tensione continua. 21 3.2.1 Principio di funzionamento teorico Per far fronte a questa esigenza, la maggior parte degli RFID in commercio, impiega strutture basate sul classico ponte di diodi a doppia-semionda, il cui schema è riportato in Fig. 3.7. Il funzionamento di questo circuito si basa sull’accensione/spegnimento a coppie, dei quattro diodi presenti nello schema. Trascurando le tensioni di soglia e le possibili perdite, durante la semionda positiva della vin , la corrente può scorrere nella maglia formata dai diodi D3 , D2 e dal condensatore di carico CL , caricando quest’ultimo alla tensione di picco di vin . Durante la semionda negativa, invece, a condurre sono i diodi D1 e D4 , che vanno a caricare il condensatore in uscita sempre alla stessa tensione e, cosa più importante, sempre con la stessa polarità. Si va cosı̀ a creare una tensione continua sull’uscita partendo da una sinusoidale in ingresso. Nella pratica, il principio di funzionamento è lo stesso, ma le soglie dei dispositivi e le perdite dovute a parassiti, o a non idealità circuitali, non sono più trascurabili. Per quanto riguarda le prime, la presenza di una soglia di accensione dei diodi, fa in modo che la tensione massima raggiungibile dal carico Vout,max non possa mai superare il valore Vout,max = Vp − 2 × Vth (3.28) in cui Vth è la tensione di soglia dei diodi e Vp è la tensione di picco assunta dalla semionda in ingresso [9]. Inoltre, per questo motivo, esiste un valore minimo, pari a 2 × Vth , che il segnale in ingresso deve assumere per garantire l’accensione del raddrizzatore e al di sotto del quale, come si deduce dalla (3.28), la tensione in uscita è nulla. Le perdite invece, rappresentabili da una resistenza o da un generatore di corrente collegati sull’uscita, causano una scarica costante del condensatore che si manifesta sulla tensione di uscita come un’ondulazione chiamata ripple, la cui ampiezza viene indicata con Vr . Dall’istante in cui la semionda positiva presenta il suo picco massimo, i diodi D3 e D2 non conducono più, poiché la tensione ai loro capi è inferiore alla tensione di soglia e perciò il condensatore inizia a scaricarsi. La scarica continua fino a che il modulo della semionda negativa non supera un certo valore di tensione, in modo da far accendere l’altra coppia di diodi e ricaricare il condensatore fino a Vout,max . L’andamento della tensione di uscita è mostrato in Fig. 3.6. In questo processo di carica e scarica, entrano in gioco diversi fattori: in particolare, l’ampiezza del ripple, dipende dai valori che CL e RL assumono rispetto alla frequenza del segnale in ingresso. Questi ultimi due parametri, a parità di corrente di carico, definiscono infatti la costante di tempo τ = RL CL 22 (3.29) Figura 3.6: Andamento della tensione di ripple che entra in gioco nel periodo di non conduzione dei diodi nella forma vo = Vout,max · e −R t L CL (3.30) Da qui, con pochi passaggi, è facile arrivare alla relazione tra Vr e i parametri CL , RL e f = 1/T T (3.31) 2CL RL Si nota quindi che maggiore è τ e minore sarà l’ampiezza dell’oscillazione, in quanto in ogni ciclo di ricarica, che nel caso del ponte a doppia semionda ha durata T /2, CL si scaricherà in maniera più contenuta e la vo rimarrà prossima al suo valore massimo [9]. Vr = Vp 3.2.2 Principali tipologie e relative caratteristiche Per quanto riguarda il sistema in questione, due sono gli aspetti da tenere bene in considerazione: la minima tensione utile in ingresso e l’efficienza di conversione. La prima definisce la soglia di accensione del rettificatore e, dal nostro punto di vista, fornisce una prima limitazione in termini di range di funzionamento; la seconda è stata invece il parametro principale su cui si è basata la scelta progettuale effettuata. La PCE (Power Conversion Efficiency), è un parametro definito dal rapporto Pout (3.32) Pin con Pout e Pin che rappresentano rispettivamente la potenza utile fornita al carico e la potenza in ingresso ricevuta dall’antenna. Nella maggior parte dei PCE = 23 Figura 3.7: Ponte di diodi a doppia semionda casi essa è dichiarata in percentuale e fornisce un’idea del consumo energetico del circuito al quale fa riferimento [2]. Considerato il fatto che il tag deve essere un dispositivo di facile integrazione e a basso costo, il rettificatore a singolo diodo è stato scartato in partenza in quanto esso è caratterizzato da una PCE molto bassa. Sono invece state considerate la normale struttura a ponte (Fig. 3.8) e quella a gate incrociati (Fig. 3.9), entrambe utilizzanti transistor MOS connessi a diodo. La topologia a gate incrociati presenta un valore di soglia minore e quindi, a parità di tensione in ingresso, fornisce una tensione più elevata in uscita. La struttura a ponte di diodi, invece, riesce a fornire un valore di PCE costante sia per carichi piccoli che per quelli più impegnativi. Per quest’ultima struttura, della quale è riportato un esempio in Fig. 3.8, il consumo di potenza può essere diviso in tre parti: 1. la potenza dissipata dalla resistenza di canale dei transistor MA ed MB collegati a CL , mentre caricano il nodo di uscita alla Vout,max , rispettivamente durante la semionda positiva e quella negativa; 2. la potenza consumata dalla resistenza di carico; 3. la potenza consumata dai diodi formati dalla giunzione Bulk-Source dei quattro MOS, che creano le perdite di leakage presenti in ogni semiperiodo. Per la topologia a gate incrociati di Fig. 3.9, invece, il consumo di potenza si divide in quattro parti: 24 Figura 3.8: Struttura a ponte semplice NMOS Figura 3.9: Struttura con connessione cross-gate NMOS 25 1, 2, 3 come nel caso precedente; 4 la potenza consumata dalle resistenze di canale dei transistor M3 ed M4 che, in questo caso, sono anch’essi attraversati dalla corrente di carico. Entrambe le tipologie possono essere implementate interamente con transistor NMOS o PMOS, oppure possono utilizzare la tecnologia CMOS. Ciascuna delle possibili implementazioni fornisce caratteristiche differenti, che possono essere sfruttate a seconda delle necessità. La struttura semplice a NMOS presenta una elevata soglia di accensione e una modesta PCE, che però aumenta all’aumentare della resistenza d’uscita, in quanto in questo modo si diminuiscono le perdite e si sfrutta meglio la potenza in ingresso. L’efficienza ottenibile non è comunque superiore al 30%. La struttura, sempre NMOS, ma con i gate incrociati, ha una tensione di soglia minore, ma anche una PCE inferiore, che presenta un picco per bassi valori di resistenza di carico, per scendere poi rapidamente una volta superato quel valore. In questo caso si arriva ad efficienze medie del 21%. Entrambe le strutture realizzate con PMOS presentano circa le stesse caratteristiche delle precedenti, e si differenziano solamente per minori perdite di leakage nella topologia normale e per una relazione Vout vs. Vin più lineare in quella a gate incrociati. I contributi di leakage vengono diminuiti in quanto il bulk non è più connesso a massa ma alla tensione di uscita, che quindi, essendo sempre la più positiva, mantiene tutti i diodi di giunzione Bulk-Source sempre in condizione di polarizzazione inversa. Anche in questi due casi i valori di PCE non superano comunque il 40%. La realizzazione CMOS risulta la migliore in termini di efficienza. 3.2.3 Raddrizzatore CMOS con gate incrociati Tra tutte le configurazioni possibili, la scelta è ricaduta su un raddrizzatore CMOS con connessione a gate incrociati, il cui schema è riportato in Fig. 3.10. A differenza di tutte le altre topologie, essa presenta una bassissima tensione di soglia e un’efficienza di molto superiore alla media, che in alcuni casi può superare il 50%. In questo caso, come si può dedurre dallo schema elettrico, i dispositivi accoppiati sono M2 /M3 ed M1 /M4 . Durante la semionda positiva M2 ed M3 vedono rispettivamente una vgs positiva ed una negativa, si accendono e connettono rispettivamente in2 a massa e in1 a Vrect , permettendo cosı̀ la carica di CL alla tensione Vout,max . Questa tensione risulta minore di Vp , ma è comunque maggiore rispetto alle altre tipologie. Durante la semionda negativa invece la coppia M2 /M3 è spenta, mentre la coppia M1 /M4 è accesa e permette di compiere lo stesso processo di prima, invertendo la polarità della semionda stessa da negativa a positiva. 26 Figura 3.10: Raddrizzatore CMOS con connessione cross-gate Per quanto riguarda la progettazione di questa parte circuitale, le simulazioni sono state fondamentali, poiché hanno permesso di valutare il comportamento del circuito nel suo complesso, e quindi di andare ad individuare e modificare tutti i parametri che ne influenzano le prestazioni [2]. Teoricamente ci si è basati su due principali fattori: • la resistenza superficiale dei transistor dipende dalla tensione in ingresso del rettificatore; per questo, considerando variazioni di vgs dalla Vth (∼ 400 mV) fino alla massima tensione consentita dalla tecnologia (∼ 1.8 V), i valori di rds possono variare anche di due ordini di grandezza; • maggiori sono le dimensioni dei transistor e minori risultano le resistenze superficiali, che, a parità di corrente di carico, diminuiscono a loro volta le cadute di tensione sui MOS, permettendo al rettificatore di fornire maggiori tensioni in uscita. D’altro canto, utilizzare transistor grandi significa avere a che fare con grandi capacità di gate da caricare e quindi un circuito più lento e meno efficiente in termini di consumi. Le dimensioni definitive e i risultati delle simulazioni per il rettificatore sono presentati nel Capitolo 5 nel paragrafo ad esso dedicato. 3.3 Circuito di protezione Esistono due tipi di eventi che, seppur aventi origini differenti, possono provocare un danneggiamento fisico del chip: una scarica elettrostatica e un’eccessiva differenza di potenziale indotta sull’antenna del tag. Per questo, risulta d’obbligo inserire nel sistema delle opportune misure di sicurezza che, 27 al verificarsi di questi eventi, preservino integro il dispositivo. Ogni protezione deve comunque avere il minimo impatto sul corretto funzionamento del circuito, non peggiorandone le prestazioni. Una semplice soluzione potrebbe essere quella di inserire uno o più diodi Zener di clamping in parallelo all’antenna, in modo da bloccare la tensione in ingresso ad un valore prefissato dalla loro soglia inversa. Siccome però la tecnologia utilizzata non permette di realizzare diodi Zener, la realizzazione di un simile circuito non risulta possibile, cosı̀ come l’utilizzo di un analogo circuito realizzato utilizzando più diodi normali con polarizzazione diretta (disponibili nella tecnologia) connessi in serie. Infatti, anche sottosoglia, i diodi inseriti in questo modo, presentano correnti di perdita che il sistema non riesce ad erogare, finendo per non lavorare nel modo più appropriato o addirittura rischiando il completo spegnimento. Si è dunque optato per un’altra soluzione. In un sistema RFID come quello qui trattato, le ESD (Electrostatic Discharge) sono dovute alle cariche elettrostatiche che possono accumularsi sulla superficie del chip durante la fase di realizzazione, integrazione o successiva manipolazione. Questo rapido accumulo di cariche può portare al breakdown del dispositivo mediante una forte scarica di corrente. Per evitare ciò, si inserisce un percorso a bassa resistenza verso massa, che si presenti solo in presenza di elevate tensioni e che dia modo alle cariche elettrostatiche presenti, di scaricarsi senza produrre danni [5]. Il circuito utilizzato per questo scopo è la parte a destra della linea tratteggiata dello schematico di Fig. 3.11. Figura 3.11: Schematico del circuito di protezione in ingresso Durante una scarica elettrostatica, la tensione |in1 − in2 | cresce molto velocemente. Di norma, il filtro RLC in ingresso non è abbastanza rapido da accorgersene, ma la presenza dei diodi M5 , M6 , M7 , M8 permette alla 28 tensione Vrect di cambiare repentinamente. A quel punto, il condensatore CC trasmette il fronte di salita a M9 che, accendendosi, crea il percorso a bassa resistenza verso massa e neutralizza la scarica. Una volta estinta la ESD, M9 viene interdetto da RC . Quando invece il tag è troppo vicino al reader, il livello di tensione indotta sull’antenna, e quindi ai capi dei MOS del rettificatore, risulta pericolosamente elevato. Per come sono collegati i transistor, la tensione dell’antenna, rappresenta la vgs dei transistor del raddrizzatore, che, data la tecnologia utilizzata, non può superare 1.8 V. Per evitare la rottura dei componenti, è stata aggiunta una parte di circuito di protezione, rappresentata in Fig. 3.11 nella sezione a sinistra della linea tratteggiata. Fino a che la tensione Vrect non supera un determinato valore, definito dalla somma delle soglie dei due diodi in serie, il dispositivo di sicurezza non viene attivato e il sistema funziona regolarmente. Ogni volta che la tensione Vrect supera il valore prefissato, il nodo A sale a valori positivi e porta i transistor M5 ed M6 in uno stato più conduttivo. Questo percorso a bassa impedenza verso massa fa aumentare la corrente di carico vista dall’antenna la quale, tramite la sua resistenza serie, fa diminuire il livello della Vrect presente sui gate dei MOS. Maggiore è il livello della Vrect rispetto alla soglia predefinita, maggiore sarà la corrente erogata dall’antenna, mantenendo cosı̀ il livello di tensione indotta al di sotto del valore critico. 29 Capitolo 4 Pompa di carica e Regolatore di Tensione LDO La tensione in uscita da qualsiasi rettificatore, presenta normalmente troppe fluttuazioni per poter essere utilizzata direttamente come alimentazione di un circuito elettronico. Inoltre, almeno nel caso considerato, il livello ottenuto dopo la fase di raddrizzamento, non è necessariamente quello desiderato e varia con la tensione indotta sull’antenna del tag. Per ottenere un segnale di tensione stabile ad un valore prefissato e scevro da ogni ripple, è necessario gestire il segnale proveniente dal raddrizzatore attraverso un sistema di regolazione, qui implementato tramite una pompa di carica retroazionata. 4.1 Generalità e principio di funzionamento Le cosiddette pompe di carica sono circuiti che forniscono in uscita una tensione maggiore di quella da loro utilizzata come alimentazione [3]. Per vedere come questo sia possibile, si analizzi il circuito di Fig. 4.1. Figura 4.1: Raddopiatore di tensione ideale 30 Durante la fase φ, gli interruttori S1 e S3 sono chiusi e la capacità viene caricata alla tensione VDD . Successivamente, mentre i primi due interruttori vengono aperti, S2 viene chiuso e il condensatore, che mantiene la carica immagazzinata nella fase precedente, viene collegato nuovamente alla VDD . Questo significa che durante la fase φ (Vout − VDD )C = VDD C (4.1) Vout = 2VDD (4.2) o meglio Quindi, in assenza di un carico in continua, la tensione di uscita generata è il doppio di quella in ingresso. Per analizzare cosa avviene in presenza di un carico, occorre modificare lo schematico precedente, aggiungendo un condensatore e un resistore, come mostrato in Fig. 4.2. Figura 4.2: Raddoppiatore di tensione reale In questo caso, la tensione di uscita in assenza di RL è data da Vout = C 2VDD C + Cout (4.3) Inoltre, in presenza di RL , si genera sull’uscita una tensione di ripple Vr , che può essere trascurata rispetto alla Vout solamente utilizzando una Cout sufficientemente grande. Ottenere fattori di moltiplicazione della tensione maggiori dei due è possibile collegando in cascata all’ingresso più di un condensatore in serie. 31 4.2 Tipologie di base Le prime pompe di carica proposte furono quelle di Cockcroft e Walton con le quali si riuscirono ad ottenere tensioni vicine agli 800.000 V che furono utilizzate per studiare alcune strutture atomiche della materia. Queste pompe di carica erano del tipo mostrato in Fig. 4.3. Figura 4.3: Moltiplicatore di tensione di Cockcroft-Walton Come si può notare, i tre condensatori CA , CB e CC sono connessi in serie e vedono in parallelo le capacità C1 e C2 attraverso gli interruttori. Inoltre CA è polarizzato costantemente alla VDD e i condensatori hanno tutti lo stesso valore C. Durante la fase φ, C1 è connesso in parallelo a CA e viene caricato alla VDD . Quando gli interruttori cambiano posizione durante la fase successiva φ, C1 trasmette metà della sua carica a CB e rimangono caricati entrambi a VDD /2. Nel ciclo ancora successivo saranno CB e C2 a condividere le cariche e a caricarsi a VDD /4 mentre C1 verrà caricato nuovamente a VDD . È chiaro che, se questo processo viene ripetuto per qualche ciclo, le cariche vengono trasferite su tutti i condensatori fino a creare una tensione pari a 3VDD . Questo principio è in teoria banalmente estendibile e, aumentando il numero dei condensatori in serie, il livello della tensione in uscita potrebbe crescere all’infinito. Tuttavia, in pratica, questa tecnica risulta altamente inefficiente per realizzazioni integrate, sia in termini di area di silicio occupata dalle capacità, sia per quanto riguarda l’impedenza d’uscita, che continua ad aumentare via via che si aggiungono nuovi stadi. Un secondo tipo di pompa di carica, ideata proprio per sfruttare al meglio le potenzialità della microelettronica, è stata progettata da Dickson: su questo modello si basano la maggior parte delle pompe di carica esistenti in 32 letteratura. Lo schematico della pompa di carica di Dickson è rappresentato in Fig. 4.4. Figura 4.4: Pompa di carica di Dickson Il circuito funziona con due segnali di clock, φ e φ, i quali lavorano in controfase e variano tra la tensione Vφ e 0. I diodi operano come interruttori a fasi alterne e presentano una tensione di soglia pari a Vd . Per completezza, vengono inoltre mostrate le capacità parassita, indicate con CS , presenti ad ogni nodo del circuito. Trascurando le capacità parassite, si vede come il circuito operi pompando le cariche lungo il percorso creato dai diodi attraverso i condensatori C, che quindi vengono caricati e scaricati ad ogni ciclo di clock. Quando il clock della fase φ scende a 0, il diodo D1 conduce fino a che il potenziale sul nodo 1 raggiunge il valore (Vin − Vd ). Non appena la fase φ torna alta, la tensione al nodo 1 diventa Vin + (Vφ − Vd ). Questo causa l’accensione di D2 , che conduce fino a che la tensione sul nodo 2 arriva a Vin + (Vφ − Vd ) − Vd . Quando φ scende nuovamente la tensione al nodo 2 diventa Vin + 2(Vφ − Vd ). Dopo N iterazioni è facile ricavare la tensione di uscita come Vout = Vin + N (Vφ − Vd ) − Vd (4.4) Le capacità CS influiscono sul risultato finale riducendo la tensione traC sferita di un fattore C+C , che inserito nella (4.4) porta a: S C Vout = Vin + N Vφ − Vd − Vd (4.5) C + CS Se, oltre alle CS , teniamo conto di un carico in uscita, che assorba una corrente Iload , la tensione Vout viene ulteriormente ridotta e diventa Vout = Vin + N C C + CS N Iout Vφ − Vd − − Vd (C + CS )fφ (4.6) dalla quale risulta ovvio che la tensione viene effettivamente aumentata solo se 33 C N Iout Vφ − Vd − >0 C + CS (C + CS )fφ (4.7) A questo punto è utile definire due parametri che possono essere utilizzati per caratterizzare qualsiasi pompa di carica: la fluttuazione di tensione ∆V e il guadagno della pompa GV . Il primo rappresenta l’effettiva variazione di tensione che sussiste tra un nodo e l’altro del circuito e, nel caso della pompa di carica di Dickson, vale ∆V = C Iout Vφ − C + CS (C + CS )fosc (4.8) Il secondo, invece, è definito come GV = VN − VN −1 (4.9) che per la pompa di Dickson diventa GV = ∆V − Vd (4.10) Sfortunatamente, non appena la tensione di alimentazione decresce, scende anche il valore di Vφ disponibile e di conseguenza calano sia ∆V che GV . Per questo e per ovvi motivi di rendimento, questo tipo di pompa non è utilizzabile per sistemi operanti a basse tensioni. 4.3 Pompa di carica ad inverter CMOS La pompa di carica utilizzata in questo progetto è raffigurata in Fig. 4.5. Essa è lavora in due fasi, φ e φ, che pilotano una serie di latch impilati. Ciascun latch sfrutta come livello di riferimento l’uscita del precedente, per fornire in uscita un livello di tensione maggiorato del valore della tensione di pilotaggio VC . Prendendo come riferimento lo schematico di Fig. 4.5, il principio di funzionamento risulta abbastanza intuitivo: il segnale di clock del sistema RFID viene convertito nelle due fasi φ e φ dai due inverter di pilotaggio che, essendo alimentati tra VC e massa, forniscono in uscita due segnali in controfase che variano tra queste due ultime tensioni. Il latch, a questo punto, viene pilotato attraverso i condensatori CP in modo da caricare il condensatore d’uscita Cload alla tensione (VL + VC ), sfruttando alternativamente, a seconda del semiperiodo, la corrente in uscita dal primo o dal secondo inverter. Due sono le caratteristiche rilevanti per questo tipo di pompa di carica: la possibilità di avere il livello di tensione VC diverso dalla tensione di picco del clock e il modo in cui le due fasi φ e φ vengono generate. La prima facilita di molto l’inserimento di un sistema di controllo per la regolazione 34 Figura 4.5: Pompa di carica a inverter CMOS utilizzata della tensione di uscita, la seconda va a diminuire i consumi della pompa di carica, in quanto i tempi di ritardo esistenti tra le varie commutazioni fanno in modo che le due fasi non siano perfettamente sincronizzate e non sussistano nel circuito picchi di corrente dovuti a commutazioni simultanee. Un’analisi più approfondita del circuito può essere effettuata prendendo come riferimento la Fig. 4.6, in cui vengono mostrati gli andamenti delle correnti nelle due diverse fasi del clock, per una pompa ad inverter CMOS a due stadi. Ipotizzando inizialmente scariche tutte le capacità presenti nel circuito, quando il segnale CK = 1 e CK = 0, il flusso della corrente è quello rappresentato in verde e si verifica che: • i transistor in conduzione sono P2 , P3 , MN 1 , MN 3 , MP 2 , MP 4 ; tutti gli altri sono spenti; • CL , tramite CP 4 , tende a caricarsi alla tensione VC ; • CP 1 e CP 3 si caricano entrambi a VC /2 tramite la maglia formata da: P 3 → C P 3 → MP 2 → MN 3 → C P 1 → P 2 ; • il nodo X si trova conseguentemente a VC /2. Nella fase successiva, con CK = 0 e CK = 1 e la corrente schematizzata in rosso, troviamo che: 35 Figura 4.6: Andamento delle correnti nella pompa di carica • i transistor in conduzione sono P1 , P4 , MN 2 , MN 4 , MP 1 , MP 3 ; tutti gli altri sono spenti; • CP 3 è cortocircuitato a massa da P3 e MN 2 e si scarica pressoché completamente; • CP 2 e CP 4 vengono caricati a VC /2 tramite la maglia: P 1 → C P 2 → MP 1 → MN 4 → C P 4 → P 4 ; • CL vede ai suoi capi la serie di VC +VCP 1 con VCP 1 = VC /2 dal periodo precedente, e quindi tende a salire verso 23 VC ; • il nodo X è sempre a VC /2. Al terzo colpo di clock, si ripresenta la situazione iniziale, con la differenza che CP 1 , caricato a VC /2, si trova collegato in serie CP 3 , che invece, è stato scaricato completamente nella fase precedente. In questo modo, i due condensatori condividono la carica e, avendo la stessa capacità, si portano entrambi a VC /4 (Fig. 4.7). Ora, considerando il principio di sovrapposizione degli effetti, il nodo X, che normalmente si troverebbe a VC /2, si carica invece a VX = VC 3 VC + = VC 2 4 4 36 Figura 4.7: Circuito equivalente della pompa di carica Risulta chiaro come, nei cicli successivi, la tensione al nodo intermedio X salga costantemente verso il valore VC , presentando un comportamento asintotico del tipo: (2n − 1) · VC = VC (4.11) n→+∞ 2n Si può considerare la pompa di carica a regime quando, dopo un certo numero di cicli, il nodo intermedio X si porta a una tensione prossima a VC , permettendo cosı̀ a CP 1 e CP 4 di rimanere carichi e, tramite gli inverter, di caricare a loro volta CL al doppio della tensione di pilotaggio (2VC ). La trattazione è facilmente estendibile a pompe di carica con un maggiore numero di stadi. Per quanto riguarda le perdite, esse possono essere divise in due categorie: perdite per conduzione e perdite per commutazione. Le prime, sono dovute alle cadute di tensione sulle RON dei transistor, i quali, appena dopo ogni commutazione si portano in regione lineare e presentano perciò delle resistenze di canale pari a: VX = lim RON = L µCOX W (VGS − VT H ) (4.12) in cui µ è la mobilità superficiale degli elettroni o delle lacune, COX è la capacità per unità di area dell’ossido di gate, W e L rappresentano rispettivamente la larghezza e la lunghezza dei transistor, VGS è la tensione presente tra gate e source e VT H è la tensione di soglia. Tralasciando il valore effettivo della corrente che scorre nella pompa di carica ad ogni ciclo di clock, le perdite totali per conduzione avranno una forma del tipo 37 PC = 2 N Ipompa RON 2 N Ipompa L = µCOX W (VGS − VT H ) (4.13) con il coefficiente N che dipende dal modo in cui Ipompa si distribuisce e scorre nei rami del circuito. Importante è notare la dipendenza di PC da 1/W . Le perdite dinamiche sono invece dovute alla potenza utilizzata per far commutare i transistor tra interdizione e regione lineare e dipendono da due fattori principali: 1. capacità di gate: assumendo tutte uguali le cadute di tensione sui transistor e le loro dimensioni otteniamo le perdite dinamiche come PG = 8fs 1 2 CG VG2 = 4fs CG VG2 (4.14) in cui CG = W LCOX rappresenta la capacità di gate, fs è la frequenza di clock e VG è la tensione presente sul gate. 2. capacità drain-source: anche se di minore entità, le perdite dovute a questa capacità influiscono sulle perdite dinamiche totali in relazione al valore di W . Dai due punti precedenti risulta chiaro come perdite dinamiche e per conduzione dipendano in maniera inversa dal parametro W e di conseguenza esista un valore ottimo di W per cui le perdite siano entrambe minimizzate. Inoltre, si nota come le perdite, e quindi il guadagno della pompa di carica, dipendano anche dalla frequenza del clock fs e dal numero di stadi, che, se troppo elevato, fa aumentare inutilmente il fattore N delle perdite statiche. Anche in questo caso le simulazioni si sono rivelate lo strumento migliore con il quale affrontare il problema, sia per quanto riguarda il dimensionamento dei componenti, sia per quanto riguarda l’analisi dei consumi, che comunque, per questa parte di progetto, sono stati considerati di importanza secondaria. Anche in questo caso, tutti i risultati e le scelte progettuali sono riportati nel Capitolo 5. 4.4 Sistema di controllo retroazionato Come riportato nelle specifiche di progetto, i livelli di tensione necessari al corretto funzionamento del sistema sono due: 1.8 V per la trasmissione dati e 3.3 V per la ricarica della batteria. Per il modo in cui la pompa di carica è costruita, il livello della tensione di uscita cambia al variare della tensione in ingresso (vin ) e in base alla quantità di corrente erogata (IL ). Diventa perciò indispensabile un sistema di controllo che stabilizzi la 38 Figura 4.8: Pompa di carica retroazionata tensione ai valori prefissati, nei tempi previsti dal protocollo di trasmissione e per qualsiasi valore assunto da vin o da IL . Il sistema implementato in questo progetto consta di un amplificatore operazionale che, eseguendo un confronto tra una tensione di riferimento Vref e una frazione Vp della tensione di uscita Vout , ottenuta dalla Vout stessa tramite un partitore, fornisce in uscita la tensione VC , utilizzata come alimentazione degli inverter di pilotaggio. Uno schema generico della pompa di carica retroazionata con partitore capacitivo è rappresentato in Fig. 4.8. Una volta definito il livello del riferimento Vref , che in questo caso proviene da un circuito band-gap integrato già progettato per questo sistema RFID, occorre progettare in maniera adeguata il partitore, in modo che, quando la Vout raggiunge uno dei valori prefissati, in ingresso all’amplificatore operazionale la tensione Vp eguagli Vref . In questo modo l’amplificatore operazionale fornirà in uscita: VC > 0 se Vref > Vp VC = 0 se Vref 6 Vp regolando la tensione di uscita della pompa di carica ad un valore dipendente dal partitore utilizzato. A questo punto, gli aspetti principali da considerare sono: • il dimensionamento del partitore; • la progettazione di un amplificatore operazionale che abbia un guadagno e una banda adeguati ad annullare qualunque variazione della Vout . Per quanto riguarda il primo punto, è importante scegliere correttamente la tipologia del partitore (resistivo o capacitivo). Il partitore capacitivo 39 permette di ridurre notevolmente i consumi, in quanto non dissipa potenza statica, ma presenta lo svantaggio di dover essere resettato tramite un interruttore che, collegato in parallelo, va a creare dei percorsi circuitali parassiti tra il nodo intermedio del partitore e altri punti del circuito. Questi collegamenti modificano la carica presente nelle capacità che, essendo teoricamente isolate durante tutto il funzionamento del sistema, non permettono né il ripristino dei corretti valori, né la corretta azione del sistema di controllo. Avendo quest’ultimo una retroazione negativa infatti, a seconda del verso della corrente parassita, la carica continua ad aumentare o a diminuire costantemente, e ciò porta ad un aumento o ad una diminuzione costante della tensione d’uscita che, per tempi già dell’ordine dei secondi, si scosta di molto dai valori richiesti da specifica. D’altra parte, un partitore resistivo consuma costantemente una certa potenza statica e quindi peggiora i consumi, ma in qualunque caso, non può presentare scompensi di carica e quindi non disturba il funzionamento del sistema di controllo. Per questi motivi, è stato implementato un partitore resistivo, dimensionato in modo tale da fornire i livelli desiderati, non compromettendo i consumi del sistema. Mantenendo valori di resistenza elevati per limitare le correnti di perdita e imponendo quindi Rp = 10 MΩ, avendo già definito il livello di riferimento imposto dal riferimento band-gap pari a 500 mV e i due livelli d’uscita a 1.8 V e 3.3 V, il calcolo risulta: 0.5 = 1.8 · Rp1 (107 + Rp1 ) 0.5 · (107 + Rp1 ) = 1.8 · Rp1 0.5 · 107 = (1.8 − 0.5) · Rp1 0.5 Rp1 = · 107 = 3.8 MΩ 1.3 (4.15) per Vout = 1.8 V, e 0.5 = 3.3 · Rp2 + Rp2 ) (107 0.5 · (107 + Rp2 ) = 3.3 · Rp2 0.5 · 107 = (3.3 − 0.5) · Rp2 0.5 Rp2 = · 107 = 1.8 MΩ 2.8 (4.16) per Vout = 3.3 V. 4.4.1 Amplificatore operazionale integrato L’amplificatore operazionale realizzato per il sistema di regolazione è basato su un’architettura a due stadi: uno stadio differenziale seguito da uno stadio 40 Figura 4.9: Amplificatore operazionale integrato common-source PMOS [10]. Lo schema dell’amplificatore è riportato in Fig. 4.9. Come si può notare dallo schematico, sono stati introdotti alcuni transistor per permettere di spegnere l’amplificatore (power-down) tramite i segnali P D+ e P D−, in modo da non consumare potenza quando il circuito non è attivo. I parametri fondamentali da tener in considerazione per la progettazione di questo blocco sono stati il guadagno, la banda e l’offset sistematico. In tutto il sistema realizzato, questo amplificatore operazionale è stato usato per tre volte: per i controlli delle due pompe di carica e per quello del regolatore LDO. Viste le differenti specifiche per le differenti tensioni di uscita (1.8 V e 3.3 V dalle pompe di carica, 1.8 V dal regolatore LDO), la struttura utilizzata è rimasta la stessa, ma le dimensioni dei componenti sono state variate in modo da soddisfare precisamente le specifiche in ciascun caso. I risultati delle simulazioni e il dimensionamento dei transistor sono riportati nel Capitolo 5. 4.5 Regolatore di tensione LDO Per il funzionamento del sistema in zone distanti dal reader e comunque per portare la tensione della batteria al valore richiesto per il funzionamento del circuito, è stato inserito un regolatore di tensione Low Drop-Out (LDO) 41 che appunto, partendo dalla tensione della batteria a 3.3V, fornisce una alimentazione a 1.8 V stabile, per qualsiasi valore assunto da vin o da IL . Grazie alla presenza del transistor di controllo, che diminuisce la caduta di tensione interna al regolatore, gli LDO, a differenza dei normali regolatori lineari, presentano un’efficienza molto elevata. D’altra parte però, questo tipo di regolatore, è nominalmente caratterizzato da una debole stabilità: a causa del secondo polo introdotto dall’impedenza di carico, infatti, il margine di fase viene facilmente peggiorato di molto e viene resa necessaria una compensazione in frequenza, solitamente realizzata da una grande capacità posta in uscita [11]. I regolatori LDO più moderni, hanno eliminato questa scomoda capacità creando topologie circuitali più compatte, che prevedono un condensatore integrato dalle dimensioni contenutissime e una rete di compensazione per il taglio in frequenza. Ciò nonostante, il progetto in cui andrà inserito il sistema di alimentazione elaborato in questa tesi, non presenta alcun problema di spazio e per questo, è stata scelta la classica tipologia di LDO con capacità di compensazione esterna. Lo schema circuitale del regolatore LDO realizzato è riportato in Fig. 4.10. Figura 4.10: Regolatore di tensione Low Drop-Out Anche per il regolatore LDO il partitore di tensione utilizzato per la retroazione è stato scelto resistivo, in modo da non introdurre drift sulla tensione d’uscita, dovuto alle perdite di carica in un partitore capacitivo. Parametri importanti del regolatore sono la resistenza di uscita Rout e le dimensioni del condensatore, che, per quanto ininfluenti per il progetto, non 42 devono comunque diventare eccessive. La resistenza di uscita, in questo caso è data dal transistor M0 che quindi è stato reso il meno resistivo possibile mantenendo abbastanza largo il canale (W ). Sulle dimensioni del condensatore invece hanno influito la minima e la massima corrente di carico imponibile al regolatore LDO: infatti, mantenendo ferme le dimensioni dei transistor, la stabilità del circuito dipende fortemente dal livello di corrente erogata in uscita. I risultati sono riportati nel Capitolo 5. 43 Capitolo 5 Simulazioni ed ottimizzazione In questo capitolo verranno presentati i metodi di simulazione e i relativi risultati per ogni blocco circuitale realizzato. In particolare saranno descritti gli schemi circuitali utilizzati, il dimensionamento dei componenti e tutti gli andamenti ritenuti importanti per ogni funzionalità del sistema. 5.1 Rettificatore e protezioni Le simulazioni eseguite per la progettazione del rettificatore sono state mirate, come precedentemente menzionato, alla massimizzazione del rendimento in termini di potenza. Inoltre, essendo questo il blocco circuitale dal quale si attinge l’intera quantità di corrente necessaria all’alimentazione del sistema, particolare attenzione è stata portata alla minimizzazione del valore della resistenza di uscita. Considerando che il rettificatore lavora normalmente con il circuito di protezioni collegato, tutte le simulazioni sono state eseguite comprendendo anche tale circuito, in modo da rendersi conto del suo reale effetto sul sistema. Ciononostante, in un primo momento, le simulazioni sono state effettuate inducendo tensioni in ingresso non superiori a 1 V, in modo da non far entrare in funzione le protezioni ed analizzare solamente il comportamento del ponte. Una volta inserita, in ingresso al rettificatore di Fig. 3.10, una modellizzazione dell’antenna con relativa tensione indotta, il carico è stato rappresentato da un generatore di corrente continua Iload e un condensatore CL . Quest’ultimo, in un primo momento, è stato dimensionato molto grande, 1 nF per l’esattezza, ed è poi stato ridimensionato una volta ottimizzato il circuito nel suo complesso. Tramite le simulazioni sono state effettuate: 44 • le analisi degli andamenti della tensione di uscita in base alla corrente di carico; • le valutazioni dei minimi valori di tensione di soglia per l’accensione del rettificatore; • le analisi dei rendimenti in termini di potenza. Di seguito sono riportati gli andamenti sopra elencati con le relative osservazioni, inoltre viene riportata anche la tensione d’uscita in funzione della larghezza di canale W dei transistor utilizzati nel rettificatore. 2.5 2 Vrect [V] 1.5 1 0.5 0 0 100 200 300 400 500 600 700 Iload [uA] Figura 5.1: Vrect vs. Iload per il raddrizzatore Come si può notare dalla Fig. 5.1, a causa della resistenza d’uscita del rettificatore, la tensione d’uscita disponibile diminuisce al crescere della corrente di carico. In particolare, in un caso come questo in cui Vind = 400 mV e 0 < Iload < 700µA, la tensione rimane ad un livello ragionevole solo per Iload inferiori ai 600 µA, dopodiché risulta inutilizzabile. Nel grafico di Fig. 5.2, invece, si nota innanzitutto come il circuito di protezione vada a bloccare il livello di tensione d’ingresso in modo che l’uscita non diverga per valori troppo alti di Vind e poi come il raddrizzatore abbia effettivamente una tensione di accensione minima al di sotto della quale esso non riesce a fornire tensione Vout in uscita e risulti praticamente spento. Per ottenere la curva di efficienza PCE è stata effettuata un’analisi parametrica in cui, avendo posto il raddrizzatore in un tipico punto di lavoro con Vind = 400 mV e Iload = 500 µA, al variare del W dei transistor, si è valutata la potenza in ingresso e quella di uscita. La prima è stata calcolata come 45 Figura 5.2: Vrect vs. Vind Figura 5.3: PCE vs. W dei transistor del raddrizzatore 46 Figura 5.4: Vout vs. W dei transistor del raddrizzatore Pin 1 = T2 − T1 Z T2 Vind × Iind · dt (5.1) T1 con Vind e Iind che rappresentano rispettivamente la tensione e la corrente indotte dal reader sull’antenna del tag; la seconda come Pout = 1 T2 − T1 Z T2 Vrect × Iload · dt (5.2) T1 con il solito significato per le variabili. Analizzando in maniera incrociata l’andamento della PCE e della Vout al variare delle dimensioni dei transistor è stato possibile definire le dimensioni ottime del W dei vari transistor. Si nota in effetti che la PCE aumenta all’aumentare del W dei PMOS e al diminuire del W degli NMOS, mentre la tensione di uscita va esattamente al contrario: per questo sono state scelte delle dimensioni intermedie che stabilissero un compromesso tra rendimento e massimo valore di Vout . I valori ottimali delle lunghezze di canale L, invece, sono stati scelti in modo da massimizzare la Roff dei transistor e portare al minimo le perdite. Le dimensioni utilizzate sono riportate in Tab. 5.1. Una volta ottimizzato il circuito del rettificatore, sono state eseguite le simulazioni per la progettazione del circuito di protezione, per il dimensionamento del quale ci si è basati principalmente su due fattori: • la tensione in ingresso al rettificatore non deve superare il valore critico di 1.8 V; 47 • i valori della tensione raddrizzata in uscita non devono risentire della presenza del circuito di protezione. Dopo alcune simulazioni si è giunti alla conclusione di limitare la Vind vista dopo il filtro di risonanza in ingresso, ad un valore di circa 2 V e di utilizzare come ingresso differenziale del raddrizzatore dei transistor a doppio strato di ossido di gate, che sopportassero Vgs fino a 2.4 V. Infatti, limitando la tensione in ingresso a valori minori di 2 V, quando la Vind corrisponde al minimo livello di soglia del rettificatore, la corrente di carico erogabile scende al di sotto del minimo consentito da specifica, compromettendo il funzionamento dell’intero sistema. Transistor L[µm] W[µm] M1,2 M3,4 M5−9 1.98 0.48 0.180 5 30 300 Tabella 5.1: Dimensioni dei transistor del rettificatore e delle protezioni 5.2 Pompa di carica Gli obiettivi da raggiugere per la progettazione della pompa di carica, sono stati quelli espressi dalle specifiche di progetto che definiscono i livelli di tensione e di corrente di carico necessari al funzionamento del sistema. I livelli desiderati sono due: Carica batteria: 3.3 V con una corrente di carico inferiore a 100 µA; Trasmissione dati: 1.8 V con una corrente di almeno 150 µA. Sin dalle prime simulazioni è risultato chiaro che una sola pompa di carica, ottimizzata per un livello particolare, non poteva essere utilizzata anche per l’altro. In particolare, si è visto che una pompa di carica a 3 stadi è in grado di fornire in modo preciso 1.8 V con 150 µA, ma non riesce a raggiungere 3.3 V neppure con deboli correnti di carico, in quanto l’amplificatore operazionale del sistema di regolazione, non presenta una tensione di uscita sufficientemente alta. D’altra parte, una pompa di carica a 4 stadi, raggiunge i 3.3 V con facilità ma non funziona correttamente quando la Vout richiesta è di 1.8 V e la Iload supera i 100 µA. Siccome le due tensioni non servono ad assolvere la stessa funzione, non devono necessariamente essere fornite nello stesso punto del circuito, né tanto meno nello stesso istante di tempo. Per questo, è stato possibile realizzare una 48 struttura formata da due pompe di carica ad inverter CMOS completamente indipendenti che, comandate da un’opportuna logica di controllo, sono in grado di fornire i livelli d’uscita desiderati nei tempi stabiliti dal protocollo di trasmissione utilizzato. In un primo tempo, le simulazioni sono quindi state eseguite sulle singole pompe di carica fino alla loro ottimizzazione. In seguito si è passati al sistema nel suo complesso, applicando anche dei transitori sui carichi e sui segnali di pilotaggio, in modo da rappresentare una possibile sequenza di eventi, alla quale potrebbe essere sottoposto il sistema durante il funzionamento reale. L’ottimizzazione delle due pompe di carica è stata mirata a mantenere più piccole possibili le dimensioni dei condensatori CP che, in questo modo, avrebbero rappresentato un minor ingombro sul chip e un carico più contenuto per gli inverter di pilotaggio, inoltre, è stato scelto il valore ottimale di capacità di carico per rendere stabile il circuito di controllo. Il circuito utilizzato per le simulazioni della singola pompa di carica è lo stesso rappresentato in Fig. 4.8, modificato solamente per aggiungere il numero di stadi necessari e inserire un generatore di corrente continua Iload che fungesse da carico. Gli andamenti analizzati sono stati: • andamento di Vout in funzione di Iload ; • analisi della stabilità del sistema di controllo in funzione della capacità CL . I grafici sono riportati in Fig. 5.5 e in Fig. 5.6 rispettivamente per la pompa di carica a 1.8 V e quella a 3.3 V. Ipotizzando un tempo di start-up di durata opportuna, inizialmente la corrente di carico è stata impostata a 0, in modo da far settare le pompe di carica al valore nominale. Una volta a regime, la Iload è stata fatta crescere con una pendenza regolare fino a portarsi al valore massimo richiesto da specifica. Si può notare come sotto i 30 µA il valore di tensione di uscita non cambi. Sopra i 30 µA il valore scende per arrivare a pieno carico a una caduta di tensione ∆V < 100 mV per entrambe le pompe di carica. Deve essere specificato che queste simulazioni rappresentano il caso peggiore, in cui cioè la tensione indotta sul tag è minima, mentre la corrente richiesta dal carico è massima. Avendo inserito in ingresso il circuito di protezione, per tensioni indotte superiori ad 1 V, le correnti erogabili dalla pompa sono di molto superiori. Per quanto riguarda la stabilità e il dimensionamento di CL , ci si è basati su simulazioni parametriche in cui si è fatto variare il valore della capacità di carico, mantenendo costanti i livelli di Iload e di Vind rispettivamente a 80 µA (o 150 µA) e 500 mV. Si è trovato che i valori delle capacità di uscita non possono essere inferiori a 3 nF, altrimenti, a pieno carico, l’anello di retroazione diventa completamente instabile. 49 Figura 5.5: Andamento di Vout (1.8 V) vs. Iload per la pompa di carica Figura 5.6: Andamento di Vout (3.3 V) vs. Iload per la pompa di carica 50 Transistor L[µm] P1 , P3 P2 , P4 MP # MN # 0.18 0.18 0.18 0.18 W[µm] 100 300 30 10 Tabella 5.2: Dimensioni dei transistor della pompa di carica Condensatore Capacità [pF] CP3.3 CP1.8 CL 10 30 3000 Tabella 5.3: Dimensioni delle capacità della pompa di carica Per generare il clock della pompa di carica è stata utilizzata la portante emessa dal reader, prelevata da un lato del rettificatore attraverso un piccolo condensatore che, caricatosi al valor medio del segnale prelevato, fornisce un segnale a 13.56 Mz sinusoidale che va da 0 alla tensione di picco massima indotta in ingresso. Inserito come ingresso agli inverter di pilotaggio, il segnale cosı̀ creato fa in modo che vengano generate le due fasi φ e φ. Le dimensioni ottenute per i vari componenti utilizzati sono riportate in Tab. 5.2 e Tab. 5.3. 5.3 Amplificatore operazione e regolatore di tensione LDO Le simulazioni sull’amplificatore operazionale sono state eseguite in un primo momento per analizzarne la banda e il guadagno, in seguito ne è stato valutato anche il consumo di potenza, per assicurarsi che non andasse ad influire in maniera eccessiva sul rendimento dell’intero sistema. I grafici qui riportati fanno riferimento all’amplificatore utilizzato dal regolatore LDO, polarizzato da una batteria a 3.3 V, avente un carico capacitivo di 1 pF e una corrente d’uscita nulla. Si può notare il taglio a −3 dB a circa 100 kHz, che garantisce una banda sufficientemente ampia per il controllo retroazionato, inoltre è da specificare il fatto che la struttura analizzata e della quale sono riportati i grafici, è stata successivamente modificata nel dimensionamento dello stadio d’uscita, una volta che l’amplificatore operazionale è stato inserito nella retroazione di una delle due pompe o del regolatore LDO. Per questo, parametri come il 51 80 60 Guadagno [dB] 40 20 0 −20 −40 −60 0 10 1 10 2 10 3 10 4 10 5 10 6 10 7 10 8 10 9 10 Frequenza [Hz] Figura 5.7: Banda/Guadagno dell’OP-AMP integrato margine di fase non sono stati analizzati specificatamente per gli amplificatori a sé stanti ma sono stati considerati all’interno del sistema e sono stati ritenuti ottimizzati automaticamente una volta stabilizzato l’alimentatore. I consumi dell’amplificatore operazionale sono abbastanza contenuti: sempre facendo riferimento alla struttura utilizzata nel regolatore LDO, si trova una corrente di perdita usata per la polarizzazione di 4.7 µA. Inoltre, dal punto di vista della stabilità del sistema, fondamentale è stato il dimensionamento dell’amplificatore in modo che la corrente in ogni ramo fosse proporzionata al carico in cui veniva specchiata: in questo modo infatti, si evita di inserire nel circuito un offset sistematico che rende l’anello di retroazione completamente instabile. Per quanto riguarda il regolatore LDO sono state prese in considerazione la sua stabilità rispetto alla capacità d’uscita e l’andamento della tensione Vout rispetto alla corrente di carico. Come riportato in Fig. 5.8, la tensione in uscita dal regolatore LDO risulta stabile a 1.8 V come richiesto da specifica per correnti di carico da 0 a 20 mA. La capacità di carico è stata dimensionata a 3 nF mentre la corrente utilizzata per la polarizzazione è di 6.8 µA. Come precedentemente specificato, per soddisfare alle differenti specifiche di progetto, lo stadio finale degli amplificatori operazionali utilizzati nei diversi controlli ha previsto differenti dimensionamenti: le dimensioni dei transistor nei vari casi sono riportate in Tab. 5.5. 52 Figura 5.8: Tensione di uscita del regolatore LDO vs. variazione della corrente di carico Transistor L[µm] M9 , M18 M10 M11 M13 , M14 M15 , M16 M0 0.18 1 1 1 1 0.18 W[µm] 0.28 20 60 600 10 400 Tabella 5.4: Dimensioni dei transistor dell’amplificatore operazionale e del regolatore LDO 53 Posizione circuitale LDO Pompa 1.8 V Pompa 3.3 V M12 [µm] M17 [µm] W/L=20/1 W/L=20/1 W/L=100/1 W/L=60/1 W/L=120/1 W/L=600/1 Tabella 5.5: Dimensioni dei transistor degli stadi finali degli amplificatori operazionali 5.4 Sistema completo Lo schematico del sistema completo è rappresentato in Fig. 5.9, in cui si notano: • lo stadio di ingresso composto dal raddrizzatore con le sue relative protezioni; • le due pompe di carica; • il multiplexer (MUX); • il segnale di pilotaggio Vpilot ; • la tensione Vbg in uscita dal riferimento di tensione Band-gap. La tensione Vpilot rappresenta la parte finale della logica digitale non considerata in questa tesi, mentre il blocco del multiplexer (MUX) e tutti gli altri interruttori utilizzati in questo progetto, sono stati presi da circuiti già progettati e perfettamente funzionanti, per questo i loro schemi elettrici e le loro specifiche non vengono riportate in questa tesi; tutti i dati sono comunque presenti nei riferimenti bibliografici citati [4]. La struttura è stata pensata in modo che le due pompe di carica possano fornire i valori di tensione di uscita richiesti da specifica, in modi e tempi indipendenti tra loro. Infatti, seppur rallentando leggermente il funzionamento del tag, separare i tempi di ricarica della batteria da quelli di trasmissione dati, permette di non sovraccaricare mai il rettificatore, che quindi riesce sempre ad erogare la quantità di corrente indispensabile al corretto funzionamento del sistema. I segnali di comando, utilizzati per settare l’alimentatore nelle condizioni di lavoro volute, vengono creati da un unico segnale proveniente dalla parte digitale del tag tramite una coppia di inverter. Le due fasi cosı̀ create, e indicate come ph+ e ph−, vanno a pilotare in maniera complementare le due pompe di carica accendendole o spegnendole a seconda della necessità. Il principio di funzionamento è molto semplice: durante la ricarica della batteria, il MUX, comandato da ph+ e ph−, fa in modo che solo la pompa 54 Figura 5.9: Sistema completo di carica a 3.3 V veda il clock in ingresso, mentre l’altra veda, in ingresso agli inverter di pilotaggio, un segnale nullo. Contemporaneamente l’amplificatore operazionale della pompa di carica non utilizzata viene messo in power-down, in modo da non creare un percorso da Vrect verso massa tramite il MOS d’uscita e quindi non sprecare potenza inutilmente. Durante la fase di trasmissione dati il funzionamento è esattamente lo stesso, con i valori dei segnali di pilotaggio scambiati in maniera duale. L’andamento ottenuto dalle simulazioni è riportato in Fig. 5.10, in cui viene azionata per prima la pompa a 3.3 V, facendola andare a regime in circa 60 µs e poi imponendole un carico di 80 µA. In un secondo momento viene fatto commutare il MUX in modo da spegnere la pompa di carica a 3.3 V e accendere la pompa a 1.8 V, che viene fatta settare in circa 30 µs e alla quale viene poi richiesta una corrente di carico di 150 µA. Si può notare come gli andamenti delle tensioni d’uscita siano praticamente uguali a quelli ottenuti dalle simulazioni delle pompe di carica effettuate singolarmente. Da sottolineare è l’importanza dei due inverter che, comandati da Vpilot , generano i segnali ph+ e ph−, tramite i quali viene azionato il controllo di power-down di entrambi gli amplificatori operazionali. Nel nostro caso infatti, il power-down è realizzato con due MOS che, se accesi, vanno a spengnere gli specchi di corrente e da un interruttore che, quando è aperto, blocca il flusso della corrente di pilotaggio dell’amplificatore. Per come è stato col- 55 Figura 5.10: Vout della pompa di carica con controllo digitale attivo 56 legato l’interruttore utilizzato nel progetto, il PMOS che lo compone ha il source collegato alla Vrect . Il pilotaggio tramite segnali digitali, va bene solo quando la tensione rettificata non supera 1.8 V. Per valori superiori, il source risulterebbe ad una tensione più positiva del gate non permettendo il corretto spegnimento del PMOS e quindi introducendo un leakage costante, che andrebbe a peggiorare di molto il funzionamento della pompa di carica. Pilotando questo interruttore tramite degli inverter collegati tra Vrect e massa, invece, il livello alto sul gate del PMOS è proprio pari alla tensione di source e perciò il leakage è ridotto al minimo. 57 Capitolo 6 Conclusioni Il lavoro descritto in questa tesi prevedeva la progettazione del sistema di alimentazione per un chip RFID a 13.56 MHz, composto da: un’antenna di ricezione, un raddrizzatore, una pompa di carica e un sistema di regolazione per la tensione di uscita. Data la natura del sistema parzialmente passiva, per tutta la progettazione, sono stati considerati di primaria importanza i consumi, anche se non vi era un preciso parametro elencato tra le specifiche di progetto. Per quanto riguarda l’antenna, ci si è limitati ad adottare le misure imposte da normativa e a calcolare il suo valore di induttanza da inserire nel modello circuitale. Per il raddrizzatore, ci si è basati su di una struttura a ponte a doppia semionda con gate incrociati realizzata in tecnologia CMOS, grazie alla quale si è riusciti ad ottenere una bassa resistenza di uscita, una alta efficienza di conversione e una bassa tensione di soglia del sistema completo. La pompa di carica utilizza anch’essa la tecnologia CMOS e prevede una struttura a latch impilati pilotati da inverter. In questo caso si è visto dalle simulazioni come una sola pompa di carica non sarebbe bastata, perciò è stata realizzata una struttura con due pompe di carica indipendenti, gestite da una logica di controllo non trattata in questa sede. Realizzato tramite un amplificatore operazionale posto in retroazione negativa all’uscita, il sistema di regolazione della tensione è compreso nel blocco circuitale della pompa di carica. Per la progettazione di quest’ultimo ci si è incentrati sulla stabilità del sistema e sulla massima corrente erogabile dallo stadio d’uscita dell’amplificatore operazionale: da esso infatti dipende il corretto pilotaggio delle due pompe di carica. Tutte le specifiche sono state rispettate correttamente e, data la tecnologia adottata, si è cercato di ottimizzare il circuito nel miglior modo possibile. In questo senso si è trovata come minima tensione indotta per l’accensione del sistema una Vind = 400 mV, mentre, per il funzionamento vero e proprio richiesto da specifica, sono state ottenute due possibili situazioni: 58 • Vout = 3.3 V @ ILmax < 100 µA, con una Vind di almeno 500 mV; • Vout = 1.8 V @ ILmax > 150 µA, con una Vind di almeno 500 mV. Come completamento di tutto il sistema è stato inserito anche un regolatore di tensione Low Drop-Out, che, servendosi della batteria, fornisce l’alimentazione a tutto il circuito nelle situazioni più critiche. Tutte le simulazioni sono state eseguite tramite il software CADENCE. 59 Bibliografia [1] K. Finkenzeller, RFID Handbook: Fundamentals and Applications in Contactless Smart Cards and Identification, Second Edition, Wiley, 1994. [2] Z. Zhu, B. Jamali and P. H. Cole, Brief Comparison of Different rectifier structures for HF and UHF RFID, University of Adelaide, http://www.m-lab.ch/auto-id/SwissReWorkshop/papers/. [3] L. Pylarinos, Charge Pumps: An Overview, University of Toronto, http://www.eecg.toronto.edu/ kphang/ece1371/chargepumps.pdf. [4] F. Conso, Progettazione di un Circuito di Interfaccia Misto AnalogicoDigitale per Sensori Capacitivi di Umidità a Basso Consumo di Potenza, Tesi di Laurea Specialistica, Università degli studi di Pavia, 2007. [5] A. Facen, Design of a Low-Cost Passive UHF RFID Tag in 0.18µm CMOS Technology, Ph. D. Thesis, Università degli Studi di Parma, 2008. [6] ISO 15693, Identification Cards – Contactless Integrated Circuit(s) Cards – Vicinity Integrated Circuit(s) Card. [7] ISO 7810, Identification Cards – Physical Characteristics. [8] S. S. Mohan, Simple Accurate Expressions for Planar Spiral Inductors, IEEE Journal of Solid State Circuits, vol. 44, pp. 1419–1424, Oct. 1999. [9] A. Sedra and K. Smith, Circuiti per la Microelettronica, Ingegneria 2000, 1994. [10] F. Maloberti, Analog design for CMOS VLSI systems, Kluwer Academic Publishers, 2001. [11] R. J. Milliken and J. Silva-Martı́nez. Full On-Chip CMOS Low-Dropout Voltage Regulator, IEEE Transaction on Circuits and Systems I, vol. 54, pp. 1879–1890, Sept. 2007. 60