Ottimizzazione Openssl su Itanium 2/OpenVMS

Riccardo Giacomelli

8 febbraio 2005

2

Indice

I

Architettura Itanium 2

0.1

0.2

0.3

II

7

Introduzione Itanium 2 processore RISC

0.1.1 EPIC . . . . . . . . . . . . . . .

Architettura generale . . . . . . . . . . .

0.2.1 Execution model . . . . . . . . .

0.2.2 Unitá funzionali e issue rules . .

0.2.3 Bundles e Dipersal Rules . . . .

0.2.4 Pipeline . . . . . . . . . . . . . .

0.2.5 Memory Hierarchy . . . . . . . .

Meccanismi innovativi di Itanium . . . .

0.3.1 Registri . . . . . . . . . . . . . .

0.3.2 Register Stack . . . . . . . . . .

0.3.3 Software pipeline . . . . . . . . .

0.3.4 Speculation and Predication . . .

o

.

.

.

.

.

.

.

.

.

.

.

.

CISC?

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Assembler Itanium

9

9

10

11

11

12

15

15

15

15

16

18

18

21

1 Descrizione dell’assembler

1.1 Formato delle istruzioni

1.2 Registri . . . . . . . . .

1.3 Procedure . . . . . . . .

1.4 Explicit Bundle . . . . .

Itanium

. . . . . .

. . . . . .

. . . . . .

. . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

23

23

23

24

24

2 istruzioni principali

2.1 Add . . . . . . .

2.2 Alloc . . . . . . .

2.3 And . . . . . . .

2.4 Cmp-Cmp4 . . .

2.5 Dep . . . . . . .

2.6 Extr . . . . . . .

2.7 Ld . . . . . . . .

2.8 Nop . . . . . . .

2.9 Mix-Mux . . . .

2.10 Shl . . . . . . . .

2.11 Shr . . . . . . . .

2.12 Shrp . . . . . . .

2.13 Xor . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

27

27

27

28

28

28

28

29

29

29

30

30

30

31

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

3

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

4

INDICE

III

Ottimizzazione degli Algortimi

33

2.14 Introduzione . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

35

3 Linee generali

3.1 Ottimizzazione generale del codice . . . . . . . .

3.1.1 Load-Store . . . . . . . . . . . . . . . . .

3.1.2 Cicli e loop unrolling . . . . . . . . . . . .

3.2 Ottimizzazione dell’assembler . . . . . . . . . . .

3.3 Fasi di Ottimizzazione degli Algoritmi . . . . . .

3.4 Operazioni presenti in tutti gli algoritmi . . . . .

3.4.1 Uso di Costanti . . . . . . . . . . . . . . .

3.4.2 Selezione di bits da registro . . . . . . . .

3.4.3 Look up in tabella . . . . . . . . . . . . .

3.4.4 Uso delle load . . . . . . . . . . . . . . . .

3.4.5 Xor tra una serie di valori . . . . . . . . .

3.4.6 Htonl Ntohl . . . . . . . . . . . . . . . . .

3.4.7 Uso dei bundles per le istrzioni assembler

3.5 Regole Generali per Itanium . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

37

37

37

38

39

39

40

40

40

41

41

42

42

43

44

4 DES

4.1 Caratteristiche Principali . . . . . . . . . . . .

4.1.1 Permutazioni . . . . . . . . . . . . . . .

4.1.2 32 bit-64 bit . . . . . . . . . . . . . . .

4.1.3 Table look-up . . . . . . . . . . . . . . .

4.2 Ottimzzazione DES in Dettaglio . . . . . . . .

4.2.1 Initial Permutation e Final Permutation

4.2.2 16 Rounds . . . . . . . . . . . . . . . . .

4.2.3 Ottimizzazione in Itanium . . . . . . . .

4.3 Risultati . . . . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

45

45

45

46

47

48

48

50

51

51

5 RC5-32/12/16

5.1 Caratteristiche Principali . . . . . . . . .

5.1.1 Rotate variabili . . . . . . . . . . .

5.1.2 Add modulo 232 . . . . . . . . . .

5.2 Ottimzzazione RC5-32/12/16 in Dettaglio

5.2.1 RC5-32/12/16 single round . . . .

5.2.2 Ottimizzazioni in Itannium . . . .

5.3 Risultati . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

53

53

53

53

54

54

55

56

6 SHA-1

6.1 Caratteristiche Principali . . . . . . . . .

6.2 Descrizione dell’algoritmo e ottimizzazione

6.2.1 Descrizione dei round . . . . . . .

6.2.2 Espansione delle word . . . . . . .

6.3 Ottimizzazione SHA-1 nel dettaglio . . . .

6.3.1 Singolo Round . . . . . . . . . . .

6.3.2 Espansione delle word . . . . . . .

6.3.3 Ottimizzazione in Itanium . . . . .

6.4 Risultati . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

57

57

58

58

58

59

59

59

59

60

INDICE

5

7 AES (Rijndael)

7.1 Caratteristiche Principali . . . . . .

7.1.1 Scelta dell’implementazione .

7.2 Ottimizzazione AES nel dettaglio . .

7.2.1 Ottimizzazione dell’algoritmo

7.3 Ottimizzazione In Itanium . . . . . .

7.4 Risultati . . . . . . . . . . . . . . . .

IV

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Appendix

65

65

65

66

69

70

71

73

8 Help Itanium/OpenVMS

8.1 Assembler Itanium . . .

8.2 Compilare il codice . . .

8.3 Linking . . . . . . . . .

8.4 Debugger . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

75

75

75

76

76

9 Summary

9.1 DES . . . . . . . . .

9.1.1 DES Results

9.2 RC5-32/12/16 . . . .

9.3 AES . . . . . . . . .

9.4 SHA-1 . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

79

79

79

80

80

82

.

.

.

.

.

.

.

.

.

.

6

INDICE

Parte I

Architettura Itanium 2

7

0.1. INTRODUZIONE ITANIUM 2 PROCESSORE RISC O CISC?

0.1

9

Introduzione Itanium 2 processore RISC o

CISC?

In Internet, in molti articoli riguardanti Itanium, questo processore viene definito a volte un RISC a volte un CISC; entrambe le definizioni hanno un qualcosa

di vero. Si definiscono RISC, ovvero Reduct Set of Istruction Computing quei

processori che possiedono un ridotto set di istruzioni assembler e non hanno

nel loro set istruzioni complicate, come ad esempio le operazioni sulle stringhe dell’8086. L’idea su cui si basano i processori RISC é quella di risolvere i

problemi complicati e lunghi, invece che con una sola istruzione, in piú passi,

suddividendo l’operazione complessa in una serie di piú istruzioni semplici. Disponendo solo di istruzioni semplici, i RISC sono in grado di eseguire molte piú

istruzioni al secondo rispetto ai CISC. I processori CISC sono quelli che hanno

implementate un vasto numero di istruzioni e dispongono di istruzioni complicate quali, ad esempio, l’istruzione di rotate di un registro o le operazioni su

stringhe. Il processore Itanium sicuramente un processore RISC perché dispone

di operazioni semplici che durano un colpo di clock. Un esempio concreto é dato

dal fatto che l’operazione add esiste solo con operandi contenuti in registri , e

quindi per fare add di un operando in memoria bisogna prima caricarlo in registro con una operazione di load. Oppure, altro esempio, non ha supporto per

rotate variabile di registro. Allo stesso tempo possiede anche istruzioni complicate: prendiamo ad esempio la extr che permette di selezionare un sottoinsieme

di bit da un registro, operazione che di solito era fatta con shift + and con

maschera. Basti pensare che su Itanium 2 sono implemetate oltre 150 istruzioni, ognuna della quali ha delle varianti. Per quanto riguarda la compatibilitá

con le versioni assembler precedenti si adottano delle soluzioni quali l’utilizzo

di pipeline separate per eseguire codice in assembler non Itanium. Oppure si

adotta una memoria di microcodice in cui per ogni istruzione complicata c’é la

serie di istruzioni semplici corrispondente. Quando si deve eseguire una istruzione complessa si effettua un jump nella memoria di microcodice e si eseguono

le istruzioni semplici corrispondenti. Concludendo, nella sua struttura Itanium

un processore RISC superscalare in quanto riesce a compiere ben 6 istruzioni

per colpo di clock, ma avendo al tempo stesso anche caratteristiche CISC. In

realtá Itanium va oltre i processori RISC e CISC. Il termine esatto per definire

l’architettura Itanium EPIC.

0.1.1

EPIC

Una caratteristica di Itanium che il processore esegue le operazioni nell’ordine in cui gli vengono fornite dal compilatore. Non ha nessun meccanismo di

riordino delle istruzioni, non ha alcun meccanismo di ottimizzazione del codice

al momento dell’esecuzione. In processori come il Pentium esisteva un pool di

istruzioni di cui il processore aveva eseguito il fetch; poteva poi decidere di farne

avanzare alcune mentre altre erano in stallo, oppure era in grado di cambiare

l’ordine di esecuzione delle istruzioni. Questo meccanismo, se da un lato era

utile per cercare di eseguire in modo piú veloce possibile il codice, dall’altro

presupponeva l’esistenza di una serie di processi per controllare che l’esecuzione del codice fosse ancora corretta, verificava che tutte le dipendenze fossero

state rispettate ecc. L’architettura risultante diventava molto complicata. In

10

Itanium, invece, la strategia é cambiata: il processore esegue in ordine tutte

le istruzioni senza cercare di modificarne la sequenza. A questo punto é chiara limportanza fondamentale del compilatore, poiché il codice compilato verrá

eseguito cosı́ com’é stato compilato. La scelta di Itanium é quella di dare pieno

controllo del processore al programmatore. Le istruzioni sono molto accurate,

permettono addirittura di controllare la cache. Tuttavia, proprio per il fatto

che si ha pieno controllo sul processore e le istruzioni sono ricche di dettagli,

la programmazione in assembler Itanium e la realizzazione di compilatori per

Itanium risultano complicate. EPIC significa Explicit Parallel Instruction Computing. Questo paradigma ha portato a una rivoluzione, ovvero a seguire una

linea di progetto che lascia solo le procedure semplici ed essenziali nel core, mentre quelle piú complicate vengono demandate ad altri, ovvero al compilatore. Il

compilatore prepara il codice, mentre il processore, con un’espressione trovata

sul sito Intel, will rock it, ovvero lo eseguirá molto velocemente. Al tempo stesso

in Itanium sono implementati nuovi meccanismi che complicano l’architettura .

Essi saranno presentati nella sezione seguente.

0.2

Architettura generale

La grande capacitá di eseguire istruzioni permette a Itanium di sfruttare al

massimo il parallelismo esistente nel codice, a condizione che venga scritto e

compilato in modo adeguato. (Piú avanti verrá spiegato meglio come). Le

caratteristiche piú importanti di Itanium sono:

1. Architettura interamente a 64 bit

2. Vasto set di istruzioni

3. Gran numero di registri

4. Struttura di accesso alla memoria ottimizzata

5. gran numero di unitfunzionali in grado di eseguire 6 istruzioni per clock

6. Register Stack-meccanismi innovativi per gestire i registri e i passaggi di

parametri a funzione

7. Software pipeline-meccanismi innovativi per gestire i loop

8. Cache instructions-istruzioni per controllare direttamente la cache

9. Speculation and Predication-meccanismi di speculazione e predicati innovativi

Itanium dispone di un’architettura interamente a 64 bit; sia i registri che i bus

che la pipeline e le unitá funzionali hanno tutte parallelismo 64 bit. La vera

innovazione consiste nell’avere le unitá funzionali e i registri a 64 bit, perché

giá altri processori come il pentium disponevano di un bus a 64 bit per migliorare il bandwidth verso l’esterno del processore, ma non disponevano di unitá

funzionali a 64 bit.

0.2. ARCHITETTURA GENERALE

0.2.1

11

Execution model

Itanium puó eseguire fino a 6 istruzioni per colpo di clock. Il processore esegue

le istruzioni tre a tre. Un gruppo di istruzioni viene denominato Bundle. Il

processore esegue quindi due Bundle per colpo di clock. Quando il processore

riesce ad eseguire 2 Boundle in un colpo di clock si verifica una situazione di

dual issue, ma non sempre riesce ad eseguirne due. In questo caso c’é uno

split issue, ovvero i due bundle vengono eseguiti in 2 colpi di clock successivi.

In definitiva il processore esegue o 3 o 6 istruzioni per clock. Questo importante

perché se anche solo una delle 3 istruzioni nel secondo Bundle non puó essere

eseguita per uno dei motivi citati dopo, tutte e tre le istruzioni verranno eseguite

al clock successivo. I motivi per cui ci puó essere uno split issue sono:

1. uno stop esplicito é stato incontrato. Lo stop é rappresentato con ;;

2. non ci sono abbastanza risorse per eseguire tutte le istruzioni

3. Le istruzioni non sono state poste nel Bundle seguendo le regole di dispersal Itanium

Le regole di dispersal definiscono in che modo le istruzioni debbano essere posizionate nel bundle. Esse saranno spiegate nelle subsection successive. Ritornando a processori come il Pentium, questi avevano un’architettura piú complicata

anche perché dovevano occuparsi di controllare i cosidetti hazards, ovvero le situazioni in cui un registro é scritto con un nuovo valore prima che il precedente

valore potesse essere letto (WAR-Write after read). Oppure il registro viene

letto prima che il valore da leggere sia stato scritto (RAW-Read after write).

Un esempio su tutti é dato dall’istruzione che legge un registro pensando di

trovare il risultato di un’istruzione precedente, ma la precedente non era ancora

terminata. Oppure, altro esempio, dato da hazards (WAW-write after write),

cioé quando esistono 2 scritture consecutive sullo stesso registro. Come é stato

risolto in Itanium tutto questo? In veritá Itanium non se occupa minimamente: sará il compilatore ad inserire tra le due istruzioni in questione uno stop

implicito in modo da rispettare la dipendenza. Se il compilatore non inserisce

nessuno stop e si verificano degli hazard il processore, come letteralmente scritto

nei manuali intel, si comporterá in modo non deterministico e il risultato non

sará prevedibile.

0.2.2

Unitá funzionali e issue rules

Itanium 2 dispone di 6 unitá ALU. Queste vengono usate per eseguire le operazioni aritmetiche, compares, multimedia istruction ecc. Dispone di 4 porte

verso la cache per l’accesso alla memoria, due per le store, e due per le load.

Questo permette di eseguire 2 load e 2 store per colpo di clock. Possiede 2

unitá Integer(I0, I1), e una unitá shift per operazioni quali lo shift right,shift

left, ecc. In totale ha 11 porte a cui le istruzioni vengono mandate per essere

eseguite:M0, M1, M2, M3, I0, I1, F0, F1, B0, B1 e B2. Le M0-M3 sono le

porte per la memoria, ma non sono tutte uguali: M0 e M1 sono le porte per le

load, M2 e M3 sono le porte per le store. Inoltre le porte M non vengono solo

usate per gli accessi in memoria, ma anche per eseguire operazioni di tipo ALU

tipo add, and ecc. Lidea é che poiché le porte di memoria dovevano contenere

un’unitá per calcolare l’indirizzo e quindi in grado di svolgere calcoli, quando

12

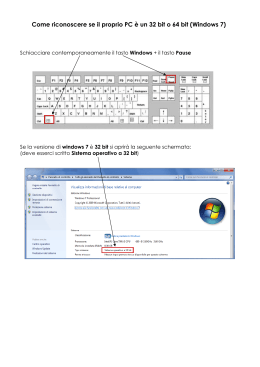

Instruction Type

A1-A5

A6-A8

A

I

I5

I7

I10

I11, I12

I29

M1

M4, M5

M34

Istrutions

add, shladd

cmp, cmp4

and

xor, or

shr, shr. u

shl, shl. u

shrp

extr, extr. u, Dep

sxt, zxt, czx

ld4, ld8. .

st4st8. .

alloc

Description

add, parallel add

compare e compare 4 bytes

and logico

xor, or logico

shift right

shift left

shift right pair usato per rotate fissi

extract, Deposit

signe extended, zero extended

Integer load

Integer store

allocate frame on reg stack

M0

Y

Y

Y

Y

M1

Y

Y

Y

Y

Y

Y

M2

Y

Y

Y

Y

Y

Y

Tabella 1: principali istruzioni e porte sulle quali possono essere eseguite

queste porte non venivano usate per l’accesso in memoria potevano essere usate

per eseguire altre istruzioni. Di conseguenza, nelle porte M sono state inserite

delle vere e proprie ALU in grado di calcolare gli indirizzi di memoria quando

necessario, ma anche di eseguire operazioni aritmetiche all’occorrenza. Le porte I0 e I1 sono le porte Integer; esse eseguono operazioni quali gli shift o gli

xor, oppure istruzioni complicate quali la mix o l’extr. Un limite di Itanium é

costituito proprio da queste 2 porte. Nell’ottimizzazione degli algoritmi la maggior parte delle istruzioni era di tipo integer; Itanium, pur avendo tutte queste

unitá funzionali, puó eseguire solo 2 istruzioni Integer per colpo di clok, e per le

istruzioni piú complicate come l’extr anche solo una per clock. Le porte F0, F1

sono le Floating point, Le porte B0, B1, B2 sono le porte in cui sono eseguite le

operazioni di branch. La tabella 1 riporta le principali istruzioni e le porte su

cui possono essere eseguite. Il type delle istruzioni definisce se sono istruzioni di

tipo ALU, Integer o Memory. All’interno di questi gruppi vi sono sottoinsiemi,

per esempio A2, A4, ma le sottodivisioni non sono importanti. Quello che é importante é sapere quali istruzioni appartengono a quale gruppo, e da che unitá

funzionale possono essere eseguite. Come si vede dalla tabella 1 le istruzioni

ALU possono essere eseguite da qualunque unitá M o I, le istruzioni Integer,

sono piú limitate, per esempio la extr puó essere solo eseguita dell’unitá I0.

0.2.3

Bundles e Dipersal Rules

Le Dipersal Rules sono le regole che il processore usa per eseguire le istruzioni.

Sono molto importanti perché se non vengono rispettate, si avrá uno split

issue. Come abbiamo detto prima le istruzioni sono raggruppate in bundles

ognuno di tre istruzioni. Ciascuna delle tre posizioni all’interno del bundle é

chiamata slot. Ogni bundle ha 3 slot. La posizione in cui un’istruzione é posta

determina l’unitá funzionale da cui sará eseguita. c’é un mappaggio preciso

tra la posizione delle istruzioni e l’unitá funzionale a cui sará anno assegnate.

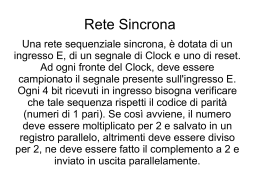

Questo mappaggio é chiamato dipersal. Essistono molti tipi di Bundles, per

esempio MMI, MMF, MII. Le lettere M stanno sempre per memory, A ALU, I

Integer, F floating point, B branch. Un Bundle del tipo MMI significa che ha

2 istruzioni memory e una integer. L’ordine in cui sono specificate le istruzioni

M3

Y

Y

Y

Y

Y

I0

Y

Y

Y

Y

Y

Y

Y

Y

Y

I1

Y

Y

Y

Y

Y

Y

Y

0.2. ARCHITETTURA GENERALE

MII

MLI

MMI

MFI

MMF

MIB

MBB

BBB

MMB

MFB

MMI

Y

Y

Y

Y

Y

Y

MLI

Y

Y

13

Y

Y

Y

Y

Y

MMI

Y

Y

Y

Y

Y

Y

MFI

Y

Y

Y

Y

Y

Y

MMF

Y

Y

Y

Y

Y

Y

MIB

Y

Y

Y

Y

Y

Y

MBB

Y

Y

Y

Y

Y

Y

BBB

Y

Y

Y

Y

Y

Y

MMB

Y

Y

Y

Y

Y

Y

MFB

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

Tabella 2: tipi di Bundle che possono andare in dual issue

non é casuale ma preciso: prima devono essere scritte le 2 istruzioni memory, poi

l’istruzione integer. Scrivendo il codice assembler i Bundle vengono dichiarati

con 2 parentesi graffe e il tipo del bundle scritto all’inizio. Per esempio:

{. mmi

ld4 r32=[r32]

ld4[ r33=[r33]

shr r35=r35, 2

}

Un Bundle di questo tipo é un memory-memory-integer; si puó notare che l’istruzione integer occupa proprio il terzo slot nel bundle. Le dispersal rules sono

molte. Le principali per le operazioni ALU e Integer sono:

• l’istruzione nel primo slot I dei due Bundles sará eseguita da I0, La seconda

da I1.

• Se la seconda istruzione I puó essere eseguita solo da I0 ci sará uno stop

implicito e l’istruzione sará eseguita nel colpo di clock seguente

• Gli slot I non contengono solo istruzioni I ma possono contenere anche

istruzioni di tipo ALU. Se 2 istruzioni di tipo I sono giá state assegnate

alle due unitá funzionali I0 e I1, e un ulteriore slot I contiene unistruzione

ALU, questa verrassegnata ad una unitá M libera. E’ il caso dei Bundles

MMI-MMI.

Un esempio della prima regola questo:

{. mmi

ld4 r32=[r32]

ld4[ r33=[r33]

shr r35=r35, 2

}

{. mmi

ld4 r32=[r32]

ld4[ r33=[r33]

xor r35=r35, 2

};;

14

Come detto nella regola citata prima, l’istruzione shr che é la prima istruzione Integer verrá assegnata all’unitá I0, l’istruzione xor che la seconda istruzione

Integer verrá assegnata a I1. E’ importante capire che, se nei 2 bundle c’é un’istruzione tipo extr eseguibile solo da I0, questa deve essere posta nel primo slot

I, altrimenti si avrá uno split issue. esempio:

{. mmi

ld4 r32=[r32]

ld4[ r33=[r33]

shr r35=r35, 2

}

{. mmi

ld4 r32=[r32]

ld4[ r33=[r33]

extr r35=r35, 2

};;

In questo esempio lo slot I0 occupato dall’istruzione shr; l’istruzione integer

successiva cioé extr non puó essere eseguita, e c’é un split issue. Se il codice

fosse scritto nel modo seguente:

{. mmi

ld4 r32=[r32]

ld4[ r33=[r33]

extr r35=r35, 2

}

{. mmi

ld4 r32=[r32]

ld4[ r33=[r33]

shr r35=r35, 2

};;

sarebbero eseguite tutte e sei le istruzioni in un colpo di clock. La terza regola

diceva che se in uno slot integer c’é un’istruzione ALU, e le 2 unitá I0 e I1 sono

gioccupate l’istruzione assegnata ad una unitá M. esempio:

{. mii

ld4 r32=[r32]

extr r35=r35, 2

shr r35=r35, 2

}

{. mmi

ld4 r32=[r32]

st4 [r40]=r40

and r50=r50. r51

};;

le due istruzioni integer shr e extr sono assegnate alle unitá integer. Lo slot

integer del secondo bundle non puó essere assegnato ad una unitá integer, ma

siccome contiene una istruzione ALU verrá assegnata ad una unitá M. La tabella

2 indica quali tipi di bundle possono essere eseguiti insieme in un solo colpo di

clock. Non é sufficiente seguire la tebella 2 affinché si abbia dual issue, poiché

0.3. MECCANISMI INNOVATIVI DI ITANIUM

15

é sempre necessario seguire le regole di dispersal. Se non vengono rispettate ci

sará split issue anche se si sono usati 2 bundle che nella tabella 2 sembravano

poter essere eseguiti in dual issue. Per approfondimenti sulle altre regole di

dispersal consultare [1, capitolo 1.1] La regola generale quella di porre prima

nel bundle le istruzioni con piú limitazioni.

0.2.4

Pipeline

La pipeline Itanium 2 é molto lunga, ha 8 stage. Una pipeline lunga serve

soprattutto per migliorare il throughput di istruzioni per colpo di clock. Le

varie stage della pipeline non sono state approfondite perché non sono essenziali

per la comprensione dell’ottimizzazione su Itanium.

0.2.5

Memory Hierarchy

Il processore Itanium ha una cache L1-D di primo livello per i dati, una cache

L1-I per le istruzioni, una cache L2 di secondo livello unificata e una cache di

terzo livello. Il TLB(Translation lookaside buffer) per convertire gli indirizza

da cercare full associative, non verrá approfondito qui. La cosa piú importante

sono le dimensioni e le latenze della cache. La cache L1 ha dimensione 16Kbytes,

set associative a 4 vie, e una linea di cahe lunga 32 byte. La cache L2 ha

dimensione 96Kbytes, 6 way set associative e una linea di 64 bytes. La cache L3

sul processore esaminato ha dimensione 3 Mbytes. La latenza di primo livello

lavora alla velocitá del processore; per accedervi basta un colpo di clock, quindi

la latenza per accedere alla cache L1 é un colpo di clock. Per accedere alla cache

L2 la latenza di 6 colpi di clock per gli interi 9 per i floating point. La latenza

per L3 di 21 colpi di clock per gli interi e 24 per i floating point. Se c’é un

miss in L1 si controllerin L2 e se c’é ancora miss si controllerá in L3, quindi le

latenze per accedere a L3 vanno sommate. Il bus esterno dalla cache L3 alla

memoria ha una bandwidth di 2.1 Gb/secondo. Tra L3 e L2, invece, si possono

trasmettere 16 bytes/clock. Tra L2 e L1 si possono trasmettere 32 bytes/clock,

e tra L1 ed il register file si possono caricare 2 x 8 bytes/clock. Il processore

dispone di 4 porte (2 per le load e 2 per le store), quindi possono essere eseguite

al massimo 2 load di 8 bytes ciascuna e 2 store di 8 bytes ciascuna.

0.3

0.3.1

Meccanismi innovativi di Itanium

Registri

Itanium dispone di un ricco set di registri: i registri utilizzabili sono molti, come

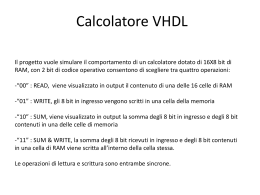

si vede dalla figura 1. Gli Integer registers sono registri general purpose a 64 bit

e vengono utilizzati comunemente per contenere dati, indirizzi ecc. I Predicate

registers sono usati per i predicati che sono un meccanismo per velocizzare le

condizioni presenti nel codice, tipo if-else. I Branch Registers sono registri per

contenere gli indirizzi dei salti e vengono usati per velocizzare i salti presenti

nel codice. In realtá vi é un’ulteriore suddivisione nei registri General purpose

R1-R128:

• R0:sempre uguale a zero

• R1:GP(Global Data Pointer)

16

128

Integer Registers

128

Floating Point Registers

Instruction Pointer

64

Predicate Registers

User Mask

8

Branch Registers

128

Application Registers

CPUID Registers

Current Frame Pointer

Performance Monitor

Data Registers

Figura 1: set di registri itanium

• R2-R3:scratch

• R4-R7:riservati

• R8-R11:valori di ritorno delle procedure

• R12:stack pointer

• R13:(Riservato)Thread Pointer

• R14-R31:scratch

• R32-R128:General registers

Gli scratch registers sono quelli usati per scopi general purpose, quando una

procedura usa pochi registri vengono usati questi registri. Il registro R0 sempre uguale a zero é uno stratagemma, usato anche in altri processori, per poter

ottenere l’indirizzamento assoluto semplicemente usando l’indirizzamento base+displacement e usando come base R0. Cosı́ implementando pochi modi di

indirizzamento, se ne possono ottenere altri derivati da questi. I registri R32R128 sono general purpose e possono essere usati dalle procedure che usano piú

di 2 o 3 registri e che quindi non hanno abbastanza registri di scratch.

0.3.2

Register Stack

Dato il gran numero di registri era necessario un meccanismo per gestirli al

meglio, perché non tutte le procedure usano i registri da R32 a R128, ed era

0.3. MECCANISMI INNOVATIVI DI ITANIUM

Registri R32

Proc A

R40

Local

R50

R55

R60

R68

Output

Proc B

Input

Local

Proc C

Output

Input

Proc B

Proc A

17

Input

Local

Local

Local

Output

Output

Figura 2: chiamate a procedura

necessario permettere alla funzione di usufruire solo dei registri necessari. In

altri processori la procedura standard prevedeva che o il chiamante o il chiamato (caller o calle) salvassero il valore dei registri nello stack per permettere

alla funzione di usarli. Con tutti questi registri diventava un pó complicato

e inefficiente questo metodo di procedere. In Itanium si usa un altro metodo

chiamato Regiter Stack I registri da R32 a R128 vengono usati come uno stack.

Ogni funzione ha a disposizione 3 tipiú di registri:

• Input registers

• Local registers

• output registers

Gli input sono i registri usati per i parametri in ingresso, i Local sono quelli

usati internamente dalla funzione. I registri di output non sono quelli usati per

i valori di ritorno come potrebbe sembrare dal nome, ma sono quelli usati dalla

funzione per passare parametri ad altre sottofunzioni. Si ricorda che i registri

per passare i valori di ritorno sono R8-R11. I registri di output del chiamante

coincidono con i registri di input del chiamato. Bisogna considerare i registri

R32-R128 come uno stack ogni funzione alloca sullo stack il numero di registri

che gli occorrono. input, local e output sono solo denominazioni diverse per i

registri general purpose e, una volta compilato il codice, vengono mappati sui

registr r32-r128. Essi servono per facilitare la scrittura del codice. esempio: In

figure 1.2 si puó vedere come cambia lo stack regisers con 3 procedure A, B,

C che vengono chiamate una dentro l’altra. All’inizio lo stack registers punta

al registro R32, la procedura A alloca sullo stack register 8 registri Local, cioé

da usare internamente, e 10 registri output per passare i parametri di input

18

ala procedura B. Quando la procedura B viene chiamata, essa consapevole di

dover ricevere in input 8 parametri e alloca sullo stack registers 8 registri di

input piú 5 registri che userá internamente, e altri 5 registri per poter passare

i parametri di input alla procedura C. Si puó notare come i registri di output

di A e quelli di input di B coincidano; questo permette di passare i parametri

da una funzione all’altra. C, a sua volta, alloca 5 registri di input e 8 registri

local. Come si puó notare C non usa registri di output perché non deve chiamare

sotto di sé nessun’altra procedura. All’istruzione di return di una funzione il

puntatore dello stack registers torna indietro alla funzione precedente. In questo

modo si elimina la necessitá di salvare i registri che la funzione userá perché

necessario solamente che la funzione allochi con l’istruzione ALLOC dei registri

sullo stack. Una domanda che sorge spontanea é : se dopo chiamate a procedura

successive magari ricorsive si allocato un numero di registri che vá oltro R128

cosa succede? Itanium se si arriva fino a R128 e sono necessari altri registri

usa un meccanismo per salvare i registri e liberare spazio sullo stack dei registri

per la funzione successiva. Questa operazione abbastanza costosa in termini di

colpi di clock puó durare anche 20 colpi di clock e deve essere quindi evitata

accuratamente se le prestazioni sono essenziali. D’altronde il numero di registri

é tale da far sı́ che il processore non debba mai salvare i registri per liberare

spazio sullo stack.

0.3.3

Software pipeline

I meccanismi di software pipeline non sono stati da me approfonditi piú di

tanto perché non li ho utilizzati; daró comunque un’idea generale del loro funzionamento perché in alcuni casi, sono meccanismi molto utili e innovativi. Il

software pipeline é applicato quando nel software ci sono dei blocchi di codice

uguale ripetuti piú volte, come nel caso dell’algoritmo DES in cui ci sono 16

round. L’idea del software pipeline é quella di usare una pipeline applicata al

software. Per esempio nel caso del DES ogni round dovrá svolgere delle operazioni specifiche: Espansione E, trasformazione tramite S-boxes, ecc. L’idea

é quella di mettere i vari round in pipeline, cioé mentre il primo round sta

eseguendo la sua seconda operazione, il secondo esegue la prima e cosı́ via. Tuttavia nel caso di algoritmi crittografici ogni round dipende dal precedente, di

conseguenza il secondo round non puó iniziare prima della fine del primo. Per

questo motivo questi meccanismi non sono stati utilizzati nell’ottimizzazione.

La pipeline viene attuata grazie al register stack, il meccanismo descritto sopra.

Si usano dei registri virtuali. Ogni ciclo usa un determinato numero di registri

( ad esempio il primo utilizza i registri dall’R32 al R41, dall’R42 all’R51 ecc).

Per esempio per il ciclo uno il virtual register 1 corrisponde al registro R32, per

il ciclo 2 il virtual register 2 corrisponde al registro R42. Potendo usare diversi

registri i cicli possono essere eseguiti insieme.

0.3.4

Speculation and Predication

Prediction

Il meccanismo di Prediction serve per ottimizzare le condizioni tipo if-else presenti nel codice. Quando nel codice si trovano delle condizioni, queste vengono

predette dalla branch prediction unitá con meccanismi complessi illustrati dopo,

0.3. MECCANISMI INNOVATIVI DI ITANIUM

19

if(R1)

R2=R2+R4;

else

R7=R2-R5;

Figura 3: condizione tipo if-else

cmp. eq p1,p2=r1,r0

(p1)br. cond else_clause

add r2=r2,r4

br end_if

else_clause:

sub r7=r2-r5

end_if:\linebreak

Figura 4: codice assembler if-else

cmp.ne p1, p2=r1, r0

(p1)add r1=r2, r4

(p2)sub r7=r2, r5

Figura 5: codice assembler if-else trasformato con predicati

ma non detto che vengano predette nel modo esatto. Ogni condizione che non é

predetta esattamente, porterá a una perdita di colpi di clock, poiché le istruzioni

caricate non sono quelle esatte e si deve eseguire un’altra parte di codice. La

perdita é proporzionale alla lunghezza della pipeline, perché quando si ha una

prediction errata la pipeline viene svuotata e si perderanno tante piú istruzioni

quanta la sua lunghezza. Siccome la pipeline di Itanium é lunga 8 stages il numero distruzioni che vengono perse puó essere significativo. Nello pseudocodice

in figura 1. 3 c’é una condizione sul registro R1. Se é vera si esegue il codice

R2=R2+R4, altrimenti il codice R7=R2-R5. La condizione sará predetta con i

meccanismi sopra descritti. Se la condizione su R1 é predetta in modo erroneo si

perdono fino a 10 clock. I prediacati sono un modo per permettere al processore

di eseguire o ignorare delle istruzioni. Si basano sull’uso dei predicate registers

che sono lunghi 1 solo bit e valgono o TRUE o FALSE. I predicati precedono le

istruzioni in questo modo:

(p1)R2=R3+R4

L’istruzione R2=R3+R4 verrá eseguita solo se il valore di p1 é TRUE cioé

1, altrimenti l’istruzione verrá considerata come una nop e ignorata. Il codice

esempio di prima che tradizionalmente era compilato come in figura 1.4

La prima istruzione di compare paragona R1 con R0 che vale sempre 0, se

é vera setta P1=1 e P2=0. L’istruzione successiva br(branch) verreseguita sole

se P1 uguale a 1 ciose R1==0. Questo modo di procedere anche nel caso di

un codice cosı́ semplice porta a una perdita di colpiú di clock, perché anche

20

se il codice é lungo solo due colpiú di clock considerando che la condizione é

predetta in modo erroneo il 30% delle volte si ottiene una lunghezza media di

(2 clock+(30%*10clock)=5. Trasformando il codice compiú lato con i predicati

come in figura 1.5.

In questo modo sono stati eliminati i salti nel codice e il processore semplicemente ignorerá le istruzioni che non devono essere eseguite . Il codice

durerá sempre 2 colpi di clock senza avere nessun ritardo causato da un’erronea

previsione del branch.

Parte II

Assembler Itanium

21

Capitolo 1

Descrizione dell’assembler

Itanium

1.1

Formato delle istruzioni

Le istruzioni vengono scritte nella forma:

ISTR R1=R2, R3

R1 é l’operando destinazione, R1 e R2 sono gli operandi sorgente. Le istruzioni

Itanium hanno molti modificatori, alcuni per la dimensione delle istruzioni(per

esempio load 4 bytes o 8 bytes), altri che definiscono delle ulteriori indicazioni

per l’istruzione. I modificatori possono essere trovati o attaccati all’istruzione

come per esempio nel caso della load :ld4 o ld8, oppure separati dall’istruzione da

un punto, come per esempio ld8.fill.sa. L’assembler Itanium offre una grande

varietá di istruzioni con molti modificatori disponibili in modo da offrire al

programmatore la possibilitdi controllare anche i comportamenti piú sottili del

processore e dell’architettura. Un esempio sono le istruzioni che permettono di

controllare la cache.

1.2

Registri

Dato l’alto numero di registri i nomi dei registri sono molti, e alcuni registri

hanno anche 2 denominazioni. Molti non hanno accesso diretto dal programma,

ma vengono usati e modificati solo dal processore. I general purpose registers

sono i registri piú usati. Gli application registers sono registri che controllano

le funzioni del processore piú svariate, dal mascheramento degli interrupt, alla

scelta dell’uso di memory reference big o little endian, al controllo del register

stack. Qui verrá soltanto analizzato luso dell’application register ar.pfs; per

approfondimenti si rimanda a [2]. Il registro ar.pfs viene usato per controllare

il register stack engine, ovvero il meccanismo che controlla il register stack.

I Control Registers servono per memorizzare lo stato del processore e i suoi

parametri.

23

24

CAPITOLO 1. DESCRIZIONE DELL’ASSEMBLER ITANIUM

REGISTERS TYPE

General purpose registers

Floating-point registers

Application registers

Control Registers

Instruction TLB traslation registers

Data TLB translation registers

Predicate Registers

NOTAZIONE ASSEMBLER

r

f

ar

cr

itr

dta

p

ACCESSO INDIRETTO

Y

Y

Tabella 1.1: principali registri Itanium

1.3

Procedure

Le procedure in assembler Itanium vengono scritte in questo modo:

1

2

3

4

5

6

7

8

9

10

.text

.global encrypt

.proc funzione_di_encrypt

encrypt:

alloc loc0=ar.pfs, 3, 20, 0, 0

...

istruzioni

...

br. ret.sptk.many b0;;

.endp funzione_di_encrypt

La riga 2 serve a rendere visibile all’esterno la funzione encrypt, dichiarandola

global. La procedura viene aperta dalla riga 3, e viene chiusa dalla riga 10. La

riga 4 é l’entry point, il punto a cui si salta quando viene chiamata la procedura. L’istruzione alla riga 5 alloca sullo stack 20 registri local e 3 registri di

input. Per ulteriori informazioni sull’istruzione alloc vedi la sezione istruzioni

principali. L’istruzione alla riga 9 é l’istruzione di ritorno, i vari modificatori

vengono spiegati nella sezioni istruzioni. All’interno della procedura, al posto di

usare i registri Rxx, si possono utilizzare i registri In, loc e out; questo facilita

la scrittura del codice. Al posto dei puntini del codice precedente potrá quindi

trovare istruzioni del tipo:

mov

xor

add

mov

loc2=in0

loc2=loc2,loc3

loc3,loc2,loc5

out1=loc3

Si ricorda che i registri out non servono per passará e i valori di ritorno, ma solo

per passará e i valori in input alle procedure. Per passará e i valori di ritorno si

usano i registri r8-r11.

1.4

Explicit Bundle

Quando si scrive l’assembler Itanium si puó porre uno stop implicito al processore; questo significa che tutte le istruzioni dopo lo stop verranno eseguite nel

colpo di clock successivo. Lo stop espresso con ;; esempio:

1.4. EXPLICIT BUNDLE

xor

add

and

sub

25

loc2=loc2, loc3

loc3,loc2,loc5;;

loc7=loc20,loc21

loc5=loc4,loc19

Il processore esegue le prime due istruzioni in un colpo di clock, dopodiché

incontra lo stop ed esegue le altre 2 istruzioni nel colpo di clock successivo.

E’ possibile scrivere l’assembler con Bundle espliciti, ovvero si puó comunicare

al processore come le istruzioni verranno codificate ed eseguite. Ogni Bundle

composto da tre slot, cio3 istruzioni; il processore puó eseguire al massimo 2

bundle alla volta, ovvero 6 istruzioni. I Bundle vengono indicati con parentesi

graffe . All’inizio del Bundle si puó scivere il tipo di Bundle. esempio:

{. mmi

add loc3, loc2, loc5

add loc7=loc7,loc8

xor loc2=loc2,loc3

}

{. mmi

ld4 loc9=[loc9]

ld4 loc10=[loc10]

shr loc11=loc11,3

}

Qui sono indicati 2 boundle, entrambi di tipo memory-memory-integer. In ognuno ci sono 3 istruzioni che devono essere nel posto giusto allinterno del Bundle.

Ad esempio, le istruzioni Integer vanno all’ultimo slot. Per ulteriori informazioni su come avviene l’esecuzione o i vari tipi di Bundle vedere la sezione

Architettura.

26

CAPITOLO 1. DESCRIZIONE DELL’ASSEMBLER ITANIUM

Capitolo 2

istruzioni principali

2.1

1

2

3

4

Add

add r1=r2,r3

add r1=r2,r3,1

adds r1=imm14,r3

addl r1=imm22,r3

La add ha la forma o add registro registro come in 1, o add registro immediato

come in 3. In 2 l’operazione svolta r2+r3+1. Ci sono 2 forme per gli add con

immediati, perché Itanium distingue tra immediati di lunghezze diverse. La

causa di questo é il formato delle istruzioni. Anche se ogni istruzione viene

codificata sempre su 41 bit, i campi cambiano, e in alcune istruzioni é possibile

inserire immediati solo di certe dimensioni. Qui si distingue tra immediati di

14 bit o minori, e quelli di al max 22 bit. Se si deve sommare una costante con

piú di 22 bit bisogna prima caricare la costante con una movl in un registro.

2.2

Alloc

1 alloc r1=ar.pfs,i,l,o,r

La alloc alloca sullo stack register il numero di registri richiesto che risulta la

somma di i+l+o. i sta per registri di input, il numero di registri in cui vengono

passate le funzioni. l sta per local, il numero di registri usati internamente dalla

procedura. o sta per output, il numero di registri usati per passare paramatri

alle sottoprocedure. R sta per rotating, controlla il meccanismo di rotazione

dei registri. Vedere Register Rotation per approfondimenti. In questo caso r é

sempre posto a zero. ar.pfs é l’application register che controlla lo stack engine,

ovvero il meccanismo di register stack. esempio:

alloc loc1=ar.pfs,2,10,0,0

Questa istruzione alloca sullo stack register 12 registri, di cui i primi due sono

usati per ricevere i parametri di ingresso, 10 sará anno usati internamente alla

funzione. I registri disponibili per la procedura saranno loc1-loc13.

27

28

CAPITOLO 2. ISTRUZIONI PRINCIPALI

2.3

1

2

And

and r1=r2,r3

and r1=imm8,r3

Quando si usano delle costanti, la massima lunghezza della costante é di 8 bit,

oltre bisogna caricare la costante in un registro con una movl ed usare la forma

1.

2.4

Cmp-Cmp4

Compare e Compare 4 bytes sono le due istruzioni di compare, compare 4 byte

é usata per confrontare i valori a 32 bit. Esistono molti modificatori per queste

2 operazioni. Ci sono modificatori per i valori con segno, senza segno e che

determinano come i predicate register verranno settati. La forma base

1

2

cmp.crel p1, p2=r2,r3

cmp4.crel p1, p2=r2,r3

crel puó essere eq per equal, ne per non equal, lt per low than, ecc. Vengono

confrontati i due valori contenuti in r2 e r3. Le istruzioni settano i due predicate

registers p1 e p2 a seconda che la condizione sia vera o falsa. Se la condizione é

vera p1 e posto a 1, se é falsa p1 posto a 0. P2 vienesettato sempre all’inverso

di p1, se p1 vale 1 p2 vale 0 e viceversa. I due predicate registers possono poi

essere messi nel codice precedendo le istruzioni. esempio:

(p1) add loc7=loc7,loc5

(p2) add loc7=loc7,loc6

A seconda che la condizione sia vera o falsa loc7 sará sommato o loc5 o loc6.

2.5

Dep

1 dep r1=r22,r3,pos6,len4

dep. z r1=r2,pos6,len6

Deposit serve per prelevare da un registro un gruppo di bit che iniziano al bit

0, di lunghezza specificata da len4, per poi depositarli in un altro registro alla

posizione indicata da pos4. puó essere utile in alcuni casi, l’unico problema che

la lunghezza del gruppo di bit che vengono depositati al massimo espressa su 4

bit, ed il gruppo di bit quindi al massimo di 15 bit. Se si vuole fare deposit di

un numero di bit superiore non c’é modo. La seconda versione dep.z azzera i

bit del registro destinazione e ha valori di pos e len su 6 bit.

2.6

1

2

Extr

extr r1=r3,pos6,len6

extr.u r1=r3,pos6,len6

2.7. LD

29

Extract, al contrario di dep, estrae un gruppo di byte da un registro e li mette

in un altro registro a partire dal bit 0. Il gruppo di bit di lunghezza len6 e inizia

in posizione indicata da pos6. Questa istruzione molto utile perché permette

di selezionare dei bit da un registro, operazione molto comune negli algoritmi

crittografici. L’unico punto a sfavore é che se ne puó eseguire solo una per colpo

di clock.

2.7

Ld

La load ha molte forme e molti modificatori; questi permettono di specificare

quanti byte devono essere letti da memoria, se la cache deve considerare il valore

caricato come di uso frequente oppure no, se la cache deve fare l’advance load

della word successiva al valore caricato in vista di una load uleriore o no, e cosı́

via. I modificatori non verranno presentati qui. Per approfondimenti consultare

[1].

1

2

3

ldsz r1=[r3]

ldsz r1=[r3],r2

ldsz r1=[r3],imm9

sz sta per size; puó valere 4, 8 o 16, indicati quanti nyte sono letti. In tutte e

tre le forme l’indirizzo contenuto in r3. In 2 il valore di r3 aggiornato dopo la

load, sommando r2. In 3 dopo la load a r3 viene sommato un immediato di 9

bit. Le ultime 2 forma sono di autoincremento.

2.8

1

2

3

4

5

6

Nop

nop imm21

nop.i imm21

nop.b imm21

nop.m imm21

nop.f imm21

nop.x imm62

La nop é molto importante perché usata per riempire gli slot vuoti. Quando

si hanno meno di 3 istruzioni per formare un bundle si possono usare delle

nop per arrivare a tre istruzioni e usará e l’explicit bundling. Gli immediati

sono ignorati dal processore, possono servire solamente come demarcazione in

punti del programma. Esistono differenti tipi di nop; la prima solo una pseudo

operazione e viene mappata su una delle successive. Ogni nop puó andare ad

occupare un’unitá funzionale diversa, una unitá integer o di branch, oppure di

memory, oppure di floating point o una x unitá .

2.9

Mix-Mux

Per queste istruzioni si rimanda al mauale Intel [1].

30

CAPITOLO 2. ISTRUZIONI PRINCIPALI

2.10

1

2

3

4

Shl

Shr r1=r3,r2

shr.u r1=r3,r2

shr r1=r3,count6

shr.u r1=r3,count6

Lo shift Left semplicemente shifta a destra R3 di n posizioni pari al contenuto

di R2 o dell’immediato count su 6 bit.

2.11

1

2

Shr

Shl r1=r3,r2

shr r1=r3,count6

Lo shift Right semplicemente shifta a destra R3 di n posizioni pari al contenuto

di R2 o dell’immediato count su 6 bit.

2.12

R2

Shrp

R3

R1 Figura 2.1: Shrp

1

shrp r1=r2,r3,coun6

shif right pair é un’operazione molto utile: serve per eseguire i rotate fissi sia a

destra che a sinistra. I due operandi r2 e r3 sono affiancati e considerati come

un unico blocco di 128 bit; da questo blocco vengono selezionati 64 bit, a partire

dalla posizione specificata da count6, e messi in un altro registro, come si puó

vedere in figura 2.1. Per ottenere uno shift fisso, bisogna avere il valore da

routare da 32 bit in r2. Si deve mettere lostesso valore in r3, ma nella parte

alta del registro. Cosda avere, una volta eseguita la shrp, il valore da routare 2

volte affiancato. Poi in count6 si mette un valore pari a 32+il numero di bit di

cui si vuole il rotate a sinistra oppure 32-il numero di bit di cui si vuole il rotate

a destra. In r3 nei primi 32 bit si avrá il valore routato dei bit voluti. Unica

accortezza é quella di azzerare i bit da 32 a 64 di r3, (quando necessario).

2.13. XOR

2.13

1

1

31

Xor

xor r1=r2,r3

xor r1=imm8,r3

I due operandi sorgente sono r2 e r3 e quello destinazione r1, in caso di immediato la limitazione é che l’immediato deve essere su al massimo su 8 bit.

32

CAPITOLO 2. ISTRUZIONI PRINCIPALI

Parte III

Ottimizzazione degli

Algortimi

33

2.14. INTRODUZIONE

2.14

35

Introduzione

In questa parte verranno presentati gli algortimi ottimizzati. La parte degli

algortmi é strutturata in modo da permettere una lettura piú semplice o una

piú approfondita. Per ogni algoritmo vi é prima una parte che descrive in modo generale le caratteristiche dell’algortimo e le ottimizzazioni eseguite. Nella

sezione successiva, chiamata ottimizzazione in dettaglio, vengono forniti maggiori dettagli, e vengono anche presentate e spiegate parti di codice assembler.

La sezione Ottimizzazioni in Itanium riassume il lavoro svolto specificatamente

per Itanium, traendo le conclusioni finali. Nel capitolo linee generali vengono

introdotti dei metodi di ottimizzazione generali, validi per tutti gli algortimi e

sono illustrate le situazioni che si incontrano spesso in tutti gli algoritmi.

36

Capitolo 3

Linee generali

3.1

Ottimizzazione generale del codice

Le parti del codice che subiscono ritardi e su cui si puó operare un’ottimizzazione

sono,in generale, le seguenti:

• load-store

• cicli tipo for o while

• jump

3.1.1

Load-Store

Il discorso sulle load vale per tutte le architetture su cui si usano le load, in

generale nei processori RISC. Le load dalla memoria impiegano minimo 2 colpi

di clock per essere eseguite; questo vuol dire che,dopo la load ,deve passare un

colpo di clock prima di poter usare il valore caricato. Questo colpo di clock

andrá sprecato. Il modo per risolvere il problema é anticipare il piú possibile le

load, in modo tale da avere i valori caricati dalla memoria il prima possibile. Non

tutte le load saranno anticipabili nel codice perché questo dipende da quando

l’indirizzo a cui fa riferimento la load disponibile nel codice. Nel caso in cui

l’istruzione di load e quella che ne usa il risultato siano vicine, il colpo di clock

tra le due istruzioni deve essere riempito con istruzioni che non siano dipendenti

dalla load, e far sı́ che possano essere eseguite prima del completamento della

load. esempio:

1 xor R45=R45, R39

2 ld4 R40=[R40];;

3 xor R42=R40,R41

4 add R45=R45,R46

5 sub R47=R47,R50;;

6 xor R45=R45,R47;;

Dopo la Load ci sará un colpo di clock in cui il processore non usato perché

l’istruzione successiva di xor usa R40 che é il risultato della load. Si puó notare

come le istruzioni 4 e 5 non dipendano dalla load. Il codice eseguito in 4 colpi

di clock. Trasformando il codice cosı́

37

38

CAPITOLO 3. LINEE GENERALI

1 xor R45=R45, R39

2 ld4 R40=[R40];;

3 add R45=R45,R46

4 sub R47=R47,R50;;

5 xor R42=R40,R41

6 xor R45=R45,R47;;

Il buco dopo la load é stato riempito con le due istruzioni e il codice eseguito in

3 colpi di clock. Per le store il discorso é inverso; esse possono essere posticipate

nel codice, ed eseguite quando si hanno degli slot liberi.

3.1.2

Cicli e loop unrolling

Il classico ciclo del tipo:

for i=1 to 10 do

a[i]=a[i-1]+b

c=c+f

Quando questo ciclo compilato per ogni iterazione del ciclo verrá perso minimo

un colpo di clock, perché al termine ci sará un’istruzione di compare che verifica

se si é arrivati alla fine del ciclo e ci sará un salto al codice iniziale per una

nuova iterazione. In realtá dipendentemente dall’architettura, si perderanno

molti piú colpiú di clock tanto piú é lunga la pipeline. Essendo la pipeline

Itanium molto lunga, si perderanno anche 10 colpi di clock per iterazione. La

soluzione il loop unrolling, cioil codice viene srotolato, invece che usare il for

si scrivono esplicitamente le varie iterazioni del ciclo, in modo da eliminare i

branch al fondo di ogni iterazione. esempio:

iterazione 1

a[1]=a[0]+b

c=c+f

iterazione 2

a[2]=a[1]+b

c=c+f

iterazione 3

a[3]=a[2]+b

c=c+f

iterazione 4

a[4]=a[3]+b

c=c+f

. . .

. . .

Il loop unrolling dá anche un’altra opportunitá perché ora che abbiamo le operazioni una dopo l’altra si puó sfruttare il parallelismo del codice operando uno

scheduling sulle istruzioni, ovvero riordinando ed eseguendo quante piú operazioni possibili in parallelo. Ci sono due tipi di cicli: i cicli in cui le varie iterazioni

sono dipendenti le una dalle precedenti, e quelle in cui sono invece indipendenti

tra di loro. Il caso di prima quello in cui un’iterazione del ciclo dipende dalla precedente. piú le iterazioni sono indipendenti, piú si avrá parallelismo nel

codice e piú si avrá beneficio dal loop unrolling e dall’ottimizzazione.

3.2. OTTIMIZZAZIONE DELL’ASSEMBLER

3.2

39

Ottimizzazione dell’assembler

Quando si ha un codice assembler, quello che limita il parallelismo e la velocitá

del codice sono :

• dipendenze di dato

• dipendenze di nome

• dipendenze di controllo

Le dipendenze di dato sono quelle in cui un’istruzione ha come operando un

input un valore che l’output di una precedente operazione, quindi tra le due c’é

una dipendenza di dato. esempio:

XOR R40=R40,R42

ADD R41=R40,R46

Sono proprio queste dipendenze per cui non si puó fare nulla; esse sono indipendenti dall’architettura su cui viene compilato il codice e limitano il parallelismo

del codice. Le dipendenze di nome sono quelle in cui due istruzioni usano lo

stesso registro, ma non c’é dipendenza di dato tra le due. esempio:

XOR R40=R41,R42

ADD R41=R39,R32

Queste dipendenze possono essere evitate nella scrittura del codice semplicemente cambiando il nome ai registri coinvolti. In particolare in Itanium, dato il

gran numero di registri, non si verificano spesso dipendenze di questo tipo. Le

dipendenze di controllo sono quelle relative ai branches. Un’istruzione dentro

ad un if é dipendente dalla condizione dell’if e dal branch che eventualmente

verreseguito. E’ utile,dove possibile, trasformare le dipendenze di controllo in

dipendenze di dato. In Itanium ,per risolvere questo problema, esiste il meccanismo di Predication, che grazie ai predicati, come spiegato nell’apposita sezione,

permette al processore di eseguire o meno delle istruzioni.

3.3

Fasi di Ottimizzazione degli Algoritmi

Per Ottimizzare gli algoritmi di openssl sono state eseguite le seguenti fasi:

1. Stdio approfondito dell’algoritmo

2. scelta dell’implementazione

3. traduzione in assembler dello pseudocodice o codice C

4. debug

5. ottimizzazione e riordinamento del codice

6. debug

40

CAPITOLO 3. LINEE GENERALI

Lo studio dell’algoritmo ha lo scopo di capire le caratteristiche principali dell’algoritmo e il suo funzionamento. La fase successiva prevede di scegliere tra

le varie implementazioni dell’algoritmo quella che piú si adatta all’architettura Itanium, e se necessario apportare delle modifiche a queste implementazioni

che sono scritte in pseudocodice o in C. Scelta l’implementazione, questa viene

tradotta in assembler Itanium, dopo che si sono scelte le istruzioni da usare. In

alcuni casi sono state eseguite prove con differenti versioni di codice assembler

per vedere quale risultava il piú efficiente. Un esempio é la permutazione iniziale

del DES, di cui sono state realizzate 2 versioni: una usando l’istruzione extr. u

e l’altra usando solo shift+and. Attraverso una lunga fase di Debug, nella quale

vengono testati i vari spezzoni di codice uno per uno per poi essere montati

insieme, si arriva ad una versione funzionante del codice assembler. A questo

punto il codice non ancora ottimizzato, anzi, puó addirittura risultare piú lento

del codice in C. Nella fase di ottimizzazione vengono apportare le ultime modifiche al codice per renderlo piú veloce possibile e soprattutto vengono riordinate

le istruzioni e racchiuse in budles. La fase di scrittura del codice e quella di

ottimizzazione non sono del tutto separate, perché mentre si scrive il codice si

cerca di scriverlo giá ottimizzato o comunque pronto per esserlo in un ulteriore

fase. La fase di riordinamento del codice é essenziale e deve essere eseguita con

cura, perché si rischia di perdere colpi di clock solo invertendo l’ordine di due

istruzioni.

3.4

3.4.1

Operazioni presenti in tutti gli algoritmi

Uso di Costanti

Gli algoritmi usano spesso costanti da sommare o mettere in xor. Di solito queste

sono costanti a 32 bits. Dato l’alto numero di registri disponibili, é conveniente

caricarle all’inizio dell’algoritmo in un registro e mantenerle, in modo da non

doverle piú ricaricare. Per questo si usa l’istruzione movl(move long). esempio:

movl R50,0x0000000034b56a76

L’istruzione movl usa 2 slot all’interno del bundle; per questa ragione é meglio

usarla in uno spazio del codice in cui c’é uno spazio libero di 2 slot. E’ facile che

si generi uno split issue se non posizionata bene. Di solito si usa in un bundle

con prima un’istruzione Ingeger o ALU. ES:

{

xor R43=r44,R45

movl R50,0x0000000034b56a76

}

3.4.2

Selezione di bits da registro

Un’operazione molto comune consiste nel dover selezionare un gruppo di bits da

un registro. Questa operazione é eseguita di solito con uno shift + un and. Co

lo shift si porta il gruppo di bits da selezionare in basso nel registro, con l’and e

una maschera opportuna si selezionano solo i bits che occorrono. Per esempio,

per selezionare i bits dal 20 al 26 del registro R40. Le operazioni da compiere

sono:

3.4. OPERAZIONI PRESENTI IN TUTTI GLI ALGORITMI

41

Shift right R40 di 20 posizioni

and R40,0x3f

Su Itanium, poiché i registri sono da 64 bit, per poter eseguire un and con una

maschera piú lunga di 22 bit si deve caricare la maschera in un registro con una

movl. Un altro modo per selezionare i bits dato dall’uso dell’istruzione extr.

Questa é studiata apposta per selezionare un insieme di bits da un registro e

posizionarli in un altro registro. Sembrerebbe che con una sola istruzione si

possa eseguire il tutto. In realtá quando le selezioni di bits da registro sono

molte (come accade negli algoritmi esaminati), l’uso di extr. u non é molto

conveniente. La questione che extr.u é eseguibile solo dall’unitá funzionale I0, e

quindi una sola extr.u puó essere eseguita per colpo di clock. Usando shift+and,

gli shift possono essere eseguiti dalle unitá funzionali I0 e I1, quindi si possono

eseguire 2 shift per colpo di clock. In ogni caso si eseguono al massimo 2 selezioni

di bits da registro ogni 2 colpi di clock. In molti casi ho preferito usare gli shift

perché sono piú facilmente riorganizzabili e pongono meno limitazioni, mentre

gli extr.u sono molto limitativi in quanto possono essere eseguiti solo da una

unitá funzionale.

3.4.3

Look up in tabella

Per eseguire il look up in tabella c’é bisogno dell’indirizzo base di questultima;

esso sará caricato in un registro, dopodiché é necessario un displecement che sará

sommato alla base. Itanium supporta solo le load in cui l’indirizzo contenuto

in un registro, quindi non si possono usare modi di indirizzamento complicati

come base+displecement, ma i due valori vanno sommati preventivamente. Il

valore base della tabella va dichiarato nella sezione data, per esempio se il nome

della tabella é Te0:

. data

. global Te0#

successivamente si carica l’indirizzo in un registro, si puó sommare il displacement e caricare il valore da memoria:

movl R50=Te0#

add 51=0xf, R50

ld4 R51=[R51]

3.4.4

Uso delle load

E’ frequente dover caricare da memoria valori tutti contigui in memoria. E’ il

caso delle chiavi dei round. Solitamente le chiavi dei round sono posizionate in

uno struct e i loro valori sono contigui in memoria. Siccome Itanium dispone di

load dalle varie dimensione, si possono usare load4 che carica 32 bits, load8 che

carica 64 bits ma anche load16 che carica 128 bits dalla memoria. Poi, una volta

caricati i valori, se erano necessarie unitá da 32 bits, basterá dividere i blocchi.

In realtla regola é quella di usare una load sempre della dimensione minima

necessará ia. Se si lavora su dati a 32 bit meglio usare load4 e non load8. Il

problema é che finché si usano load4, l’accesso alla cache non avrá problemi.

Quando si usano le load8, gli accessi a memoria devono essere allineati a 8

bytes. La cache supporta accessi non allineati in qualche caso, ma si rischia

42

CAPITOLO 3. LINEE GENERALI

di incappare in una penalitá in termini di colpi di clock persi. Considerando

anche il fatto che Itanium permette 2 load per colpo di clock, se si usano valori

a 32 bit, non c’é ragione di usará e load8, a meno che non sia strettamente

necessario e si sia assolutamente certi che i valori da caricare siano allineati. Un

esempio concreto stato quello di rc5: lo struct che conteneva le chiavi del round

strutturato in questo modo:

typedef struct rc5_key_st

{

int rounds;

RC5_32_INT data[2*(RC5_16_ROUNDS+1)];

} RC5_32_KEY;

Come si puó vedere, nello struct prima delle chiavi contenute in data c’é un int

di 32 4 bytes. La versione iniziale di RC5 usava le load8. Siccome le chiavi si

trovano dopo un int, sono sfasate tutte di 4 bytes, usando le load8, ci saranno

degli accessi non allineati in memoria. Il risultato é stato che il codice era

piú lento di quello originale. Modificando il codice e usando le load4 il codice

risultava piú veloce. In questo caso si era perso circa il 15-20 % delle prestazioni.

E’ molto importante non mischiare load4 con load8.

3.4.5

Xor tra una serie di valori

A volte nel codice sono presenti linee di questo genere:

A=A^B^C^D^E^F^G

Questo codice sará compilato in modo da eseguire uno xor alla volta. In realtá ,

siccome lo xor é un’operazione che gode di proprietá commutative e associative,

il codice sopra puó essere eseguito in 3 colpi di clock invece che in 6. Se si

ipotizza che i valori di A, B, C. . siano contenuti nei registri R40, R41, R42,

R43, R44, R45, R46, Il codice puó essere riscritto come:

1 clock

xor R40=R40,R41

xor R48=R42,R43

xor R49=R44,R45

2 clock

xor R40=R40,R48

xor R49=R49,R46

3 clock

xor R40=R40,R49

Dato il gran numero di registri disponibili in Itanium é opportuno usare piú

registri e risparmiare colpi di clock.

3.4.6

Htonl Ntohl

In tutti gli algoritmi c’é il problema di interpretare le word o come host order o

come network order. Per trasformare una word da host order a network order

e viceversa, i singoli byte devono essere scambiati di posto nella word in questo

modo:

3.4. OPERAZIONI PRESENTI IN TUTTI GLI ALGORITMI

43

host order:

B1 B2 B3 B4

network order: B4 B3 B2 B1

Per eseguire tale operazione normalmente si usano degli shift piú or. In Itanium

ci sono delle istruzioni particolari come la mux. Queste istruzioni fanno esattamente questa operazione. Quindi, per convertire da host to network order e

viceversa, l’ideale é usare l’istruzione

mux1

3.4.7

R32=R33,@rev

Uso dei bundles per le istrzioni assembler

Si puó usare sia l’explicit Boundling che l’implicit Boundling. Con l’implicit

Boundling il compilatore deciderá i boundling, i dual issue e gli split issue.

Usando l’explicit Boundling, si ha il pieno controllo sul processore, si sa quale istruzione verrassegnata a quale unitá funzionale, si sa quando il processore

caricherun nuovo bundles, e quali istruzioni verranno eseguite in un dato colpo

di clock. Se si decide di usará e i Bundles, é preferibile racchiudere in Bundles

TUTTE le istruzioni del codice, non soltanto quelle piú critiche. E’ sconsigliabile mischiare istruzioni racchiuse in Bundles con operazioni non racchiuse in

Bundles. Questo perché il compilatore in alcuni casi inserisce uno split issue

anche dove non serve, e tutto il lavoro di perfezionamento del codice é inutile

se si perdono colpi di clock in questo modo. Inoltre, é anche difficile vedere

dove il compilatore ha inserito lo split issue, perché bisogna operare con un debugger sul codice compilato e controllare linea per linea se il codice come ce lo

aspettavamo. Per esempio se inserisco un codice di questo tipo:

{. mii

load4 R40,[R40]

xor R41=R41,R42

shr R43=R43,2

}

xor R44=R44, R48;;

Tutte queste istruzioni possono essere eseguite nello stesso colpo di clock perché

non hanno dipendenze fra di loro. Come si vede le prime tre sono racchiuse