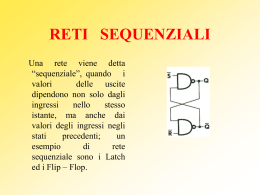

G.- F. Dalla Betta, G. Soncini. Appunti di Elettronica 2. Capitolo V Reti sequenziali V.1. Considerazioni generali V.2. Flip-Flop V.3 Esempi applicativi V.4 Implementazioni circuitali 1 Sistema Combinatorio: L’uscita del sistema in un particolare istante è determinata unicamente dal valore presente agli ingressi in quel determinato momento. In un circuito combinatorio il segnale si propaga attraverso le varie porte logiche solo in una direzione, senza mai propagarsi da una porta logica ad una precedente. Sistema Sequenziale: L’uscita del sistema non dipende solo dal valore presente agli ingressi, ma anche dalla “storia” precedente del sistema stesso. Nei circuiti sequenziali si utilizza la retroazione (feedback) per creare elementi dotati di memoria (Flip-Flop). Ramo di retroazione (feedback) 2 3 RETROAZIONE (FEEDBACK) • La retroazione consiste nel prelevare una copia del segnale d’uscita di un sistema e riportarla in ingresso al sistema stesso. i0 i1 SISTEMA out Feedback • Il segnale “retroazionato” può essere sommato (reatroazione positiva) o sottratto (retroazione negativa) agli ingressi del sistema. • I circuiti che si prenderanno in considerazione di seguito sfruttano la retroazione positiva che tende a portare il sistema in uno dei suoi stati estremi (può anche provocare oscillazioni) 4 Esempio di retroazione: oscillatore ad anello IN CS D IN* OUT VOUT Il punto Vin=Vout è un punto di equilibrio instabile. La retroazione porta il sistema ad oscillare (con periodo D) , rendendolo instabile. IN=OUT OUT=IN VIN Period 2(D+s) IN s D OUT time 5 V.2. FLIP-FLOP FLIP: circuito in cui si sfrutta la retroazione per realizzare un sistema dotato di memoria. F N Q • In questa configurazione e’ di scarsa utilità perché, una volta memorizzato il dato (1), non lo si può più cancellare. Commutazione dell’ingresso F N Q Accensione del circuito FLIP-FLOP SET RESET (FF-RS, oppure SR Latch) Idea base: sostituisco l’invertitore del FLIP con un secondo NOR. RESET Q SET • Ho una doppia retroazione delle uscite sugli ingressi ed inoltre altri due ingressi esterni (SET e RESET). • Risolvo quindi il problema del FLIP, perche’ con RESET=1 (e SET=0) posso cancellare lo stato precedentemente memorizzato. • Al contrario, con SET=1 e RESET=0 impongo Q=0 • Infine, con SET=0 e RESET=0 il circuito conserva la situazione precedente, che dipende dalla “storia passata” degli ingressi. 6 7 Tabella della Verità per FF-RS R S 0 0 0 1 Q non cambia 1 1 1 0 0 problema ! 0 1 N.B. Lo stato S=R=1 è critico ! Infatti, le uscite si portano entrambe a 0 ed il sistema si porterà in uno stato oppure in altro a seconda di quale ingresso torna per primo a 0. Caso 1 Caso 2 t0 t1 R S Q 1 1 0 0 1 1 R S Q 1 1 0 1 0 0 t2 0 0 0 1 0 0 • Non potendo garantire la commutazione simultanea degli ingressi, impongo che possa cambiare un solo ingresso alla volta e proibisco la condizione SET = RESET = 1. 8 Realizzazione del flip-flop SR Ci si riconduce ad una tabella della verità, definendo gli stati QN (stato attuale del FF) e QN+1 (stato futuro del FF). Non cambia S R QN QN+1 SET RESET Non permesso R 0 0 S 0 0 QN 0 1 QN+1 0 1 0 1 0 1 0 1 1 1 0 0 1 0 1 1 0 0 1 1 1 1 0 1 NA NA 9 Realizzazione a NAND del flip-flop SR RS QN 0 1 00 0 1 01 1 1 11 - 10 0 0 QN +1 S + R QN R R QN S Q QN+1 S Realizzazione a NOR del flip-flop SR RS QN 0 1 00 0 1 01 1 1 11 - QN +1 R S + QN ) 10 0 0 Q S R Q QN+1 S QN Q R 10 Problemi del flip-flop SR Il latch SR è sensibile agli istanti di commutazione degli ingressi: in presenza di GLITCH il FF-SR si trova per un attimo nello stato S=1, R=0 e Q viene settato a 1. Una volta che S torna a 0 Q rimane alto. A Generatore di glitch Quindi, se mettessi un invertitore per evitare la condizione non permessa S=R=1, a causa del ritardo dell’invertitore, avrei comunque un periodo di Condizione proibita tempo in cui S=R=1. A A D A D 11 FLIP-FLOP SR Level Sensitive (con il Clock) Per risolvere i problemi visti in precedenza utilizzo un segnale di clock: Quando CK=1 il FF è “trasparente“ CK=0 il FF si trova con S=R=0 e conserva l’ultimo stato. Facendo in modo che il CK commuti allo stato alto soltanto dopo che gli ingressi Se R si sono assestati elimino il problema dei glitches. A A A CK S Q 12 FLIP-FLOP D (D-Latch) Quando CK=1 il D-Latch lascia passare il segnale da D a Q CK=0 il D-Latch mantiene memorizzato l’ultimo valore Esempio di applicazione: convertitore A/D Impulso che dice al conv. A/D di effettuare una conversione Tempo necessario per effettuare una conversione 13 Esempio di applicazione: convertitore A/D START Ingresso analogico A/D REF D0 D1 D2 Dn BUSY Uscita digitale I bit di uscita devono essere immagazzinati e fatti scorrere lungo uno shift register. 14 Utilizzo un array di D-Latch per mantenere i bit di uscita in attesa che sia disponibile il nuovo valore.Abilito il D-Latch utilizzando il segnale di uscita BUSY dell’A/D. • Appena BUSY=0, i DLatch diventano trasparenti e l’uscita viene aggiornata. • Quando il convertitore è occupato ad effettuare una conversione si ha BUSY=1, BUSY=0 e i D-Latch sono in stato di mantenimento. 15 Registro a scorrimento (SHIFT REGISTER) Se provassi a realizzare lo shift register utilizzando dei D-Latch: Non funziona! • L’uscita che ci si aspetta dallo shift register e’ quella che corrisponde allo scorrimento del dato lungo il registro • In realtà, appena il CK=1, tutti i D-Latch diventano trasparenti e il dato si propaga rapidamente lungo tutta la catena. 16 Funzionamento corretto 17 Funzionamento sbagliato FLIP FLOP Master-Slave 18 L’invertitore fornisce allo Slave un clock negato e ritardato di D rispetto al clock che abilita il Master. In questo caso il dato attraversa il FF-M/S solo sui fronti di discesa di CLK. Diagramma di temporizzazione del FLIP FLOP Master-Slave 19 • In questo FF-M/S il dato viene aggiornato (cioè cambia l’uscita dello Slave) sul fronte di discesa di CLK (system clock); questa versione del FFM/S è detta Negative Edge Triggered. 20 Registro a scorrimento con FF M/S Il dato attraversa il FF M/S solo sui fronti di discesa di CK 21 FLIP FLOP J-K L’idea è quella di utilizzare la condizione proibita di un FF-SR (R=S=1). Schema circuitale del FF J-K Tabella della Verità J K 0 0 0 1 Q non cambia 0 1 1 1 inverte 0 1 QN +1 J QN + K QN • Ora la condizione J=K=1 è permessa e provoca l’inversione dello stato precedente del FF. QN +1 QN • Se J=K=0 allora attraverso AND2 passa QN che arriva al D-latch • Se J=K=1 allora attraverso AND1 passa QN FLIP FLOP D Edge Triggered In alternativa al FF M/S posso realizzare un FF Edge Triggered in questo modo. N.B. Non necessita’ di utilizzare clock e clock complementare. a) Consideriamo dapprima lo stato CK=1 e Data=1. 1 22 23 b) Poi vediamo cosa succede quando CK commuta da 1 a 0. • Questo schema circuitale realizza quindi un D-Latch Edge Triggered (sul fronte di discesa del clock). Realizzazione FLIP FLOP D Edge Triggered Implementazione a NAND 24 Segnali asincroni (PRESET/RESET) Gli schemi circuitali dei FF possono essere complicati con l’aggiunta di 2 ulteriori ingressi (PRESET e RESET) che consentono di fissare il valore dell’uscita Q a 0 o a 1 in modo indipendente dai valori di dato e clock. Simbolo grafico 25 26 V.3. Esempi applicativi Analisi di reti sequenziali Contatori Convertitori serie/parallelo e parallelo/serie Sommatore seriale 27 Analisi di reti sequenziali. Tabella delle transizioni QC QB QA 0 0 1 Stato di 0 Stato del circuito: partenza Insieme delle uscite di tutti i FF in un dato istante di tempo 0 1 1 0 1 0 0 0 Power ON Equazioni di eccitazione DC QA DB QC DA QB Descrizione alternativa Caso più generale Rete combinatoria 28 Stato Uscita Uscita Stato Uscita N.B. Le uscite di alcuni FF possono non comparire in uscita (FF nascosti), ma tutte contribuiscono a formare lo stato del circuito. Passi da effettuare per l’analisi di circuiti sequenziali 29 1. Scomporre il circuito da analizzare evidenziando la parte contenente i F.F. e quella che costituisce la logica di eccitazione 2. Studiare la logica di eccitazione e scrivere l’espressione Booleana per ciascun ingresso dei Flip-Flop 3. Definire lo stato iniziale del circuito; solitamente si considera come stato iniziale lo stato in cui si trova il circuito immediatamente dopo l’accensione (spesso e’ lo stato ZERO) 4. Determinare il nuovo stato delle uscite e inserirlo nelle equazioni di eccitazione in modo da determinare lo stato successivo 5. Proseguire con il passo 4 utilizzando l’ultimo valore trovato fino a trovare uno stato giá incontrato in precedenza. Esempio 1 Determinare la sequenza generata dal seguente circuito sincrono partendo dallo stato QA=QB=QC=0. 30 31 Si scrivono le equazioni di eccitazione per gli ingressi Di: DA QA DB QC QA + QC QB + QA QB QC QA + QC QA + QC QB + QA QB DC QB QC QA ) QC QB QA + QC QB QA Se QAQBQC=000 allora DADBDC=110; perció i primi due stati del sistema sono 000 e 110… Mappe di K. delle equazioni di eccitazione DA, DB , DC QA QB 00 QC 0 1 1 1 01 1 1 11 0 0 DA 10 0 0 QA QB 00 QC 0 1 1 0 01 1 0 11 1 1 DB 10 0 1 QA QB 00 Q C 0 1 0 0 32 01 1 0 11 0 1 10 0 0 DC • Si inserisce l’ultimo stato d’uscita trovato nelle mappe di K. trovando l’uscita successiva e si itera il procedimento fino a ritrovare uno stato giá trovato in precedenza. • La sequenza d’uscita é perció data da: tempo QA 0 1 0 1 0 1 0 QB 0 1 1 1 1 0 0 QC 0 0 0 1 1 0 0 Valore decimale 0 6 2 7 3 4 0 Esempio 2 33 Determinare la sequenza generata dal seguente circuito facente uso di 4 FF-JK, a partire dallo stato 0000 (raggiungibile mediante RESET). • I 3 FF B, C e D ricevono come ingressi Ji=Qi-1, Ki=Qi-1 quindi si comportano come FF-D. Il FF A, invece, ha: J A K A QA QB + QC ) quindi mantiene il dato (J=K=0) oppure lo inverte (J=K=1). 34 Equazione di eccitazione per JA J A K A QA QB + QC ) QA QB + QC ) + QA QB + QC ) QA QB + QA QC + QA QB QC Mappa di Karnaugh per JA QA QB 00 QC 0 1 1 0 01 0 0 11 1 1 10 0 1 Tabella delle transizioni QA QB QC QD 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 1 0 0 0 1 1 1 0 0 0 Passi di progetto per la realizzazione di un contatore sincrono 35 1. Esprimere in codifica binaria ogni numero della sequenza da realizzare. 2. Scegliere ed implementare un metodo di assegnazione delle uscite dei flipflop (N) agli stati (M); è possibile utilizzare l’uscita di un flip-flop per ciascun bit della sequenza oppure minimizzare il numero di flip-flop (M=2N) con una codifica opportuna. 3. Disegnare la tabella degli stati “presenti-futuri” della sequenza disponendo da un lato i vari stati della sequenza (Stato attuale) e a fianco la tabella con gli stati successivi (Stato successivo). 4. Scegliere il tipo di F.F. da utilizzare; è preferibile il D-F.F. (minore occupazione di area e maggior facilitá di progetto in quanto lo stato di transizione del F.F. è determinato dallo stato di eccitazione (cioè dal suo ingresso). 5. Disegnare le mappe di K. Per ogni ingresso Di dei F.F. in funzione delle uscite Qi; gli ingressi di ogni mappa sono le uscite degli N flip-flop allo stato precedente. 6. Completare le mappe mettendo in uno stato opportuno (solitamente a Zero) gli stati non utilizzati (che rappresentano stati di indifferenza) e ricavarne le espressioni booleane minime. 7. Disegnare il sistema disponendo i flip-flop ed implementando la logica di eccitazione ricavata al punto 6. 36 Esempio Progettare un contatore sincrono che realizzi la sequenza 0 3 6 9 12 0 etc… Numero 0 3 6 9 12 Stato Attuale Q 3 Q2 Q1 Q 0 0 0 0 1 1 0 0 1 0 1 0 1 1 0 0 0 1 0 1 0 Q 3 Q2 Q1 0 0 0 0 0 1 0 1 1 1 0 0 1 1 0 Q0 0 1 0 1 0 Stato Successivo Q3 Q2 Q1 Q0 0 0 1 1 0 0 1 0 1 0 1 1 0 0 0 1 0 1 0 0 37 Mappe di Karnaugh Q3 Q2 Q1 Q0 00 01 11 10 00 10 0 12 01 09 3 11 0 6 10 1 Q3 Q2 Q1 Q0 00 01 11 10 00 10 0 12 01 09 3 11 1 6 10 0 D0 Q3 Q2 Q1 Q0 00 01 11 10 00 00 0 12 01 19 11 10 1 3 0 6 D2 D1 Q3 Q2 Q1 Q0 00 01 11 10 00 00 0 12 01 19 11 10 0 3 1 6 D3 38 Equazioni di eccitazione D0 Q3 Q2 Q1 Q0 + Q3 Q2 Q1 Q0 D1 Q3 Q2 Q1 Q0 + Q3 Q2 Q1 Q0 D2 Q3 Q2 Q1 Q0 + Q3 Q2 Q1 Q0 D3 Q3 Q2 Q1 Q0 + Q3 Q2 Q1 Q0 Schema circuitale … Contatori a riempimento/svuotamento 39 • Sono contatori particolari in cui la retroazione dalle uscite agisce direttamente sono sull’ingresso del primo FLIP-FLOP, mentre gli altri FF fanno “scorrere” i dati. • Questa situazione determina sequenze caratterizzate da un iniziale “riempimento” con 1, seguito da uno “svuotamento” (ritorno di 0). 40 Esempio Tabella delle transizioni Equazioni di eccitazione D1 Q4 D2 Q1 D3 Q2 D4 Q3 Q1 0 1 1 1 1 0 0 0 0 Q2 0 0 1 1 1 1 0 0 0 Q3 0 0 0 1 1 1 1 0 0 Q4 0 0 0 0 1 1 1 1 0 Esercizio Per il contatore in figura, determinare la sequenza degli stati a partire dallo stato ZERO (Q1Q2Q3Q4=0000). 41 42 Equazioni di eccitazione D1 Q1 Q2 1 + Q1 Q2 Q4 + Q1 Q2 Q3 + Q1 Q2 Q3 Q4 ) D2 Q1; D3 Q2 ; D4 Q3 Mappe di Karnaugh per D1 Q3 Q4 Q1 Q2 00 01 11 10 00 1 1 1 1 1 1 0 01 0 1 0 1 11 0 0 1 1 10 0 Tabella delle transizioni Q1 Q2 Q3 Q4 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 1 0 0 0 1 0 1 0 0 Convertitore serie/parallelo • E’ simile ad un registro a scorrimento, però c’è il problema che il dato convertito è disponibile per un solo ciclo di clock: - posso depositare il dato in un registro, abilitato a ricevere i dati in ingresso solo alla fine della conversione; - posso modificare la struttura del registro a scorrimento ... 43 44 Interponiamo tra due FF successivi un MUX, in modo da abilitare lo scorrimento (SH=1) oppure la ricircolazione del dato (SH=0). Convertitore parallelo/serie 45 • Deve consentire di introdurre dall’esterno in parallelo il dato (LOAD) e di far partire i dati di k-bit in serie alla fine del caricamento (SHIFT). Uso uno schema simile al precedente. 46 Sommatore seriale 1° addendo Risultato 2° addendo V.4. Implementazioni circuitali 47 FLIP-FLOP SR: schema a NOR Implementazione CMOS Implementazione CMOS semplificata … Problema per S=R=1 48 FLIP-FLOP SR level sensitive Implementazione CMOS La versione CMOS consente un risparmio sul numero di transistori utilizzati rispetto allo schema di partenza (2 NOR + 2 AND) 49 FLIP FLOP D level-sensitive Osserviamo che il segnale di CK ha essenzialmente funzione di ENABLE … … risulta conveniente lo schema circuitale che fa uso di Transmission Gates ! Notevole risparmio sul numero di transistori 50 FLIP FLOP D Master-Slave La soluzione a TG e’ ancora piu’ conveniente per il M/S. Negative Edge Triggered. Master Slave

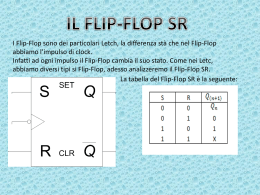

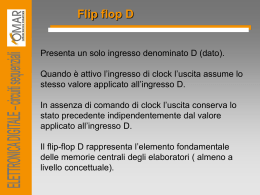

Scaricare