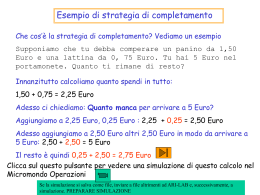

ALU 74181 Pin Descrizione !A0 - !A3 Operand inputs (active LOW) !B0 - !B3 Operand inputs (active LOW) S0 - S3 Function Select inputs M Mode Control input Cn Carry input !F0 - !F3 Function outputs (active LOW) A=B Comparator output !G Carry Generate output (active LOW) !P Carry Propagate output (active LOW) Cn+4 Carry Output Descrizione - Mode La ALU 74181 è un circuito in grado di eseguire 16 operazioni logiche e 16 operazioni aritmetiche (con o senza carry input): • M = ‘1’ i carry interni sono disabilitati e vengono eseguite le operazioni logiche di tabella • M = ‘0’ i carry interni sono abilitati e vengono eseguite le operazioni aritmetiche di tabella; inoltre si distinguono i seguenti casi: o Cn = ‘0’ il carry-in è inibito o Cn = ‘1’ il carry-in è abilitato Descrizione - Carry In modalità «aritmetica» la ALU fornisce tre carry di uscita: • Cn+4 è il classico ripple carry di uscita, calcolato in seguito all’esecuzione dell’operazione. • !P e !G sono due look-ahead carry che vengono calcolati da una logica indipendente a quella che esegue l’operazione richiesta: o !P indica che l’operazione propaga il carry-in all’esterno o !G indica che l’operazione genera un carry-out N.B. !P e !G non sono affetti dal carry in e vengono utilizzati da un’eventuale CLA (74182) nel caso si vogliano impiegare più ALU (74181) per operazioni su un maggior numero di bit Descrizione - Note generali A=B, in modalità sottrazione, indica l’equivalenza logica tra i due operandi: assume valore ‘1’, quando !F(3 - 0) = ‘1111’. Il segnale po’ inoltre essere usato insieme a Cn+4 per indicare A < B oppure A > B. La ALU opera in logica negata per quanto riguarda gli operandi, la funzione d’uscita e i carry look-ahead, come indicato dalla tabella dei pin. Le operazioni aritmetiche sono da interpretare in complemento a 2. N.B. la sottrazione viene effettuata come addizione complementare (complemento a 1): ciò significa che per ottenere l’operazione «A – B» è necessario abilitare il carry in. Tabella delle funzioni Selezione Funzione S3 S2 S1 S0 Active LOW M = ‘1’ Funzioni Logiche M = ‘0’ - Funzioni Aritmetiche Cn = ‘0’ Cn = ‘1’ 0 0 0 0 F = !A F=A–1 F=A 0 0 0 1 F = A nand B F = (A and B) – 1 F = A and B 0 0 1 0 F = !A or B F = (A and !B) – 1 F = A and !B 0 0 1 1 F=1 F = - 1 complemento a 2 = «1111» F=0 0 1 0 0 F = A nor B F = A + (A or !B) F = A + (A or !B) + 1 0 1 0 1 F = !B F = (A and B) + (A or !B) F = (A and B) + (A or !B) + 1 0 1 1 0 F = A xnor B F=A–B–1 F=A–B 0 1 1 1 F = A or !B F = A or !B F = (A or !B) + 1 1 0 0 0 F = !A and B F = A + (A or B) F = A + (A or B) + 1 1 0 0 1 F = A xor B F=A+B F=A+B+1 1 0 1 0 F=B F = (A and !B) + (A or B) F = (A and !B) + (A or B) + 1 1 0 1 1 F = A or B F = A or B F = (A or B) + 1 1 1 0 0 F=0 F=A+A F=A+A+1 1 1 0 1 F = A and !B F = (A and B) + A F = (A and B) + A + 1 1 1 1 0 F = A and B F = (A and !B) + A F = (A and !B) + A + 1 1 1 1 1 F=A F=A F=A+1 N.B. i simboli «+» e «-» indicano operazioni aritmetiche VDHL - Introduzione N.B. A causa della lunghezza del sorgente, nelle slide seguenti verrà presentata soltanto la struttura «portante» che descrive la rete, tralasciando quelle parti «modulari» se si presentano ripetutamente all’interno del codice. La Architecture è costituita da un Process all’interno del quale vengono definite le variabili (associate ai pin) utilizzate all’interno degli Statements; il funzionamento della rete viene descritto con una struttura basata su costrutti if-the-elsif-else innestati: un primo costrutto discrimina la modalità di funzionamento; per M=‘0’ un secondo costrutto separa i casi con carry-in abilitato oppure no. Per ognuno di questi 3 casi vengono elencate, sempre mediante if-then-elsif-else, le 16 possibili funzioni. Il ripple carry viene valutato dalle stesse espressioni per la funzione d’uscita; al contrario i look-ahead carry vengono gestiti, per ogni operazione aritmetica, da Statements indipendenti. Il valore di A=B è invece valutato soltanto in caso di sottrazioni da un ulteriore Statement if-then-else, mentre in tutti gli altri casi è posto a ‘0’ di default. Simulazioni Di seguito vengono riportate le simulazioni della ALU: ogni possibile funzione viene testata sia in modalità Behavioral per valutare il corretto funzionamento logico, sia in modalità Post-Route per evidenziare eventuali ritardi. Per tutti i test verranno utilizzati i seguenti valori per gli operandi: • A = «0101» • B = «1100» N.B. da ricordare che A, B, F e gli altri pin indicati nella tabella iniziale sono da valutare in logica negata(Active LOW). Ogni simulazione verifica le 16 funzioni previste in una determinata modalità operazionale: logica, aritmetica senza carry-in, aritmetica con carry-in. Simulazione Behavioral – M=‘1’ Simulazione Post-Route – M=‘1’ Simulazione Behavioral – M=‘0’, Cn=‘0’ Simulazione Post-Route – M=‘0’, Cn=‘0’ Simulazione Behavioral – M=‘0’, Cn=‘1’ Simulazione Post-Route – M=‘0’, Cn=‘1’ Analisi dei ritardi Come anticipato precedentemente, le simulazioni Post-Route evidenziano dei ritardi sulle uscite: • ‘AcB’ (‘A=B’) subisce un ritardo di 9 ns • ‘P’ e ‘G’ vengono ritardati di 10 ns • ‘F(3-0)’ presenta un ritardo che oscilla tra i 12 e 14 ns: in questo caso tale periodo si può considerare di «stabilizzazione» in quanto all’interno di esso la rete assume valori non predicibili causati da glitches. • ‘Cn4’ (‘Cn+4’) risulta contemporaneo ad ‘F(3-0)’, dunque ritardato anch’esso di 12-14 ns Tale andamento è giustificato dall’indipendenza di certi «blocchi» della rete: anche osservando il VHDL è possibile prevedere uno sfalsamento delle uscite in base alla complessità del codice che le gestisce.

Scaricare