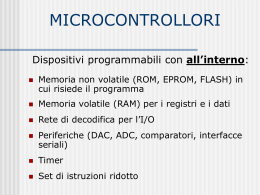

Moka Programmabile Rete sequenziale sincrona per la gestione di una moka programmabile. SCHEMATICO Segnali - lista INPUT SET_CLOCK SET_TIMER SWITCH_HMS UP PRESS CK OUTPUT SECONDS(7:0) MINUTES(7:0) HOURS(7:0) TIMERS(7:0) TIMERM(7:0) TIMERH(7:0) ERROR HEAT Segnali - descrizione INPUT SET_CLOCK: finché il suo valore logico è '1', da la possibilità di impostare l'orario corrente all'interno della moka mediante il pulsante di selezione SWITCH_HMS e il pulsante UP. SET_TIMER: finché il suo valore logico è '1', da la possibilità di impostare l'orario del timer (l'orario in cui fare il caffè), anch'esso utilizza i pulsanti SWITCH_HMS e UP. SWITCH_HMS: permette di spostare la selezione del “campo” (Hours, Minutes, Seconds) da aggiornare. Il cambiamento di “campo” si ha al rilascio del bottone. UP: permette (al rilascio) di aumentare di 1 il valore del “campo” attualmente selezionato. PRESS: quando il suo valore logico è '1', indica che la moka è presente sulla piastra. OUTPUT SECONDS(7:0): secondi dell'orologio reale. MINUTES(7:0): minuti dell'orologio reale. HOURS(7:0): ore dell'orologio reale. TimerS(7:0): secondi in cui la moka dovrà partire TimerM(7:0): minuti in cui la moka dovrà partire TimerH(7:0): ora in cui la moka dovrà partire CK: segnale di clock. Che per un corretto funzionamento dell'orologio deve essere alla frequenza di 100 Hz. ERROR: il suo valore logico va a '1' se durante le fasi di SET_CLOCK/SET_TIMER si è ecceduto il limite per un campo (23 per le ore, 59 per minuti e secondi). HEAT: il suo valore logico va a '1' quando l'orario corrente diventa l'orario impostato nel timer e permane ad 1 finché il caffè non è pronto (cioè, per 10 minuti). Schematico - introduzione Schematico - moduli Come si può notare dallo schematico nella slide precedente, la rete sequenziale sincrona della moka è stata realizzata mediante l'ausilio di componenti integrati Xilinx© e di due componenti creati appositamente: DigitalClockChecker DigitalClock DigitalClockChecker DigitalClock DigitalClock - descrizione E’ il componente che è incaricato di scandire il tempo correttamente. Quindi è un vero e proprio orologio digitale funzionante con un clock di 100 Hz (ingresso CK). E’ stato realizzato mediante contatori e decodificatori. Per ovviare ad alcuni problemi causati dal reset ASINCRONO di alcuni componenti integrati xilinx (i contatori su 8 bit, con LOAD), sono stati inseriti FFD per dare l’impulso di clear nell’istante corretto. Il componente è dotato di un ingresso CE che abilita il conteggio se il suo valore logico è ‘1’. E’ possibile far partire il conteggio dell’orario dall’ora desiderata mediante i bus di ingresso e l’ingresso SET. Come si può notare, non si fanno controlli sulla correttezza dei dati inseriti. E’ per questo motivo che questo componente dev’essere utilizzato assieme a DigitalClockChecker. Simulazioni - introduzione I due componenti realizzati come moduli della moka hanno a disposizione i loro testbench «testb – behavioral» per il componente «DigitalClock». Nome del testbench VHDL : «DigitalClockTest.vhd» «DigitalClockChecker_ DigitalClockChecker_sch_tb – behavioral» per il componente «DigitalClockChecker». Nome del testbench VHDL: «CheckerTestBench.vhd» Questi testbenches, però, non mostreranno alcun risultato in iSim a meno ché non si rimuova dalle proprietà di iSim l’utilizzo del file delle forme d’onda alternativo. Questo file è stato creato per la moka nel suo complesso, per questo motivo L’UNICO testbench che partirà senza alcun problema è «MokaSchematic_ MokaSchematic_tb – behavioural», che è il test per il quale iSim è stato configurato. Il funzionamento di quest’ultimo testbench implica il funzinamento dei due precedenti (visto l’uso dei componenti all’interno della moka). Simulazione – Panoramica globale Si può notare come la piastra HEAT si accenda per 10 minuti. Nelle prossime slides si analizzerà nel dettaglio l’impostazione dell’orario (quindi test del componente DigitalClockChecker), dello scorrere del tempo (quindi componente DigitalClock) e si mostrerà che la piastra si è accesa all’orario prestabilito. Simulazione – impostazione orario Il segnale SET_CLOCK è attivo mentre il segnale SET_TIMER è attivo (come da vincoli, si immagina che fisicamente l’attivazione dei due pulsanti in contemporanea sia impossibile). Alla pressione del tasto UP ciò che è stato selezionato mediante SWITCH_HMS viene incrementato di 1. Si può notare come il tempo di pressione sia di UP, che di SWITCH_HMS, non sia rilevante (Le onde create con UP sono tutte uguali solo perché a livello di codice, sono state generate mediante un ciclo for). Sono state impostate come orario attuale le 12:05. Simulazione – impostazione timer (ora per fare il caffè) I vincoli sono quelli della slide precedente, e anche il funzionamento. Ora è attivo l’ingresso SET_TIMER, così facendo viene impostata l’ora del timer. Sono state impostate le 12:10. Quindi, tra 5 minuti esatti la piastra HEAT dovrà andare a 1 e rimanere tale per 10 minuti. Giusto il tempo di fare il caffè. Simulazione – l’ora del caffè Nell’istante in cui le ore ed i minuti si eguagliano (da notare in quest’immagine il cambio di minuto da 9 a 10) con quelli del timer, il segnale HEAT va ad 1. E come si può notare dalla slide «Simulazione – panoramica globale», dura esattamente 10 minuti d’orologio. Simulazione – trascorsa un’ora A verifica del funzionamento del componente DigitalClock, si può notare come allo trascorrere dell 59-esimo secondo del 59-esimo minuto, l’orario passi dalle 12 alle 13. Il numero di secondi trascorsi nella simulazione non è 3600 dato che l’orario iniziale non erano le 12:00 ma le 12:05, quindi 3600 – (5*60) = 3600 – 300 = 3300. Il secondo di scarto è dato dal tempo impiegato nella simulazione per impostare l’orario. Le simulazioni presenti sono tutte behavioral, quindi non tengono conto dei ritardi Instrinsici della tecnologia usata. Simulazione – post route Della simulazione post route mostrerò semplicemente il confronto tra le due immagini «globali» della simulazione, così da evidenziare le differenze. La simulazione post route è state eseguita per soli 1600 secondi, in quanto il tempo di simulazione sarebbe risultato eccessivo. Simulazione - confronto Behavioral: Post Route: Simulazione - differenze La differenza più evidente è che nella simulazione post route il cambio tra un minuto e l’altro non è immediato. Si generano delle forme d’onda «rapide» di transizione tra un valore e l’altro, anziché essere «pulite» come nella simulazione behavioral. Ulteriori differenze non sono visibili dalle immagini, non solo per il fatto che essendo immagini globali sono poco dettagliate, ma soprattutto perché l’uso di un segnale di clock a 100Hz («lento») minimizza le differenze, in quanto la rete ha tempo di stabilizzarsi tra due fronti positivi, evitando così casi di meta-stabilità.

Scaricare