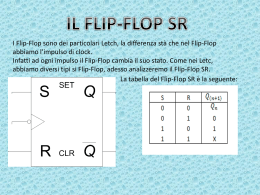

CIRCUITI SEQUENZIALI Corso di recupero di Fondamenti di Elettronica – Università di Palermo A.A. 2014-2015 Reti sequenziali rete × asincrona sincronismo Sincronismo level triggered PET edge triggered NET Latch SR Latch a porte NOR •S=R=0 • Qn = 1 0 Qn 1 R Qn 1 0 10 0 1 Qnn11 S Qn 0 10 01 Latch a porte NOR • S = 0, R = 1 Qn 1 Qn R 1 0 Qn1 S Qn 0 0 1 Latch a porte NOR • S = 1, R = 0 Qn 1 Qn 1 R 0 0 1 Qn1 S Qn 1 0 Latch a porte NOR •S=R=1 1 0 1 0 Latch a porte NOR Latch con abilitazione “gating” o “strobe” Interruttore anti-rimbalzo S = 1, R = 0 S = 0, R = 0 S = 0, R = 1 1 Q=0 Flip-flop Multivibratori bistabili edge-triggered pulse-triggered (master-slave) SR, D, JK, T Flip-flop SR latch SR di tipo sincrono × 0 0 × 0 Flip-flop PET Flip-flop PET Flip-flop Master-Slave Flip-flop con ingressi di preassegnazione Flip-flop JK Flip-flop JK Flip-flop D Flip-flop T (toggle) Flip-flop integrati Registri a scorrimento A C D B Registri SISO e SIPO Registri PIPO e PISO parallel enable Registro universale 74194 caricamento vs. destra caricamento parallelo caricamento vs. sinistra clock inibito up/down Contatori sincroni e asincroni con caricamento (LOAD) divisori di frequenza binari e non Contatori asincroni divisori di frequenza (per n 2) TCK ≥ n∙tp Q Ck T 1 Contatore binario indietro Contatore asincrono non binario (modulo 5) spike Contatori sincroni clock applicato simultaneamente a tutti i flip-flop i bit di uscita commutano contemporaneamente la massima frequenza di funzionamento aumenta assenza di spike indesiderati Contatore sincrono (modulo 8) T1 = 1 T3 = Q1∙ Q2 T2 = Q1 (n – 2) porte AND Per n bit TCK ≥ (n - 2) ∙ tp2 + tpl AND f max F.F. 1 1 TCK n 2 t p 2 t p1 Contatori sincroni: propagazione del comando in serie in parallelo f max 1 t p 2 t p1 Contatori integrati: 7490 a s i n c r o n o Contatori integrati: 7492 e 7493

Scaricare