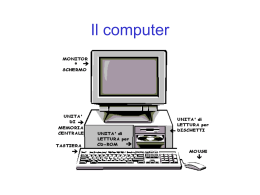

Calcolatori Elettronici Cenni sulle memorie Francesco Lo Presti Rielaborate da Salvatore Tucci Clocking Il segnale di Clock definisce quando i segnali possono essere letti e quando possono essere scritti Fronte di discesa (negativo) Falling edge Periodo di clock Fronte di salita (positivo) Rising edge Freq. clock = 1/(Periodo di Clock) e.g., Periodo di 10 nsec 100 MHz Periodo di 1 nsec 1 GHz Opzioni per gli elementi di memoria Latch sensibili al livello Flip-Flop master-slave/edge-triggered Memoria 1 Elementi di Memoria Latch Set-reset R S Q !Q Latch D sensibile al livello clock Q R S Q(t+1) !Q(t+1) 1 0 0 1 0 1 1 0 0 0 Q(t) !Q(t) 1 1 - - D clock !Q D Q Il latch e’ transparente quando il clock e’ alto (l’ingresso e’ copiato in uscita) Memoria 2 Periodo del Ciclo di Clock T Il periodo T deve essere scelto lungo abbastanza da garantire che l’output della rete combinatoria sia stabilizzato Deve esserlo prima del periodo di apertura di del flip-flop (set-up time) Deve rimanere stabile per un certo tempo (hold-time) Determina il limite superiore alla frequenza di clock Memoria 3 Elementi di Memoria Problemi con i latch: corse critiche … Elemento di Memoria Logica Combinatoria Elementi di memoria usati come input ed output nello stesso ciclo Il clock deve rimanere ad 1 per un tempo sufficiente da garantire che l’ingresso sia memorizzato …ma tale da non permettere il propagarsi del nuovo valore attraverso la rete combinatoria Difficile garantire entrambe le condizioni Dipende dai tempi di propagazione e dalla presenza di diversi percorsi attraverso la rete combinatoria Memoria 4 Elementi di Memoria Soluzione: Flip-Flops che cambiano lo stato (Q) solo sui fronti del segnale di clock (master-slave) D D D Q D-latch clock clock !Q D Q Q !Q !Q D-latch clock clock Q Master (primo D-latch) copia in Q l’ingresso quando il clock e’ alto (lo slave (secondo D-latch) e’ bloccato e non cambia stato ) Slave copia il valore del master quando il clock va a 0 (il master e’ bloccato nel suo stato di memoria ed eventuali cambi all’ingresso non vengono letti) D Set-up time C Hold time Setup e hold time per un flip-flop D Memoria 5 Assunzioni Metodologia edge-triggered Comportamento tipico Leggere il contenuto di elementi di memoria I valori sono input di una o piu’ reti combinatorie Scrivere i risultati in uno o piu’ elementi di memoria State element 1 Combinational logic State element 2 clock one clock cycle Si assume che gli elementi di memoria siano scritti ad ogni ciclo di clock Altrimenti si aggiunge un esplicito segnale di write In AND con il clock La scrittura avviene solo quando occorre la transizione di Memoria livello attiva ed il segnale di controllo e’ affermato 6 Registro Registro Simile ad un flip flop D eccetto n bit di ingresso e uscita Input Write D0 clock D1 Write: Se negato (0): i dati in uscita (Data Out) non cambiano Se affermato (1): i dati in uscita (Data Out) divengono uguali ai dati in ingresso (Data In) D Q Flip-FlopD Dn-1 Q1 !Q D Q Flip-FlopD clock clock !Q D Q Flip-FlopD clock Q0 Qn-1 !Q Write Memoria 7 Banco di registri (register file) Banco di registri ad accesso rapido per memorizzare temporaneamente gli operandi usati nelle istruzioni Nel MIPS il banco dei registri è composto da 32 registri generali Due porte in lettura da 32 bit Read data 1/2 Una porta in scrittura da 32 bit Write data Tre porte per selezionare i registri da 5 bit Read register #1 (#2) : primo (secondo) registro da leggere Write register: registro da scrivere Write: segnale di controllo In AND con il clock (non mostrato) Solo se Write=1 il valore in Write data e’ scritto nel registro indicato da Write Reg. Memoria 8 Banco di registri (2) Un banco di registri può essere implementato con un multiplexer per ciascuna porta read, un decoder per ciascuna porta write ed un array di registri costruiti partendo da flipflop D Esempio: implementazione di due porte read per un banco di registri composto da n registri Read register number 1 Register 0 Register 1 Register n – 1 M u x Read data 1 M u x Read data 2 Register n Read register number 2 Memoria 9 Banco di registri (3) Esempio: implementazione di una porta write per un banco di registri composto da n registri Log2n to n Memoria 10 Principali tecnologie per RAM Le memorie RAM sono di due tipi Memorie statiche: Static Random Access Memory (SRAM) Memorie dinamiche: Dynamic Random Access Memory (DRAM) Memorie statiche Il singolo elemento corrisponde ad un latch Memorie dinamiche Il singolo elemento corrisponde ad un condensatore ed un transistor L’informazione è memorizzata sotto forma di carica del condensatore Richiedono un refresh periodico dell’informazione Le memorie statiche sono (rispetto a quelle dinamiche) Più veloci (5ns vs. 50-100ns) Più costose (6 transistor per bit) Persistenti (non è richiesto il refresh) Più affidabili Memoria 11 Memoria Principale, Cache e Tecnologie Prestazioni della memoria principale Latenza Tempo di accesso: tempo tra quando arriva la richiesta e la parola Tempo di ciclo: tempo tra richieste Banda La memoria principale è DRAM Dinamica in quanto ha bisogno di essere rinfrescata periodicamente (8 ms) La memoria cache usa SRAM No refresh (6 transistor/bit vs. 1 transistor) Dimensione: SRAM/DRAM = 4-8 Costo/Tempo di Ciclo: SRAM/DRAM = 8-16 Memoria 12 Obiettivo: Illusione di una Memoria Grande, Veloce ed Economica Osservazioni: Le memorie di grandi dimensioni sono lente Le memorie veloci hanno dimensioni piccole Come creare una memoria che sia grande, economica e veloce (per la maggior parte del tempo)? Gerarchia Parallelismo Memoria 13 Gerarchia di memoria La memoria di un calcolatore è implementata come una gerarchia di memorie Differenti tempi di accesso e di costo corrispondenti ai diversi livelli di memoria CPU Aumenta il tempo di accesso Aumenta la capacità di memorizzazione Diminuisce il costo per bit Livello 1 Livello 2 . . . Livello n Dimensione della memoria ad ogni livello Memoria 14 Gerarchia di memoria (2) Obiettivi della gerarchia di memoria: Fornire all’utente una quantità di memoria pari a quella disponibile nella tecnologia più economica Fornire una velocità di accesso pari a quella garantita dalla tecnologia più veloce Processor Control On-Chip Cache Registers Datapath Second Level Cache (SRAM) Main Memory (DRAM) Speed (ns): 1 10 100 Size (bytes): 100 K M Secondary Storage (Disk) 10,000,000 (10 ms) G Tertiary Storage (Tape) 10,000,000,000 (10 sec) T Memoria 15 Gerarchia di memoria: Esempio del Pentium Memoria 16 Memoria Cache La memoria principale (DRAM) è sempre più lenta del processore e tende a rallentarlo Sono disponibili memorie più veloci (SRAM) ma solo per dimensioni limitate La cache opera alla velocità del processore, e quindi nasconde la “lentezza” della memoria Scopo della cache: disaccoppiare le velocità di processore e RAM Contiene le ultime porzioni di memoria acceduta: se il processore richiede l’accesso ad una di esse evita un accesso alla memoria Funziona bene sfruttando il principio di località dei riferimenti Memoria 17 Strategia di Utilizzo della Cache La prima volta che il processore richiede dei dati si ha un cache miss I dati vengono caricati dalla memoria principale e vengono copiati anche nella cache Si legge un blocco di parole contigue Le volte successive, quando il processore richiede l’accesso ad una cella di memoria Se il dato è presente in un blocco contenuto nella cache, la richiesta ha successo ed il dato viene passato direttamente al processore Si verifica un cache hit Altrimenti la richiesta fallisce ed il blocco contenente il dato viene anche caricato nella cache e passato al processore Si verifica un cache miss Obiettivo: aumentare quanto più possibile il tasso di cache hit Memoria 18 Principio di località Osservazione: i programmi accedono ad una porzione relativamente piccola del loro spazio di indirizzamento Esistono due tipi differenti di località 1. Località temporale (nel tempo): se un elemento (dato o istruzione) è stato acceduto, tenderà ad essere acceduto nuovamente in un tempo ravvicinato 2. Località spaziale (nello spazio): se un elemento (dato o istruzione) è stato acceduto, gli elementi i cui indirizzi sono vicini tenderanno ad essere acceduti in un tempo ravvicinato Esempio I programmi contengono cicli: le istruzioni ed i dati saranno acceduti ripetutamente (località temporale) Gli accessi agli elementi di un array presentano un’elevata località spaziale; nell’esecuzione di un programma è altamente probabile che la prossima istruzione sia contigua a quella in esecuzione Probabilità di riferimento 0 n-1 2 Spazio di indirizzamento Memoria 19 Principio di località (2) Come sfruttare la: 1. Località temporale Tenendo gli elementi acceduti più frequentemente vicino al processore 2. Località spaziale Spostando blocchi contigui di parole al livello superiore Memoria 20

Scaricare