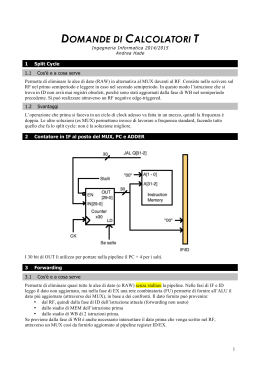

INPUT / OUTPUT Connessione tra componenti Tastiera Mouse Stampante BUS CPU Monitor Dischi RAM = Interfacce o Controller Interfaccia di I/O Linea indirizzi Linea dati Linea controllo Decoder indirizzi Circuiti controllo Dispositivo Registo dati E stato Interrupt Meccanismo che avvisa il processore della disponibilità del Dispositivo di I/O ad eseguire una operazione. Quando il dispositivo è pronto invia alla CPU un segnale di Interrupt La CPU interrompe l’operazione corrente ed esegue una routine di servizio dell’interrupt La CPU informa il dispositivo che la richiesta di interrupt è stata Accolta con un segnale di riscontro (Interrupt Acknowledge) La routine di gestione dell’interrupt salva lo stato della CPU (latenza) Interrupt Gli interrupt modificano la sequenza temporale prevista dal programmatore per cui è fornito un meccanismo di Abilitazione e Disabilitazione degli Interrupt. Soluzione 1: La routine di gestione dell’interrupt come prima Istruzione disabilita gli interrupt e li riabilita alla fine Soluzione 2: Il processore automaticamente quando riceve un interrupt li disabilita e li riabilita quando Torna dalla routine di gestione dell’interrupt. Soluzione 3: Interrupt EDGE-TRIGGERED Gestione di più dispositivi Come fa la CPU a capire da quale dispositivo riceve l’Interrupt? Come fa la CPU a determinare qual è la procedura di gestione dell’interrupt per lo specifico dispositivo? Un dispositivo può interrompere la CPU mentre questa sta servendo un altro interrupt? Come può gestire la CPU due richieste di interrupt contemporanee? Gestione di più dispositivi Come fa la CPU a capire da quale dispositivo riceve l’Interrupt? CPU INTR INTR1 INTR2 INTR3 La CPU fa il “POLLING” dei dispositivi per verificare quale IRQ è abilitato. Gestione di più dispositivi Oltre al segnale di interrupt il dispositivo invia sul bus alla CPU un proprio codice identificativo che può essere utilizzato per Identificare la routine specifica di gestione dell’interrupt (vettore di interrupt) Gestione di più dispositivi Un dispositivo può interrompere la CPU mentre questa sta servendo un altro interrupt? Problema delle Priorità CPU Dispositivo 1 Circuito Arbitraggio Priorità Dispositivo 2 Dispositivo 3 Gestione di più dispositivi Come può gestire la CPU due richieste di interrupt contemporanee? CPU Dispositivo 1 Dispositivo 2 Dispositivo 3 Gestione di più dispositivi Come può gestire la CPU due richieste di interrupt contemporanee? CPU Circuito Arbitraggio Priorità Dispositivo 1 Dispositivo 2 Dispositivo 3 Dispositivo 4 Dispositivo 5 Dispositivo 6 Interrupt Software (TRAP) Richieste dal programma utente al Sistema Operativo Direct Memory Access (DMA) Capacità di trasferire grosse quantità di dati Senza l’intervento della CPU Il trasferimento in DMA è effettuato da un apposito Circuito di controllo del dispositivo detto Controllore DMA La CPU inizializza il trasferimento e lascia al controllore DMA il compito del trasferimento. Alla fine la CPU Viene informata da un’interrupt. Arbitraggio del BUS Poiché il BUS è unico più dispositivi possono richiedere Di effettuare un trasferimento DMA Soluzione 1: Arbitraggio Centralizzato La CPU decide qual è il dispositivo che deve operare. Tale dispositivo diventa BUS MASTER Soluzione 2: Arbitraggio Distribuito Ogni dispositivo che deve effettuare il DMA Pone un codice su 4 linee di controllo. Il vincitore Viene selezionato in base al risultato dell’interazione Tra i segnali trasmessi su tali linee da tutti i contendenti Realizzazioni Hardware Bus sincroni ed asincroni Bus VME Bus ISA Bus PCI, PCI64, PCI-X Bus SCSI Bus IDE, EIDE, ATA, Serial ATA Interfaccia Parallela Interfaccia Seriale (RS232) Interfaccia di Rete

Scaricare