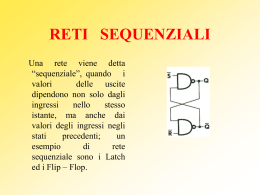

Flip-flop e Registri Flip-flop S-R (Set-Reset) o bistabile (macchina asincrona) R 1 Tabella verità NOR 0 Y1 1 R =1 S =0 0 S 1 0 R 0 Y2 1 Y1 0 R =0 S =1 1 S 1 0 Y2 B A 0 1 0 1 0 A 1 0 0 B •Se un ingresso è uguale ad 1 allora l’uscita vale 0 •Se un ingresso è uguale a 0 allora l’uscita è uguale al valore dell’altro ingresso negato Bistabile (cont.) il termine bistabile nasce dal fatto che sono “circuiti” con due stati stabili R 0 0 Y1 1 R =0 S =0 0 S 1 0 R 0 Y2 1 Y1 0 R =0 S =0 1 S 0 0 Y2 Equazioni bistabile Q S R Q Q S • Q’ prossimo stato R Q’ 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 d.c.c. 1 0 0 1 1 0 1 0 1 1 0 1 1 1 1 d.c.c. Q SR 00 01 11 0 0 0 x 1 1 1 0 x 1 Q’ = S+ RQ 10 Caratteristiche La configurazione di ingresso S=R=1 non è ammessa, poiché se da questa si passa a S=R=0 sono possibili due configurazioni per l’uscita. La configurazione effettiva non è cioè prevedibile R S Q Q Hold Reset Set SR 0 0 0 1 1 0 1 1 Q’ Q 0 1 ? Con S=R=0 il bistabile mantiene (hold) lo stato acquisito in precedenza (Q’=Q) Questa rete è cioè in grado di memorizzare una informazione elementare (bit) Segnale di sincronizzazione • • Un segnale di sincronizzazione è una variabile binaria che viene utilizzata per abilitare la commutazione di un flip-flop (sincronizzato) L’abilitazione alla commutazione può essere fatta: – all’istante in cui avviene la commutazione della variabile da 0 ad 1 (fronte di salita); – All’istante in cui avviene la commutazione della variabile da 1 a 0 (fronte di discesa) – Nel periodo in cui è stabile ad 1 oppure a 0 (a livello) Fronte di discesa 1 0 Fronte di salita •nella realtà le transizioni 0->1 e 1->0 non sono istantanee Segnale di sincronizzazione (cont.) •Alcune volte il segnale di abilitazione per la commutazione può avere un comportamento periodico (periodo T), in questi casi viene chiamato anche clock (CK) •Spesso il segnale di abilitazione per la commutazione viene identificato con CK anche se non ha un comportamento periodico Fronte di discesa 1 0 Fronte di salita Periodo T Flip-flop (bistabili) sincronizzati • • Sono ottenuti dai bistabili asincroni aggiungendo un segnale di controllo CK Abilitazione sul livello (Level-triggered), chiamati Latch • Abilitazione sul fronte di salita (positive edge triggered) • Abilitazione sul fronte di discesa (negative edge triggered) • Master-Slave – L’uscita può cambiare durante tutto il periodo in cui CK=1 o 0. – L’ingresso viene considerato solo quando CK varia da 0 ad 1 e lo stato può cambiare in corrispondenza di tale transizione – L’ingresso viene considerato solo quando CK varia da 1 a 0 e lo stato può cambiare in corrispondenza di tale transizione – L’ingresso viene considerato solo quando CK varia da 0 ad 1, mentre l’uscita cambia in corrispondenza della transizione 1->0 – Eventuali cambiamenti dell’ingresso dopo la transizione 0->1 sono ignorati dal circuito Esempio, Latch S-R R Q CK Q S R Q CK S Q CK S R Q’ 0 0 0 Q 0 0 1 Q 0 1 0 Q 0 1 1 ? 1 0 0 Q 1 0 1 0 1 1 0 1 1 1 1 ? Quando CK=1 allora si ha il consenso alla transizione Perché abilitare sui fronti? • • • Sia d il tempo in cui CK=1 e t il tempo di commutazione del FF Si supponga che d>t L’uscita può cambiare più volte se l‘ingresso varia e questo in alcuni casi può creare problemi CK S Q1 S FF1 R CK Q2 R FF2 Q1 t Ritardo di propagazione Abilitazione sul fronte Usando FF con abilitazione sul fronte (di salita o di discesa) si campiona il valore delle altre variabili di ingresso in un intervallo più ristretto (teoricamente di ampiezza nulla). CK S R CK Q1 Q2 S R Q1 t Ritardo di propagazione Campionamento sul fronte di salita Flip/flop D (delay) latch • Un solo ingresso più uno di abilitazione • Usato come unità elementare di memorizzazione – Presenta in uscita ciò che è presente in ingresso quando il CK = 1, altrimenti presenta l’ultimo valore di D quando il CK commuta da 1 a 0. D R Q Q CK Q CK D CK D S Q Master-Slave . L’ingresso viene campionato durante il fronte di salita, l’uscita commuta in corrispondenza del fronte di discesa. Master R CK S R Q CK S Slave R Q CK Q S Q Registri • Un registro è un elemento di memoria – in grado di memorizzare un insieme di n bit – composto da un insieme di flip-flop – l’informazione memorizzata in un registro prende il nome di parola (se 8 bit si identifica anche come byte) bit in ingresso bit in uscita Registri • Modalità di scrittura/lettura dei dati – Parallelo – Seriale • Operazioni sui dati: – Scorrimento a destra – Scorrimento a sinistra – Scorrimento circolare Registro parallelo-parallelo D0 D2 D1 D Q D Q D3 D Q D Q Clock Q0 Q1 Q2 Q3 Shift register D CLOCK D Q D Q D Q D Q Q Registro circolare (n=4) D0 D2 D1 D3 Write/Shift Scrivi/Scorri D Clock Q D Q D Q D Q Q

Scaricare