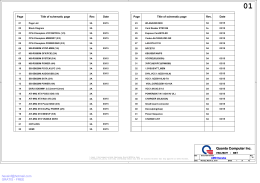

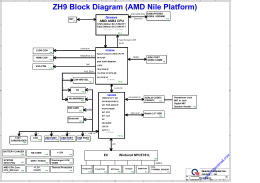

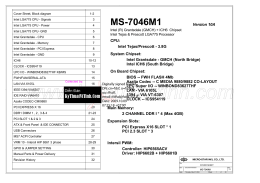

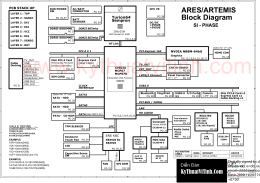

5 4 3 2 Title D MS-9620-0A C B A 1 Page Cover Sheet 1 Block Diagram 2 POWER DELIVER 3 CPU 0 940 PIN 4-7 System Memory / DDR Terminations 8-11 CPU1 940 PIN 12-15 CK8-04 PRO 16-21 PCI1 & CPUCLOCK BUFFER 22 PCI-Express *16 and *1 23 PCIE-*4 SLOT 24 PCI-Express *8 and NV-SLI 24 Rear USB Port 26 BCM 5705 GbLAN 27 FAN 28 88E1111CAA LAN 29 Front USB Port 30 AC97 ACL850 31 ATX connector / Front Panel KB/MS/LPT/COM Port 32 39 SYSTEM CLOCK BLOCK DIAGRAM W627THF LPC I/O / BIOS 33 40 VIA 6306 1394 34 SYSTEM RESET BLOCK DIAGRAM 41 IDE CONNECTOR 35 SYSTEM SMBUS BLOCK DIAGRAM 42 MS-6 ACPI Controller & MS-6+ 36 VRM1 ISL 6566 37 DDR ROUTING BLOCK DIAGRAM 43 GENERAL SPEC 44 5 4 VRM0 ISL 6566 3 http://laptop-motherboard-schematic.blogspot.com/ 38 2 D C B A Micro Star Restricted Secret Title Document Number Cover Sheet MS- 9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw R ev 0A Last Revision Date: Tuesday, January 25, 2005 Sheet 1 44 of 1 5 4 3 2 1 Block Diagram AMD K8 Socket 940 D DDR400 AMD K8 Socket 940 CPU 1 D CPU 0 HT(8GB/s) HT(8GB/s) PCIE_X8 DDR * 6 PCIE_X8 PCIE_X4 PCIE _X20LANE C 1 PCI Slots C IDE Slot ==>ATA66,100,133 *2 Dual ATA 100/133 PC I-33 CK8-04 B AC97 => S/W Audio ALC850 8 CHANEL Giga Bit LAN BCM5705 VIA 6306 1394-->2 PORT B LPC BUS AC97 SERIAL ATA *4 USB RGMII SUPER I/O W83627HF FWH A A Dual USB 1.1 OHCI /2.0 EHCI 8 Ports ==> Front-Port *6, Back-Port *4 88E1111 PHY GIGA BIT LAN 4 3 Block Di agram Document Number http://laptop-motherboard-schematic.blogspot.com/ 5 Micro Star Restricted Secret Title MS- 9620 MICRO-STAR INT'L CO.,LTD. N o. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 2 1 Rev 0A Last R evision Date: W ed nesday, February 02, 2005 Sheet of 2 44 5 4 3 2 1 MS-9620 POWER DELIEVERY DIAGRAM 24A 19.8A D 25A P12V_CPU 160A 80A VRD10.1 P41 5VDUAL 5VSB Linear Reg P41 0.715A+? 0.107A EFF 80% BIOS (Note 3) 20 0mA 0.3A P32 VCC_25 ANALOG 80A Keyboard & Mouse CK-804 P41 CPU1 0.465A+? 60mA 3VDUAL P13 3.0A PCI Express X16 USB*10 P41 P37 P38 D 50mA 25 0mA VTT_DDR Linear Reg 28.3A+?A P13 Switch Reg P37 1.5A VCC2_5_DDR VCC3 CPU0 1V5_DUAL CK-804 Linear Reg P41 P23 7.5A +12V Fan*5 19.245A+?A 30mA 95.4mA 1394 P37 BCM5705 P29 2.8A 37 5mA PCI1 (Note 4) 1.9A PCI1 1.5A PCI Express X4 PCI1 P28 4 5mA+? P5V_AUD ALC850 Linear Reg C C P28 4.4A PCI Express X16 40 0mA 3VDUAL BCM5705 P41 37 5mA 1.5A (Note 4) PCI Express X4 45 0mA 3A 1.5A PWR1394 PCI1 88E1111PHY J1394CON1 Power Isolation 12 0mA 1V5_DUAL CK-804 Linear Reg 30 0mA 1V2_VDDA CK-804 Linear Reg B B 37 1mA CK-804 5.5A VCC5 5.5A 5VDUAL 16.396A+?A P37 (Note 3) USB*10 P41 8.3A V_1P5_CORE CK-804 Switch 8.3A P41 95.4mA 1394 P29 A A 2.5A PCI1 Micro-Star Int'l Co., Ltd. P27 P28 No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw Title http://laptop-motherboard-schematic.blogspot.com/ Power Delivery Block Diagram Size Document Number Custom MS-9620 Date: 5 4 3 2 Tuesday, January 25, 2005 R ev 0A Sheet 1 3 of 44 5 4 3 2 VTT_DDR VTT_DDR AC19 AE19 J19 H19 F20 G19 AE18 AC18 F21 AF18 HT0 is for SH0 & Golem connection C2052 C2542 C2560 VTT_DDR 4.7u/0805 0.22u/16V/X7R 1000P/50V/X7R R2089 SOLDER SIDE X_51 VDD_12_A D C2554 C2545 0.22u/16V/X7R 1000P/50V/X7R SOLDER SIDE U2006E K10 J11 H10 H8 K14 J15 K16 J16 J9 E14 E13 C15 D15 E16 E15 C17 D17 C19 D19 E20 E19 C21 D21 E22 E21 C14 B14 A16 A15 C16 B16 A18 A17 A20 A19 C20 B20 A22 A21 C22 B22 C VC C _ DDR A14 A13 C13 D13 R2083 R2082 closed to AF22 pin L1_CLKIN_H(1) L1_CLKIN_L(1) L1_CLKIN_H(0) L1_CLKIN_L(0) L1_CLKOUT_H(1) L1_CLKOUT_L(1) L1_CLKOUT_H(0) L1_CLKOUT_L(0) L1_CTLIN_H(0) L1_CTLIN_L(0) L1_CTLOUT_H(0) L1_CTLOUT_L(0) L1_RSVD1 L1_RSVD2 <11> H0_MD[127..64] D7 C7 A7 A8 B12 C12 L1_RSVD3 L1_RSVD4 E11 E12 TP2002 TP2003 closed to F22 pin H 0_VREF0_DDR C2175 R2077 100RST C2174 0.1u 0.1u C2094 C2176 1000P/50V/X7R 0.1u C2095 1000P/50V/X7R <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> VC C _ DDR R2027 X_1K <17> MEM_GPIO1 R2028 VC C _ DDR X_0 R2026 U2003 1 X_100K 2 VC C _ DDR 3 U2005 FROM CPU A H0_MEMRESET1_L VC C _ DDR 1 2 3 R2035 X_1K <17> MEM_GPIO2 A A VCC 5 B GND Y 4 H0_MEMRESET_L <8,9,10> X_SN74LVC1G32DBVR VCC TO DIMM 5 B GND F22 AF22 VTT_SENSE MEMZN MEMZP MEMCLK_UP_H(3) MEMCLK_UP_L(3) MEMCLK_UP_H(2) MEMCLK_UP_L(2) MEMCLK_UP_H(1) MEMCLK_UP_L(1) MEMCLK_UP_H(0) MEMCLK_UP_L(0) MEMCLK_LO_H(3) MEMCLK_LO_L(3) MEMCLK_LO_H(2) MEMCLK_LO_L(2) MEMCLK_LO_H(1) MEMCLK_LO_L(1) MEMCLK_LO_H(0) MEMCLK_LO_L(0) MEMCKE_UP MEMCKE_LO MEMVREF0 MEMVREF1 MEMADD(13) MEMADD(12) MEMADD(11) MEMADD(10) MEMADD(9) MEMADD(8) MEMADD(7) MEMADD(6) MEMADD(5) MEMADD(4) MEMADD(3) MEMADD(2) MEMADD(1) MEMADD(0) D11 C11 E9 E10 D9 C9 E7 E8 E5 E6 D5 C5 E3 E4 D3 C3 A11 A12 B10 C10 A9 A10 B8 C8 B6 C6 A5 A6 B4 C4 A3 A4 L1_CADOUT_H(15) L1_CADOUT_L(15) L1_CADOUT_H(14) L1_CADOUT_L(14) L1_CADOUT_H(13) L1_CADOUT_L(13) L1_CADOUT_H(12) L1_CADOUT_L(12) L1_CADOUT_H(11) L1_CADOUT_L(11) L1_CADOUT_H(10) L1_CADOUT_L(10) L1_CADOUT_H(9) L1_CADOUT_L(9) L1_CADOUT_H(8) L1_CADOUT_L(8) L1_CADOUT_H(7) L1_CADOUT_L(7) L1_CADOUT_H(6) L1_CADOUT_L(6) L1_CADOUT_H(5) L1_CADOUT_L(5) L1_CADOUT_H(4) L1_CADOUT_L(4) L1_CADOUT_H(3) L1_CADOUT_L(3) L1_CADOUT_H(2) L1_CADOUT_L(2) L1_CADOUT_H(1) L1_CADOUT_L(1) L1_CADOUT_H(0) L1_CADOUT_L(0) B R2078 100RST AF17 AE16 VTT1 VTT2 VTT3 VTT4 VTT5 VTT6 VTT7 VTT8 VTT9 VTT10 RSVD_MA(15) RSVD_MA(14) SledgeHammer VC C _ DDR 42.2RST 42.2RST H 0 _VREF0_DDR H 0 _VREF0_DDR L1_CADIN_H(15) L1_CADIN_L(15) L1_CADIN_H(14) L1_CADIN_L(14) L1_CADIN_H(13) L1_CADIN_L(13) L1_CADIN_H(12) L1_CADIN_L(12) L1_CADIN_H(11) L1_CADIN_L(11) L1_CADIN_H(10) L1_CADIN_L(10) L1_CADIN_H(9) L1_CADIN_L(9) L1_CADIN_H(8) L1_CADIN_L(8) L1_CADIN_H(7) L1_CADIN_L(7) L1_CADIN_H(6) L1_CADIN_L(6) L1_CADIN_H(5) L1_CADIN_L(5) L1_CADIN_H(4) L1_CADIN_L(4) L1_CADIN_H(3) L1_CADIN_L(3) L1_CADIN_H(2) L1_CADIN_L(2) L1_CADIN_H(1) L1_CADIN_L(1) L1_CADIN_H(0) L1_CADIN_L(0) E18 E17 C18 B18 TP2000 TP2001 AF19 VLDT_1(1) VLDT_1(2) VLDT_1(3) VLDT_1(4) VLDT_1(5) VLDT_1(6) VLDT_1(7) VLDT_1(8) VLDT_1(9) Y 4 X_SN7X_4LVC1G08DCKR,SC-70 R2455 X_0 H0_MEMRESET1_L R2456 0 H0_MEMRESET_L R2034 H0_MDQS35 H0_MDQS34 H0_MDQS33 H0_MDQS32 H0_MDQS31 H0_MDQS30 H0_MDQS29 H0_MDQS28 H0_MDQS27 H0_MDQS26 H0_MDQS25 H0_MDQS24 H0_MDQS23 H0_MDQS22 H0_MDQS21 H0_MDQS20 H0_MDQS19 H0_MDQS18 H0_MDQS17 H0_MDQS16 H0_MDQS15 H0_MDQS14 H0_MDQS13 H0_MDQS12 H0_MDQS11 H0_MDQS10 H0_MDQS9 H0_MDQS8 H0_MDQS7 H0_MDQS6 H0_MDQS5 H0_MDQS4 H0_MDQS3 H0_MDQS2 H0_MDQS1 H0_MDQS0 H0_M D127 AG24 H0_M D126 AH25 H0_M D125 AG26 H0_M D124 AH27 H0_M D123 AF23 H0_M D122 AH24 H0_M D121 AF25 H0_M D120 AJ26 H0_M D119 AG27 H0_M D118 AF26 H0_M D117 AF28 H0_M D116 AE29 H0_M D115 AJ29 H0_M D114 AH29 H0_M D113 AE27 H0_M D112 AD26 H0_M D111 AD27 H0_M D110 AC26 H0_M D109 AA26 H0_M D108 AA28 H0_M D107 AD28 H0_M D106 AC27 H0_M D105 AB29 H0_M D104 AA27 H0_M D103 Y27 H0_M D102 Y28 H0_M D101 V28 H0_M D100 U26 H0_M D99 Y26 H0_M D98 W27 H0_M D97 V27 H0_M D96 U27 H0_M D95 P28 H0_M D94 N29 H0_M D93 M26 H0_M D92 L28 H0_M D91 P27 H0_M D90 P26 H0_M D89 M27 H0_M D88 L27 H0_M D87 K29 H0_M D86 K27 H0_M D85 H28 H0_M D84 G29 H0_M D83 L26 H0_M D82 J28 H0_M D81 H27 H0_M D80 H26 H0_M D79 F27 H0_M D78 F26 H0_M D77 D29 H0_M D76 D27 H0_M D75 G27 H0_M D74 F28 H0_M D73 E27 H0_M D72 C27 H0_M D71 C26 H0_M D70 E25 H0_M D69 D24 H0_M D68 F23 H0_M D67 E26 H0_M D66 F25 H0_M D65 E24 H0_M D64 G23 H0_MD QS35 H0_MD QS34 H0_MD QS33 H0_MD QS32 H0_MD QS31 H0_MD QS30 H0_MD QS29 H0_MD QS28 H0_MD QS27 H0_MD QS26 H0_MD QS25 H0_MD QS24 H0_MD QS23 H0_MD QS22 H0_MD QS21 H0_MD QS20 H0_MD QS19 H0_MD QS18 H0_MD QS17 H0_MD QS16 H0_MD QS15 H0_MD QS14 H0_MD QS13 H0_MD QS12 H0_MD QS11 H0_MD QS10 H0_MD QS9 H0_MD QS8 H0_MD QS7 H0_MD QS6 H0_MD QS5 H0_MD QS4 H0_MD QS3 H0_MD QS2 H0_MD QS1 H0_MD QS0 R27 AG25 AF27 AB27 W29 N27 J27 E29 F24 R28 AF24 AG28 AC28 V26 M28 J26 E28 D25 U31 AJ25 AJ30 AD29 AA31 M30 H30 C30 B25 T31 AL25 AL29 AE31 Y29 M29 H29 C29 C25 MEMDATA(127) MEMDATA(126) MEMDATA(125) MEMDATA(124) MEMDATA(123) MEMDATA(122) MEMDATA(121) MEMDATA(120) MEMDATA(119) MEMDATA(118) MEMDATA(117) MEMDATA(116) MEMDATA(115) MEMDATA(114) MEMDATA(113) MEMDATA(112) MEMDATA(111) MEMDATA(110) MEMDATA(109) MEMDATA(108) MEMDATA(107) MEMDATA(106) MEMDATA(105) MEMDATA(104) MEMDATA(103) MEMDATA(102) MEMDATA(101) MEMDATA(100) MEMDATA(99) MEMDATA(98) MEMDATA(97) MEMDATA(96) MEMDATA(95) MEMDATA(94) MEMDATA(93) MEMDATA(92) MEMDATA(91) MEMDATA(90) MEMDATA(89) MEMDATA(88) MEMDATA(87) MEMDATA(86) MEMDATA(85) MEMDATA(84) MEMDATA(83) MEMDATA(82) MEMDATA(81) MEMDATA(80) MEMDATA(79) MEMDATA(78) MEMDATA(77) MEMDATA(76) MEMDATA(75) MEMDATA(74) MEMDATA(73) MEMDATA(72) MEMDATA(71) MEMDATA(70) MEMDATA(69) MEMDATA(68) MEMDATA(67) MEMDATA(66) MEMDATA(65) MEMDATA(64) MEMDATA(63) MEMDATA(62) MEMDATA(61) MEMDATA(60) MEMDATA(59) MEMDATA(58) MEMDATA(57) MEMDATA(56) MEMDATA(55) MEMDATA(54) MEMDATA(53) MEMDATA(52) MEMDATA(51) MEMDATA(50) MEMDATA(49) MEMDATA(48) MEMDATA(47) MEMDATA(46) MEMDATA(45) MEMDATA(44) MEMDATA(43) MEMDATA(42) MEMDATA(41) MEMDATA(40) MEMDATA(39) MEMDATA(38) MEMDATA(37) MEMDATA(36) MEMDATA(35) MEMDATA(34) MEMDATA(33) MEMDATA(32) MEMDATA(31) MEMDATA(30) MEMDATA(29) MEMDATA(28) MEMDATA(27) MEMDATA(26) MEMDATA(25) MEMDATA(24) MEMDATA(23) MEMDATA(22) MEMDATA(21) MEMDATA(20) MEMDATA(19) MEMDATA(18) MEMDATA(17) MEMDATA(16) MEMDATA(15) MEMDATA(14) MEMDATA(13) MEMDATA(12) MEMDATA(11) MEMDATA(10) MEMDATA(9) MEMDATA(8) MEMDATA(7) MEMDATA(6) MEMDATA(5) MEMDATA(4) MEMDATA(3) MEMDATA(2) MEMDATA(1) MEMDATA(0) MEMDQS(35) MEMDQS(34) MEMDQS(33) MEMDQS(32) MEMDQS(31) MEMDQS(30) MEMDQS(29) MEMDQS(28) MEMDQS(27) MEMDQS(26) MEMDQS(25) MEMDQS(24) MEMDQS(23) MEMDQS(22) MEMDQS(21) MEMDQS(20) MEMDQS(19) MEMDQS(18) MEMDQS(17) MEMDQS(16) MEMDQS(15) MEMDQS(14) MEMDQS(13) MEMDQS(12) MEMDQS(11) MEMDQS(10) MEMDQS(9) MEMDQS(8) MEMDQS(7) MEMDQS(6) MEMDQS(5) MEMDQS(4) MEMDQS(3) MEMDQS(2) MEMDQS(1) MEMDQS(0) MEMRESET_L MEMBANK(1) MEMBANK(0) MEMRAS_L MEMCAS_L MEMWE_L MEMCHECK(15) MEMCHECK(14) MEMCHECK(13) MEMCHECK(12) MEMCHECK(11) MEMCHECK(10) MEMCHECK(9) MEMCHECK(8) MEMCHECK(7) MEMCHECK(6) MEMCHECK(5) MEMCHECK(4) MEMCHECK(3) MEMCHECK(2) MEMCHECK(1) MEMCHECK(0) MEMCS_L(7) MEMCS_L(6) MEMCS_L(5) MEMCS_L(4) MEMCS_L(3) MEMCS_L(2) MEMCS_L(1) MEMCS_L(0) http://laptop-motherboard-schematic.blogspot.com/ X_100K modified on 1/30 1 U2006B G20 G21 AE21 H0_MEMCLK_H5 AE20 H0_M EMCLK_L5 L24 H0_MEMCLK_H3 L25 H0_M EMCLK_L3 R23 H0_MEMCLK_H2 T23 H0_M EMCLK_L2 H23 J23 AD21 H0_MEMCLK_H4 AD20 H0_M EMCLK_L4 Y23 H0_MEMCLK_H1 AA23 H0_M EMCLK_L1 U25 H0_MEMCLK_H0 U24 H0_M EMCLK_L0 H24 H0_MCKEUP H25 H0_MC KELO H0_MEMCLK_H3 H0_MEMCLK_H5 H0_MEMCLK_L5 H0_MEMCLK_H3 H0_MEMCLK_L3 H0_MEMCLK_H2 H0_MEMCLK_L2 <10> <10> <9> <9> <8> <8> H0_MEMCLK_H4 H0_MEMCLK_L4 H0_MEMCLK_H1 H0_MEMCLK_L1 H0_MEMCLK_H0 H0_MEMCLK_L0 <10> <10> <9> <9> <8> <8> R2063 (BOT)120RST H0_M EMCLK_L3 H0_MEMCLK_H2 R2067 H0_MCKEUP H0_MCKELO <11> <11> H0_MAA13 H0_MAA12 H0_MAA11 H0_MAA10 H0_MAA9 H0_MAA8 H0_MAA7 H0_MAA6 H0_MAA5 H0_MAA4 H0_MAA3 H0_MAA2 H0_MAA1 H0_MAA0 <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> (BOT)120RST H0_M EMCLK_L2 H0_MEMCLK_H1 H0_M EMCLK_L1 V23 M23 H0_MEMCLK_H0 AE23 J24 J25 V24 K23 L23 K25 M25 M24 N25 N23 P23 T25 V25 H0_MAA13 H0_MAA12 H0_MAA11 H0_MAA10 H0_MAA9 H0_MAA8 H0_MAA7 H0_MAA6 H0_MAA5 H0_MAA4 H0_MAA3 H0_MAA2 H0_MAA1 H0_MAA0 AJ24 AK25 AK27 AJ27 AL24 AK24 AL26 AL27 AJ28 AK30 AJ31 AG29 AL28 AK28 AH31 AG30 AG31 AF30 AD31 AC30 AF29 AF31 AD30 AC29 AB31 AA29 Y31 W31 AC31 AA30 Y30 V29 P31 M31 L30 L29 P29 N31 L31 K31 J30 J29 G31 F29 J31 H31 F31 F30 D31 C31 B30 C28 E31 E30 A29 B28 B27 A26 C24 A24 A28 A27 A25 B24 H0_M D63 H0_M D62 H0_M D61 H0_M D60 H0_M D59 H0_M D58 H0_M D57 H0_M D56 H0_M D55 H0_M D54 H0_M D53 H0_M D52 H0_M D51 H0_M D50 H0_M D49 H0_M D48 H0_M D47 H0_M D46 H0_M D45 H0_M D44 H0_M D43 H0_M D42 H0_M D41 H0_M D40 H0_M D39 H0_M D38 H0_M D37 H0_M D36 H0_M D35 H0_M D34 H0_M D33 H0_M D32 H0_M D31 H0_M D30 H0_M D29 H0_M D28 H0_M D27 H0_M D26 H0_M D25 H0_M D24 H0_M D23 H0_M D22 H0_M D21 H0_M D20 H0_M D19 H0_M D18 H0_M D17 H0_M D16 H0_M D15 H0_M D14 H0_M D13 H0_M D12 H0_M D11 H0_M D10 H0_M D9 H0_M D8 H0_M D7 H0_M D6 H0_M D5 H0_M D4 H0_M D3 H0_M D2 H0_M D1 H0_M D0 H0_MD[63..0] R2073 (BOT)120RST H0_M EMCLK_L0 H0_MEMCLK_H5 R985 (BOT)120RST H0_M EMCLK_L5 H0_MEMCLK_H4 <11> R986 (BOT)120RST H0_M EMCLK_L4 C B G25 H0_MEMRESET1_L W25 W23 H0_MEMBAKA1 <11> H0_MEMBAKA0 <11> Y25 H0_-M SRASA AA25 H0_-M SCASA Y24 H0_-MSRASA H0_-MSCASA H0_-MSWEA U28 T29 P24 P25 T27 R26 R25 R24 H0_MEMC HECK15 H0_MEMC HECK14 H0_MEMC HECK13 H0_MEMC HECK12 H0_MEMC HECK11 H0_MEMC HECK10 H0_MEMC HECK9 H0_MEMC HECK8 V30 U29 R30 P30 V31 U30 R29 R31 H0_MEMC HECK7 H0_MEMC HECK6 H0_MEMC HECK5 H0_MEMC HECK4 H0_MEMC HECK3 H0_MEMC HECK2 H0_MEMC HECK1 H0_MEMC HECK0 AD23 AE25 AD24 AD25 AC24 AC25 AB25 AA24 H0_- MCS5 H0_- MCS4 H0_- MCS3 H0_- MCS2 H0_- MCS1 H0_- MCS0 <11> <11> <11> H0_MEMCHECK15 <11> H0_MEMCHECK14 <11> H0_MEMCHECK13 <11> H0_MEMCHECK12 <11> H0_MEMCHECK11 <11> H0_MEMCHECK10 <11> H0_MEMCHECK9 <11> H0_MEMCHECK8 <11> H0_MEMCHECK7 H0_MEMCHECK6 H0_MEMCHECK5 H0_MEMCHECK4 H0_MEMCHECK3 H0_MEMCHECK2 H0_MEMCHECK1 H0_MEMCHECK0 H0_-MCS5 H0_-MCS4 H0_-MCS3 H0_-MCS2 H0_-MCS1 H0_-MCS0 <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> <11> A Micro Star Restricted Secret Title R ev CPU0_K8 DDR & HT Document Number SledgeHammer 4 3 2 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 5 D R2072 (BOT)120RST 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 4 44 5 4 VDDA25 C2077 C2070 C2089 C2088 3 2 1 LAYOUT: Route VDDA trace approx. 50 mils wide (use 2x25 mil traces to exit ball) and 500 mils long. CT2003 U2006C 4.7u/0805 3300p/50V/X7R 100u/10V 1000P/50V/X7R 0.22u/16V VDDA25 VCC2_5 D C2073 FB2000 <37> COREFB0_H <37> COREFB0_L <22> CPUCLK0_H <22> CPUCLK0_L 43.2RST 43.2RST E1 D1 L0_REF1 L0_REF0 R2057 R2058 0 0 L7 L6 COREFB_H COREFB_L TP2006 K7 CORESENSE_H R2422 (BOT)169RST CLKIN0_L H0_TDI H0_DBREQ_L AE6 AE7 AD7 AF7 J7 H0_SCANCLK1 AE10 H0_SCANCLK2 AE11 VCC2_5 HT_STOP# R2062 680 H0_SCANEN AF11 H0_SSENA H0_SSENB H0_NC_T3 H0_NC_T4 AE13 AE12 T3 T4 H0_NC_AF13 Q2007 2N7002S PS_ON#A PS_ON#A CLKIN_H CLKIN_L AE15 THERMDA THERMDC AJ1 AH1 VID(4) VID(3) VID(2) VID(1) VID(0) G9 F9 G10 H11 G11 BP(3) BP(2) BP(1) BP(0) H13 G6 F7 H12 FBCLKOUT_H FBCLKOUT_L CPU_THEMTRIP# <13,16> R2049 R2048 R2050 R2051 R2044 0 0 0 0 0 VID4 VID3 VID2 VID1 VID0 <38> <32,38> <32,38> <32,38> <32,38> modified on 1/30 D H0_TRST_L R2463 1K H0_TCK R2462 1K H0_BP3 H0_BP2 H0_BP1 H0_BP0 VCC2_5 G18 H0_FBCLKOUT_H H18 R2421 80.6RST BYPASSCLK_H BYPASSCLK_L Routed differentially. THERMDA_CPU1 <33> VTIN_GND <13,33> H0_FBCLKOUT_L This termination resistor should be placed as close to Processor as possible. H0_TMS R2461 1K H0_TDI R2079 1K H0_NC_G14 R2043 820 H0_NC_AE14 R2088 680 H0_NC_AF13 R2087 680 STRAPPINGS H0_TMS H0_TCK H0_TRST_L C <39> VDDA1 VDDA2 VDDA3 R2060 R2059 3900P/50V/X7R CLKIN0_H G16 C2083 CLKIN0_L H16 C2084 3900P/50V/X7R H0_NC_G14 G14 H0_NC_H14 H14 VERY CLOSE TO CPU CLKIN0_H THERMTRIP_L C1 D2 C2 0.1u VDD_12_A Routed differentially with a 20/5/5/5/20. 180nH/1210 TP2008 TP2007 L8 K8 TP2017 B AF13 H0_NC_AE14 TDO LAYOUT: Route FBCLKOUT_H/L differentially with 20/5/5/5/20 for 1.5" to escape the BGA. AE8 TP2014 DBREQ_L DBRDY G8 H0_DBREQ_L R2052 U1_R6 SCANEN SCANSHIFTEN SCANSHIFTENB SCANIN_H SCANIN_L SCANOUT_H SCANOUT_L V5 U5 TSTOUT H7 ANALOG3 ANALOG2 ANALOG1 ANALOG0 T7 W6 R6 U6 SINGLECHAIN PLLCHRZ_H PLLCHRZ_L AF15 DCLKTWO BURNIN_L RESET_L LDTSTOP_L PWROK R2457 49.9RST TP2004 U1_U6 U1_T7 U1_W6 H0_NC_T3 R2458 TP2011 TP2010 U1_T7 U1_W6 U1_R6 U1_U6 680 2 4 6 8 RN2026 1 3 5 7 680_8P4R RSVD_SMBUSC RSVD_SMBUSD AF9 AE9 H0_DBRDY 1K R2047 1K H0_NC_H14 R2042 820 H0_SCANEN R2085 680 H0_SCANCLK1 R2080 680 H0_SCANCLK2 R2084 680 H0_SSENA R2086 680 H0_SSENB R2081 680 H0_BP3 H0_BP2 R2056 R2053 X_680 X_680 H0_BP1 H0_BP0 R2054 R2055 680 680 B TP2016 TP2015 VDD_12_A VCC2_5 R2041 C H0_DBRDY SCANCLK1 SCANCLK2 AE14 G12 J6 F12 <13,16> CPU_RST# <13,16> HT_STOP# <13,16> CPU_PWRGD TMS TCK TRST_L TDI C2068 C2092 33P 33P 680 H0_NC_T4 TP2018 TP2019 TP2005 AG1 AH2 H9 FREE7 FREE11 FREE15 TP2020 TP2012 TP2013 TP2009 AJ2 AA6 AC6 N6 FREE12 FREE21 FREE1 FREE3 VCC2_5 R2070 49.9RST R2068 X_49.9RST SledgeHammer R2493 680 CPU_RST# A A Micro Star Restricted Secret VCC2_5 VCC2_5 R2494 680 Title HT_STOP# R2495 680 CPU_THEMTRIP# Document Number Rev CPU0_K8 HDT & MISC MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 5 4 3 http://laptop-motherboard-schematic.blogspot.com/ 2 0A Last Revision Date: Tuesday, February 15, 2005 Sheet 5 44 of 1 5 4 3 2 1 VDD_12_A U2006A D CT2007 C2132 100u/10V <12> H0_CADIN[15..0] <12> H0_CADIN#[15..0] C <12> H0_CLKIN1 <12> H0_CLKIN#1 <12> H0_CLKIN0 <12> H0_CLKIN#0 B <12> H0_CTLIN0 <12> H0_CTLIN#0 C2080 0.22u/16V/X7R 103P N7 R7 U7 W7 M8 P8 AA7 V8 Y8 VLDT_0(1) VLDT_0(2) VLDT_0(3) VLDT_0(4) VLDT_0(5) VLDT_0(6) VLDT_0(7) VLDT_0(8) VLDT_0(9) D H0 _CADIN15 H0_CADIN#15 H0 _CADIN14 H0_CADIN#14 H0 _CADIN13 H0_CADIN#13 H0 _CADIN12 H0_CADIN#12 H0 _CADIN11 H0_CADIN#11 H0 _CADIN10 H0_CADIN#10 H0_ CADIN9 H0 _CADIN#9 H0_ CADIN8 H0 _CADIN#8 H0_ CADIN7 H0 _CADIN#7 H0_ CADIN6 H0 _CADIN#6 H0_ CADIN5 H0 _CADIN#5 H0_ CADIN4 H0 _CADIN#4 H0_ CADIN3 H0 _CADIN#3 H0_ CADIN2 H0 _CADIN#2 H0_ CADIN1 H0 _CADIN#1 H0_ CADIN0 H0 _CADIN#0 R5 T5 P3 P4 N5 P5 M3 M4 K3 K4 J5 K5 H3 H4 G5 H5 R3 R2 N1 P1 N3 N2 L1 M1 J1 K1 J3 J2 G1 H1 G3 G2 L0_CADIN_H(15) L0_CADIN_L(15) L0_CADIN_H(14) L0_CADIN_L(14) L0_CADIN_H(13) L0_CADIN_L(13) L0_CADIN_H(12) L0_CADIN_L(12) L0_CADIN_H(11) L0_CADIN_L(11) L0_CADIN_H(10) L0_CADIN_L(10) L0_CADIN_H(9) L0_CADIN_L(9) L0_CADIN_H(8) L0_CADIN_L(8) L0_CADIN_H(7) L0_CADIN_L(7) L0_CADIN_H(6) L0_CADIN_L(6) L0_CADIN_H(5) L0_CADIN_L(5) L0_CADIN_H(4) L0_CADIN_L(4) L0_CADIN_H(3) L0_CADIN_L(3) L0_CADIN_H(2) L0_CADIN_L(2) L0_CADIN_H(1) L0_CADIN_L(1) L0_CADIN_H(0) L0_CADIN_L(0) L0_CADOUT_H(15) L0_CADOUT_L(15) L0_CADOUT_H(14) L0_CADOUT_L(14) L0_CADOUT_H(13) L0_CADOUT_L(13) L0_CADOUT_H(12) L0_CADOUT_L(12) L0_CADOUT_H(11) L0_CADOUT_L(11) L0_CADOUT_H(10) L0_CADOUT_L(10) L0_CADOUT_H(9) L0_CADOUT_L(9) L0_CADOUT_H(8) L0_CADOUT_L(8) L0_CADOUT_H(7) L0_CADOUT_L(7) L0_CADOUT_H(6) L0_CADOUT_L(6) L0_CADOUT_H(5) L0_CADOUT_L(5) L0_CADOUT_H(4) L0_CADOUT_L(4) L0_CADOUT_H(3) L0_CADOUT_L(3) L0_CADOUT_H(2) L0_CADOUT_L(2) L0_CADOUT_H(1) L0_CADOUT_L(1) L0_CADOUT_H(0) L0_CADOUT_L(0) V4 V3 Y5 W5 Y4 Y3 AB5 AA5 AD5 AC5 AD4 AD3 AF5 AE5 AF4 AF3 V1 U1 W2 W3 Y1 W1 AA2 AA3 AC2 AC3 AD1 AC1 AE2 AE3 AF1 AE1 H0_CADOUT15 H0_CADOUT#15 H0_CADOUT14 H0_CADOUT#14 H0_CADOUT13 H0_CADOUT#13 H0_CADOUT12 H0_CADOUT#12 H0_CADOUT11 H0_CADOUT#11 H0_CADOUT10 H0_CADOUT#10 H0_CADOUT9 H0_CADOUT#9 H0_CADOUT8 H0_CADOUT#8 H0_CADOUT7 H0_CADOUT#7 H0_CADOUT6 H0_CADOUT#6 H0_CADOUT5 H0_CADOUT#5 H0_CADOUT4 H0_CADOUT#4 H0_CADOUT3 H0_CADOUT#3 H0_CADOUT2 H0_CADOUT#2 H0_CADOUT1 H0_CADOUT#1 H0_CADOUT0 H0_CADOUT#0 H0_CLKIN1 H0_CLKIN#1 H0_CLKIN0 H0_CLKIN#0 L5 M5 L3 L2 L0_CLKIN_H(1) L0_CLKIN_L(1) L0_CLKIN_H(0) L0_CLKIN_L(0) L0_CLKOUT_H(1) L0_CLKOUT_L(1) L0_CLKOUT_H(0) L0_CLKOUT_L(0) AB4 AB3 AB1 AA1 H0_CLKOUT1 H0_CLKOUT#1 H0_CLKOUT0 H0_CLKOUT#0 H0_CTLIN0 H0_CTLIN#0 R1 T1 L0_CTLIN_H(0) L0_CTLIN_L(0) L0_CTLOUT_H(0) L0_CTLOUT_L(0) U2 U3 H0_CTLOUT0 H0_CTLOUT#0 H0_CADOUT[15..0] <12> H0_CADOUT#[15..0] <12> VDD_12_A C2141 4.7u/1206 <16> L0_CADIN[15..0] H0_CLKOUT1 H0_CLKOUT#1 H0_CLKOUT0 H0_CLKOUT#0 <12> <12> <12> <12> H0_CTLOUT0 <12> H0_CTLOUT#0 <12> <16> L0_CADIN#[15..0] SledgeHammer <16> L0_CLKIN1 <16> L0_CLKIN#1 <16> L0_CLKIN0 <16> L0_CLKIN#0 <16>L0_CTLIN0 <16> L0_CTLIN#0 VDD_12_A C2164 C2123 0.22u/16V/X7R 103P L0_CADIN15 L0_CADIN#15 L0_CADIN14 L0_CADIN#14 L0_CADIN13 L0_CADIN#13 L0_CADIN12 L0_CADIN#12 L0_CADIN11 L0_CADIN#11 L0_CADIN10 L0_CADIN#10 L 0_CADIN9 L0_CADIN#9 L 0_CADIN8 L0_CADIN#8 L 0_CADIN7 L0_CADIN#7 L 0_CADIN6 L0_CADIN#6 L 0_CADIN5 L0_CADIN#5 L 0_CADIN4 L0_CADIN#4 L 0_CADIN3 L0_CADIN#3 L 0_CADIN2 L0_CADIN#2 L 0_CADIN1 L0_CADIN#1 L 0_CADIN0 L0_CADIN#0 VLDT_2(1) VLDT_2(2) VLDT_2(3) VLDT_2(4) VLDT_2(5) VLDT_2(6) VLDT_2(7) VLDT_2(8) VLDT_2(9) AG11 AG12 AJ10 AH10 AG9 AG10 AJ8 AH8 AJ6 AH6 AG5 AG6 AJ4 AH4 AG3 AG4 AJ11 AK11 AL9 AL10 AJ9 AK9 AL7 AL8 AL5 AL6 AJ5 AK5 AL3 AL4 AJ3 AK3 L2_CADIN_H(15) L2_CADIN_L(15) L2_CADIN_H(14) L2_CADIN_L(14) L2_CADIN_H(13) L2_CADIN_L(13) L2_CADIN_H(12) L2_CADIN_L(12) L2_CADIN_H(11) L2_CADIN_L(11) L2_CADIN_H(10) L2_CADIN_L(10) L2_CADIN_H(9) L2_CADIN_L(9) L2_CADIN_H(8) L2_CADIN_L(8) L2_CADIN_H(7) L2_CADIN_L(7) L2_CADIN_H(6) L2_CADIN_L(6) L2_CADIN_H(5) L2_CADIN_L(5) L2_CADIN_H(4) L2_CADIN_L(4) L2_CADIN_H(3) L2_CADIN_L(3) L2_CADIN_H(2) L2_CADIN_L(2) L2_CADIN_H(1) L2_CADIN_L(1) L2_CADIN_H(0) L2_CADIN_L(0) L0_CLKIN1 L0_CLKIN#1 L0_CLKIN0 L0_CLKIN#0 AG7 AG8 AJ7 AK7 L0_CTLIN0 L0_CTLIN#0 AL11 AL12 AJ12 AH12 C2146 C2093 C2079 C2163 U2006F AB10 AC11 AD10 AD8 AB14 AC15 AB16 AC16 AC9 L2_CADOUT_H(15) L2_CADOUT_L(15) L2_CADOUT_H(14) L2_CADOUT_L(14) L2_CADOUT_H(13) L2_CADOUT_L(13) L2_CADOUT_H(12) L2_CADOUT_L(12) L2_CADOUT_H(11) L2_CADOUT_L(11) L2_CADOUT_H(10) L2_CADOUT_L(10) L2_CADOUT_H(9) L2_CADOUT_L(9) L2_CADOUT_H(8) L2_CADOUT_L(8) L2_CADOUT_H(7) L2_CADOUT_L(7) L2_CADOUT_H(6) L2_CADOUT_L(6) L2_CADOUT_H(5) L2_CADOUT_L(5) L2_CADOUT_H(4) L2_CADOUT_L(4) L2_CADOUT_H(3) L2_CADOUT_L(3) L2_CADOUT_H(2) L2_CADOUT_L(2) L2_CADOUT_H(1) L2_CADOUT_L(1) L2_CADOUT_H(0) L2_CADOUT_L(0) L2_CLKIN_H(1) L2_CLKIN_L(1) L2_CLKIN_H(0) L2_CLKIN_L(0) L2_CLKOUT_H(1) L2_CLKOUT_L(1) L2_CLKOUT_H(0) L2_CLKOUT_L(0) L2_CTLIN_H(0) L2_CTLIN_L(0) L2_CTLOUT_H(0) L2_CTLOUT_L(0) L2_RSVD1 L2_RSVD2 L2_RSVD3 L2_RSVD4 AH14 AJ14 AG16 AG15 AH16 AJ16 AG18 AG17 AG20 AG19 AH20 AJ20 AG22 AG21 AH22 AJ22 AL14 AL13 AK15 AJ15 AL16 AL15 AK17 AJ17 AK19 AJ19 AL20 AL19 AK21 AJ21 AL22 AL21 L0_CADOUT15 L0_CADOUT#15 L0_CADOUT14 L0_CADOUT#14 L0_CADOUT13 L0_CADOUT#13 L0_CADOUT12 L0_CADOUT#12 L0_CADOUT11 L0_CADOUT#11 L0_CADOUT10 L0_CADOUT#10 L0_CADOUT9 L0_CADOUT#9 L0_CADOUT8 L0_CADOUT#8 L0_CADOUT7 L0_CADOUT#7 L0_CADOUT6 L0_CADOUT#6 L0_CADOUT5 L0_CADOUT#5 L0_CADOUT4 L0_CADOUT#4 L0_CADOUT3 L0_CADOUT#3 L0_CADOUT2 L0_CADOUT#2 L0_CADOUT1 L0_CADOUT#1 L0_CADOUT0 L0_CADOUT#0 AH18 AJ18 AL18 AL17 L0_CLKOUT1 L0_CLKOUT#1 L0_CLKOUT0 L0_CLKOUT#0 AK13 AJ13 L0_CTLOUT0 L0_CTLOUT#0 L0_CADOUT[15..0] <16> C B L0_CADOUT#[15..0] <16> L0_CLKOUT1 L0_CLKOUT#1 L0_CLKOUT0 L0_CLKOUT#0 <16> <16> <16> <16> L0_CTLOUT0 <16> L0_CTLOUT#0 <16> AG13 AG14 CT2006 SledgeHammer 0.22u/16V/X7R 1000P/50V/X7R 100u/10V 0.22u/16V/X7R 1000P/50V/X7R A A Micro Star Restricted Secret Title Document Number R ev CPU0_K8 HT0 & HT2 5 4 3 http://laptop-motherboard-schematic.blogspot.com/ 2 0A MS- 9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 1 Last Revision Date: Thursday, February 17, 2005 Sheet 6 of 44 B 5 4 4 .7 u/1206 C2104 4 .7 u/1206 C2139 4 .7 u/1206 C2166 4 .7 u/1206 4 3 LAYOUT: Place solder side of processor. C2606 VCCP0 4.7u/1206 C2167 4 .7 u/1206 V C C _ D DR BULK / Decopuling VCCP0 C VCCP0 C2551 C2550 C2552 C2102 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R C2127 Buck-decoupling Mid-Freq. decoupling Cap. ( 7 * 4.7uF / 1206 X7R ) VCCP0 4 .7 u/1206 4.7u/1206 C2086 3 http://laptop-motherboard-schematic.blogspot.com/ C2162 C2151 C2133 C2058 C2161 C2142 C2184 C2049 2 C2075 C2129 C2135 C2125 1000P/50V/X7R 1000P/50V/X7R 1000P/50V/X7R 1000P/50V/X7R S le d g eHammer C2113 AG2 E2 P13 W16 D23 AH23 4 .7 u/1206 C2087 V6 AD12 H2 AA4 T18 V18 Y18 K12 F19 N19 R19 U19 W19 D20 AE4 M20 P20 T20 V20 Y20 AK20 B21 AH21 AK4 B5 AH5 K6 P6 T8 AB6 AF6 M2 F6 D8 G7 AB8 AK8 B9 K18 L9 N9 R9 T2 U9 W9 AA9 AB18 AH9 W13 M10 P10 T10 V10 Y2 Y10 AB12 AF10 F11 L11 N11 R11 U11 W11 AA11 AD2 D12 M12 P12 T12 V12 Y12 AC13 AK12 B13 L13 D4 N13 R13 U13 AA13 AH13 J13 M14 P14 T14 J4 V14 Y14 AD14 AF14 F15 L15 N15 R15 U15 W15 N4 AA15 D16 F18 M16 P16 T16 V16 Y16 AD16 AK16 U4 B17 L17 N17 R17 U17 W17 AA17 AH17 M18 P18 C2085 X_(BOT)SP-CAP,220u/2V AF20 X_(BOT)SP-CAP,220u/2V C2557 AB23 AC23 L19 W21 AA21 J21 M22 P22 T22 V22 Y22 AB22 AJ23 AA19 C23 E23 K26 T26 AE28 G26 N26 W26 AE26 AG23 K20 D28 K28 T28 AB28 AH28 AH26 G28 N28 W28 AB26 AB20 L21 N21 R21 U21 H22 D26 K22 A23 U23 AL23 AC21 AD22 VCCP0 T9 AC22 Y9 AB9 AD9 D10 J10 AD13 L10 N10 R10 U10 T6 AA10 AC10 AK10 B11 L14 H15 J8 K11 M11 P11 T11 V11 N14 Y11 AA12 N16 AF12 F13 G15 F10 AD15 K13 U14 M13 AB11 AD11 AH11 G13 J12 N12 R12 U12 R14 W12 W14 AA14 AC14 AH15 AK14 B15 K15 M15 B23 P15 T15 V15 Y15 AB15 D14 J14 H17 G24 L16 R16 U16 W18 AA16 AC17 AF16 F16 K17 N24 M17 P17 T17 V17 Y17 AB17 AD17 D18 J18 W24 L18 N18 R18 U18 W10 AA18 AE17 AK18 B19 G30 K19 M19 T19 V19 Y19 AB19 AH19 J20 L20 W30 N20 R20 U20 W20 AA20 AC20 AF21 K21 M21 AB24 P21 T21 V21 Y21 AB21 D22 G22 L22 N22 B26 R22 U22 W22 AA22 AE22 AK22 J22 AE24 AK26 B29 AK23 K24 T24 AE30 AK29 D30 K30 T30 AB30 AH30 AH7 V9 L12 AC12 U2 0 06D VSS6 VDDIO1 VSS7 VDDIO2 VSS8 VDDIO3 VSS9 VDDIO4 VSS10 VDDIO5 VSS11 VDDIO6 VSS12 VDDIO7 VSS92 VDDIO8 VSS13 VDDIO9 VSS14 VDDIO10 VSS15 VDDIO11 VSS16 VDDIO12 VSS17 VDDIO13 VSS18 VDDIO14 VSS19 VDDIO15 VSS20 VDDIO16 VSS21 VDDIO17 VSS93 VDDIO18 VSS22 VDDIO19 VSS23 VDDIO20 VSS24 VDDIO21 VSS25 VDDIO22 VSS26 VDDIO23 VSS27 VDDIO24 VSS28 VDDIO25 VSS29 VDDIO26 VSS30 VDDIO27 VSS94 VDDIO28 VSS31 VDDIO29 VSS32 VDDIO30 VSS33 VDDIO31 VSS34 VDDIO32 VSS35 VDDIO33 VSS36 VDDIO34 VSS37 VDDIO35 VSS95 VDDIO36 VSS38 VDDIO37 VSS39 VDDIO38 VSS40 VDDIO40 VSS41 VDDIO41 VSS42 VDDIO42 VSS43 VDDIO43 VSS44 VDDIO44 VSS45 VDDIO45 VSS46 VDDIO47 VSS96 VDDIO48 VSS47 VDDIOFB_H VDDIOFB_L VSS48 VDDIO_SENSE VSS49 VSS50 VSS51 VSS52 VSS53 VSS54 VSS55 VSS97 VDD117 VSS56 VDD118 VSS57 VDD1 VSS58 VDD2 VSS59 VDD3 VSS60 VDD4 VSS61 VDD5 VSS62 VDD119 VSS63 VDD7 VSS64 VDD8 VSS98 VDD9 VSS65 VDD10 VSS66 VDD11 VSS67 VDD12 VSS68 VDD13 VSS69 VDD14 VSS70 VDD15 VSS71 VDD16 VSS99 VDD17 VSS72 VDD18 VSS82 VDD19 VSS83 VDD20 VSS84 VDD21 VSS85 VDD22 VSS86 VDD23 VSS87 VDD24 VSS88 VDD25 VSS89 VDD26 VSS101 VDD27 VSS90 VDD28 VSS73 VDD29 VSS74 VDD30 VSS75 VDD31 VSS76 VDD32 VSS77 VDD33 VSS78 VDD34 VSS79 VDD35 VSS80 VDD36 VSS100 VDD37 VSS81 VDD38 VSS102 VDD39 VSS103 VDD40 VSS104 VDD41 VSS105 VDD42 VSS106 VDD43 VSS107 VDD44 VSS108 VDD45 VSS109 VDD46 VSS182 VDD47 VSS110 VDD48 VSS111 VDD49 VSS112 VDD50 VSS113 VDD51 VSS114 VDD52 VSS115 VDD53 VSS116 VDD54 VSS117 VDD55 VSS183 VDD56 VSS118 VDD57 VSS119 VDD58 VSS120 VDD59 VSS121 VDD60 VSS122 VDD61 VSS123 VDD62 VSS124 VDD63 VSS125 VDD64 VSS126 VDD65 VSS184 VDD66 VSS127 VDD67 VSS128 VDD68 VSS129 VDD69 VSS130 VDD70 VSS131 VDD71 VSS132 VDD72 VSS133 VDD73 VSS134 VDD74 VSS135 VDD75 VSS185 VDD76 VSS136 VDD77 VSS137 VDD78 VSS138 VDD79 VSS139 VDD80 VSS140 VDD81 VSS141 VDD82 VSS142 VDD83 VSS143 VDD84 VSS144 VDD85 VSS186 VDD86 VSS145 VDD87 VSS146 VDD88 VSS147 VDD89 VSS148 VDD90 VSS149 VDD91 VSS150 VDD92 VSS151 VDD93 VSS152 VDD94 VSS153 VDD95 VSS187 VDD96 VSS154 VDD97 VSS155 VDD98 VSS156 VDD99 VSS157 VDD100 VSS158 VDD101 VSS159 VDD102 VSS160 VDD103 VSS161 VDD104 VSS162 VDD105 VSS188 VDD106 VSS163 VDD107 VSS164 VDD108 VSS165 VDD109 VSS166 VDD110 VSS167 VDD111 VSS168 VDD112 VSS169 VDD113 VSS170 VDD114 VSS171 VDD115 VSS189 VDD116 VSS172 VSS173 VSS174 VSS175 VSS176 VSS177 VSS178 VSS179 VSS180 VSS190 VSS181 VSS191 VSS192 VSS193 VSS194 VSS195 VSS196 VSS197 VSS198 VSS203 VSS199 VSS202 VSS1 VSS91 VSS2 VSS5 VSS3 VSS200 VSS4 VSS201 C2605 P9 F17 P19 N30 F1 F2 K2 P2 T13 V2 AB2 AF2 AK2 B3 AH3 G4 L4 R4 V13 W4 AC4 F5 D6 H6 M7 AB7 Y6 AD6 J17 AK6 B7 F14 P7 V7 Y7 M6 Y13 N8 R8 U8 W8 AA8 AF8 F8 G17 K9 AB13 M9 5 2 1 D D EMI LAYOUT: Place 1 capacitor every 1-1.5" along VDD_CORE perimiter. C2547 Place on CPU Solder side VCCP0 4 .7 u/1206 6 .8 p /50V/NPO 6 .8 p /50V/NPO 6 .8 p /5 0V/NPO 6 .8 p /5 0V/NPO 6 .8 p /5 0V/NPO 6 .8 p /50V/NPO 6 .8 p /5 0V/NPO 6 .8 p /5 0V/NPO 6 .8 p /5 0V/NPO 6 .8 p /50V/NPO 6 .8 p /50V/NPO 6 .8 p /5 0V/NPO C2120 LAYOUT: Place clolse to socket. LAYOUT: Place 1000pF capacitors between VRM & CPU. VCCP0 C2117 C 4 .7 u/1206 C2137 Buck-decoupling Mid-Freq. decoupling Cap. ( 7 * 4.7uF / 1206 X7R ) VCCP0 C2116 4.7u/1206 PLEASE THESE PARTS UNDER SOLDER SIDE OF U27 VCCP0 B A A Title Micro Star Restricted Secret Document Number MICRO-STAR INT'L CO.,LTD. No . 6 9 , L i-D e S t, J ung -He C ity, T aip e i Hs ien, Taiwan http ://www.m s i.c o m .tw 1 CPU0 _K8 POWER & GND M S - 9 620 L as t R e vis io n D ate: T ue s d ay, F e b ruary 15, 2005 S heet of 7 44 Rev 0A 5 4 3 2 1 Registered DDR333 SDRAM Sockets Channel B Channel A D D VC C _ DDR 90 63 <9,10,11> H0_DR_-MSWEA 1 D D R _VREF C2032 1000P/50V/X7R CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7 CK0(DU) CK0#(DU) CK1(CK0) CK1#(CK0#) CK2(DU) CK2#(DU) NC5 NC(RESET#) CKE0 CKE1 CAS# RAS# DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 DM8 VREF SLAVE ADDRESS = 1010000B H0_DR_MDQS0 H0_DR_MDQS1 H0_DR_MDQS2 H0_DR_MDQS3 H0_DR_MDQS4 H0_DR_MDQS5 H0_DR_MDQS6 H0_DR_MDQS7 H0_DR_MDQS8 167 H0_DR_MAA13 <9,10,11> 48 43 41 130 37 32 125 29 122 27 141 118 115 103 H0_DR_MAA0 H0_DR_MAA1 H0_DR_MAA2 H0_DR_MAA3 H0_DR_MAA4 H0_DR_MAA5 H0_DR_MAA6 H0_DR_MAA7 H0_DR_MAA8 H0_DR_MAA9 H0_DR_MAA10 H0_DR_MAA11 H0_DR_MAA12 59 52 113 92 91 181 182 183 <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> H0_DR_MEMBAKA0 <9,10,11> H0_DR_MEMBAKA1 <9,10,11> SMB_MEM_CLK SMB_MEM_DATA SMB_MEM_CLK <9,10,17> SMB_MEM_DATA <9,10,17> 44 45 49 51 134 135 142 144 H0_DR_MEMCHECK0 H0_DR_MEMCHECK1 H0_DR_MEMCHECK2 H0_DR_MEMCHECK3 H0_DR_MEMCHECK4 H0_DR_MEMCHECK5 H0_DR_MEMCHECK6 H0_DR_MEMCHECK7 16 17 137 138 76 75 H0_MEMCLK_H0 <4> H0_MEMCLK_L0 <4> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> 173 10 H0_MEMRESET_L <4,9,10> 21 111 65 154 H0_DR_MCKELO H0_DR_MCKEUP H0_DR_-MSCASA H0_DR_-MSRASA 97 107 119 129 149 159 169 177 140 H0_DR_MDQS9 <9,10,11> H0_DR_MDQS10 <9,10,11> H0_DR_MDQS11 <9,10,11> H0_DR_MDQS12 <9,10,11> H0_DR_MDQS13 <9,10,11> H0_DR_MDQS14 <9,10,11> H0_DR_MDQS15 <9,10,11> H0_DR_MDQS16 <9,10,11> H0_DR_MDQS17 <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> H0_DR_M D64 H0_DR_M D65 H0_DR_M D66 H0_DR_M D67 H0_DR_M D68 H0_DR_M D69 H0_DR_M D70 H0_DR_M D71 H0_DR_M D72 H0_DR_M D73 H0_DR_M D74 H0_DR_M D75 H0_DR_M D76 H0_DR_M D77 H0_DR_M D78 H0_DR_M D79 H0_DR_M D80 H0_DR_M D81 H0_DR_M D82 H0_DR_M D83 H0_DR_M D84 H0_DR_M D85 H0_DR_M D86 H0_DR_M D87 H0_DR_M D88 H0_DR_M D89 H0_DR_M D90 H0_DR_M D91 H0_DR_M D92 H0_DR_M D93 H0_DR_M D94 H0_DR_M D95 H0_DR_M D96 H0_DR_M D97 H0_DR_M D98 H0_DR_M D99 H0_DR_MD 100 H0_DR_MD 101 H0_DR_MD 102 H0_DR_MD 103 H0_DR_MD 104 H0_DR_MD 105 H0_DR_MD 106 H0_DR_MD 107 H0_DR_MD 108 H0_DR_MD 109 H0_DR_MD 110 H0_DR_MD 111 H0_DR_MD 112 H0_DR_MD 113 H0_DR_MD 114 H0_DR_MD 115 H0_DR_MD 116 H0_DR_MD 117 H0_DR_MD 118 H0_DR_MD 119 H0_DR_MD 120 H0_DR_MD 121 H0_DR_MD 122 H0_DR_MD 123 H0_DR_MD 124 H0_DR_MD 125 H0_DR_MD 126 H0_DR_MD 127 2 4 6 8 94 95 98 99 12 13 19 20 105 106 109 110 23 24 28 31 114 117 121 123 33 35 39 40 126 127 131 133 53 55 57 60 146 147 150 151 61 64 68 69 153 155 161 162 72 73 79 80 165 166 170 171 83 84 87 88 174 175 178 179 H0_DR_-MSWEA 90 63 1 D D R _VREF C2034 1000P/50V/X7R VC C _ DDR C2042 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 DQS8 FETEN A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10_AP A11 A12 A13 BA0 BA1 BA2 SCL SDA SA0 SA1 SA2 CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7 CK0(DU) CK0#(DU) CK1(CK0) CK1#(CK0#) CK2(DU) CK2#(DU) NC5 NC(RESET#) CKE0 CKE1 CAS# RAS# VREF SLAVE ADDRESS = 1010001B DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 DM8 157 158 71 163 H0_DR_-MCS0 <11> H0_DR_-MCS1 <11> 5 14 25 36 56 67 78 86 47 H0_DR_MDQS18 H0_DR_MDQS19 H0_DR_MDQS20 H0_DR_MDQS21 H0_DR_MDQS22 H0_DR_MDQS23 H0_DR_MDQS24 H0_DR_MDQS25 H0_DR_MDQS26 167 H0_DR_MAA13 <9,10,11> 48 43 41 130 37 32 125 29 122 27 141 118 115 103 H0_DR_MAA0 H0_DR_MAA1 H0_DR_MAA2 H0_DR_MAA3 H0_DR_MAA4 H0_DR_MAA5 H0_DR_MAA6 H0_DR_MAA7 H0_DR_MAA8 H0_DR_MAA9 H0_DR_MAA10 H0_DR_MAA11 H0_DR_MAA12 59 52 113 92 91 181 182 183 <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> H0_DR_MEMBAKA0 <9,10,11> H0_DR_MEMBAKA1 <9,10,11> SMB_MEM_CLK SMB_MEM_DATA VC C _ DDR 44 45 49 51 134 135 142 144 H0_DR_MEMCHECK8 <9,10,11> H0_DR_MEMCHECK9 <9,10,11> H0_DR_MEMCHECK10 <9,10,11> H0_DR_MEMCHECK11 <9,10,11> H0_DR_MEMCHECK12 <9,10,11> H0_DR_MEMCHECK13 <9,10,11> H0_DR_MEMCHECK14 <9,10,11> H0_DR_MEMCHECK15 <9,10,11> 16 17 137 138 76 75 H0_MEMCLK_H2 <4> H0_MEMCLK_L2 <4> 173 10 21 111 65 154 C H0_MEMRESET_L <4,9,10> H0_DR_MCKELO H0_DR_MCKEUP B H0_DR_-MSCASA <9,10,11> H0_DR_-MSRASA <9,10,11> 97 107 119 129 149 159 169 177 140 H0_DR_MDQS27 H0_DR_MDQS28 H0_DR_MDQS29 H0_DR_MDQS30 H0_DR_MDQS31 H0_DR_MDQS32 H0_DR_MDQS33 H0_DR_MDQS34 H0_DR_MDQS35 <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> <9,10,11> 3 11 18 26 34 42 50 58 66 74 81 89 93 100 116 124 132 139 145 152 160 176 9 NC2 101 NC3 102 1000P/50V/X7RNC4 184 82 VDDID CS0# CS1# CS2# CS3# WP(NC) WE# D DR2001 DDRDIMM_184 VDDSPD VDD0 VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDDQ0 VDDQ1 VDDQ2 VDDQ3 VDDQ4 VDDQ5 VDDQ6 VDDQ7 VDDQ8 VDDQ9 VDDQ10 VDDQ11 VDDQ12 VDDQ13 VDDQ14 VDDQ15 5 14 25 36 56 67 78 86 47 <9,10,11> H0_DR_MD[127..64] 184 PIN BA0 BA1 BA2 SCL SDA SA0 SA1 SA2 H0_DR_-MCS0 <11> H0_DR_-MCS1 <11> DDR DIMM SOCKET A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10_AP A11 A12 A13 PIN DDR DIMM SOCKET 184 FETEN WP(NC) WE# 9 NC2 101 NC3 102 1000P/50V/X7RNC4 7 38 46 70 85 108 120 148 168 22 30 54 62 77 96 104 112 128 136 143 156 164 172 180 15 184 82 DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 DQS8 157 158 71 163 3 11 18 26 34 42 50 58 66 74 81 89 93 100 116 124 132 139 145 152 160 176 VC C _ DDR C2016 CS0# CS1# CS2# CS3# VSS0 VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 VSS21 B DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 VDDID VDD0 VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDDQ0 VDDQ1 VDDQ2 VDDQ3 VDDQ4 VDDQ5 VDDQ6 VDDQ7 VDDQ8 VDDQ9 VDDQ10 VDDQ11 VDDQ12 VDDQ13 VDDQ14 VDDQ15 C 2 4 6 8 94 95 98 99 12 13 19 20 105 106 109 110 23 24 28 31 114 117 121 123 33 35 39 40 126 127 131 133 53 55 57 60 146 147 150 151 61 64 68 69 153 155 161 162 72 73 79 80 165 166 170 171 83 84 87 88 174 175 178 179 VSS0 VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 VSS21 H0_DR_M D0 H0_DR_M D1 H0_DR_M D2 H0_DR_M D3 H0_DR_M D4 H0_DR_M D5 H0_DR_M D6 H0_DR_M D7 H0_DR_M D8 H0_DR_M D9 H0_DR_M D10 H0_DR_M D11 H0_DR_M D12 H0_DR_M D13 H0_DR_M D14 H0_DR_M D15 H0_DR_M D16 H0_DR_M D17 H0_DR_M D18 H0_DR_M D19 H0_DR_M D20 H0_DR_M D21 H0_DR_M D22 H0_DR_M D23 H0_DR_M D24 H0_DR_M D25 H0_DR_M D26 H0_DR_M D27 H0_DR_M D28 H0_DR_M D29 H0_DR_M D30 H0_DR_M D31 H0_DR_M D32 H0_DR_M D33 H0_DR_M D34 H0_DR_M D35 H0_DR_M D36 H0_DR_M D37 H0_DR_M D38 H0_DR_M D39 H0_DR_M D40 H0_DR_M D41 H0_DR_M D42 H0_DR_M D43 H0_DR_M D44 H0_DR_M D45 H0_DR_M D46 H0_DR_M D47 H0_DR_M D48 H0_DR_M D49 H0_DR_M D50 H0_DR_M D51 H0_DR_M D52 H0_DR_M D53 H0_DR_M D54 H0_DR_M D55 H0_DR_M D56 H0_DR_M D57 H0_DR_M D58 H0_DR_M D59 H0_DR_M D60 H0_DR_M D61 H0_DR_M D62 H0_DR_M D63 <9,10,11> H0_DR_MD[63..0] DDR2000 DDRDIMM_184 VDDSPD 7 38 46 70 85 108 120 148 168 22 30 54 62 77 96 104 112 128 136 143 156 164 172 180 15 VC C _ DDR VC C _ DDR A D D R _ VREF R2013 100RST C2033 R2007 100RST C2014 0.1u 0.1u C2015 1000P/50V/X7R A Micro Star Restricted Secret Title http://laptop-motherboard-schematic.blogspot.com/ R ev CPU0 Register DDR DIMM1 & 2 Document Number 5 4 3 2 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 8 44 5 4 3 2 1 Registered DDR333 SDRAM Sockets Channel B Channel A VCC_DDR VCC_DDR <8,10,11> H0_DR_-MSWEA 1 DDR_VREF C2036 1000P/50V/X7R FETEN 167 H0_DR_MAA13 <8,10,11> A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10_AP A11 A12 A13 48 43 41 130 37 32 125 29 122 27 141 118 115 103 H0_DR_MAA0 H0_DR_MAA1 H0_DR_MAA2 H0_DR_MAA3 H0_DR_MAA4 H0_DR_MAA5 H0_DR_MAA6 H0_DR_MAA7 H0_DR_MAA8 H0_DR_MAA9 H0_DR_MAA10 H0_DR_MAA11 H0_DR_MAA12 BA0 BA1 BA2 SCL SDA SA0 SA1 SA2 59 52 113 92 91 181 182 183 CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7 44 45 49 51 134 135 142 144 H0_DR_MEMCHECK0 H0_DR_MEMCHECK1 H0_DR_MEMCHECK2 H0_DR_MEMCHECK3 H0_DR_MEMCHECK4 H0_DR_MEMCHECK5 H0_DR_MEMCHECK6 H0_DR_MEMCHECK7 CK0(DU) CK0#(DU) CK1(CK0) CK1#(CK0#) CK2(DU) CK2#(DU) 16 17 137 138 76 75 H0_MEMCLK_H1 <4> H0_MEMCLK_L1 <4> NC5 NC(RESET#) 173 10 H0_MEMRESET_L <4,8,10> CKE0 CKE1 CAS# RAS# 21 111 65 154 H0_DR_MCKELO H0_DR_MCKEUP H0_DR_-MSCASA H0_DR_-MSRASA DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 DM8 97 107 119 129 149 159 169 177 140 VREF SLAVE ADDRESS = 1010010B <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> H0_DR_MEMBAKA0 <8,10,11> H0_DR_MEMBAKA1 <8,10,11> SMB_MEM_CLK SMB_MEM_DATA VCC_DDR <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> H0_DR_MDQS9 <8,10,11> H0_DR_MDQS10 <8,10,11> H0_DR_MDQS11 <8,10,11> H0_DR_MDQS12 <8,10,11> H0_DR_MDQS13 <8,10,11> H0_DR_MDQS14 <8,10,11> H0_DR_MDQS15 <8,10,11> H0_DR_MDQS16 <8,10,11> H0_DR_MDQS17 <8,10,11> 90 63 <8,10,11> H0_DR_-MSWEA 1 DDR_VREF C2035 1000P/50V/X7R 2 4 6 8 94 95 98 99 12 13 19 20 105 106 109 110 23 24 28 31 114 117 121 123 33 35 39 40 126 127 131 133 53 55 57 60 146 147 150 151 61 64 68 69 153 155 161 162 72 73 79 80 165 166 170 171 83 84 87 88 174 175 178 179 C2047 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 82 184 VDDID 157 158 71 163 H0_DR_-MCS2 <11> H0_DR_-MCS3 <11> DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 DQS8 5 14 25 36 56 67 78 86 47 H0_DR_MDQS18 H0_DR_MDQS19 H0_DR_MDQS20 H0_DR_MDQS21 H0_DR_MDQS22 H0_DR_MDQS23 H0_DR_MDQS24 H0_DR_MDQS25 H0_DR_MDQS26 FETEN 167 H0_DR_MAA13 <8,10,11> A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10_AP A11 A12 A13 48 43 41 130 37 32 125 29 122 27 141 118 115 103 H0_DR_MAA0 H0_DR_MAA1 H0_DR_MAA2 H0_DR_MAA3 H0_DR_MAA4 H0_DR_MAA5 H0_DR_MAA6 H0_DR_MAA7 H0_DR_MAA8 H0_DR_MAA9 H0_DR_MAA10 H0_DR_MAA11 H0_DR_MAA12 BA0 BA1 BA2 SCL SDA SA0 SA1 SA2 59 52 113 92 91 181 182 183 CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7 44 45 49 51 134 135 142 144 H0_DR_MEMCHECK8 <8,10,11> H0_DR_MEMCHECK9 <8,10,11> H0_DR_MEMCHECK10 <8,10,11> H0_DR_MEMCHECK11 <8,10,11> H0_DR_MEMCHECK12 <8,10,11> H0_DR_MEMCHECK13 <8,10,11> H0_DR_MEMCHECK14 <8,10,11> H0_DR_MEMCHECK15 <8,10,11> CK0(DU) CK0#(DU) CK1(CK0) CK1#(CK0#) CK2(DU) CK2#(DU) 16 17 137 138 76 75 H0_MEMCLK_H3 <4> H0_MEMCLK_L3 <4> NC5 NC(RESET#) 173 10 CKE0 CKE1 CAS# RAS# 21 111 65 154 DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 DM8 97 107 119 129 149 159 169 177 140 WP(NC) WE# VREF 9 NC2 101 NC3 102 1000P/50V/X7RNC4 VCC_DDR CS0# CS1# CS2# CS3# DDR DIMM SOCKET 184 PIN H0_DR_MDQS0 H0_DR_MDQS1 H0_DR_MDQS2 H0_DR_MDQS3 H0_DR_MDQS4 H0_DR_MDQS5 H0_DR_MDQS6 H0_DR_MDQS7 H0_DR_MDQS8 H0_DR_MD64 H0_DR_MD65 H0_DR_MD66 H0_DR_MD67 H0_DR_MD68 H0_DR_MD69 H0_DR_MD70 H0_DR_MD71 H0_DR_MD72 H0_DR_MD73 H0_DR_MD74 H0_DR_MD75 H0_DR_MD76 H0_DR_MD77 H0_DR_MD78 H0_DR_MD79 H0_DR_MD80 H0_DR_MD81 H0_DR_MD82 H0_DR_MD83 H0_DR_MD84 H0_DR_MD85 H0_DR_MD86 H0_DR_MD87 H0_DR_MD88 H0_DR_MD89 H0_DR_MD90 H0_DR_MD91 H0_DR_MD92 H0_DR_MD93 H0_DR_MD94 H0_DR_MD95 H0_DR_MD96 H0_DR_MD97 H0_DR_MD98 H0_DR_MD99 H0_DR_MD100 H0_DR_MD101 H0_DR_MD102 H0_DR_MD103 H0_DR_MD104 H0_DR_MD105 H0_DR_MD106 H0_DR_MD107 H0_DR_MD108 H0_DR_MD109 H0_DR_MD110 H0_DR_MD111 H0_DR_MD112 H0_DR_MD113 H0_DR_MD114 H0_DR_MD115 H0_DR_MD116 H0_DR_MD117 H0_DR_MD118 H0_DR_MD119 H0_DR_MD120 H0_DR_MD121 H0_DR_MD122 H0_DR_MD123 H0_DR_MD124 H0_DR_MD125 H0_DR_MD126 H0_DR_MD127 <8,10,11> H0_DR_MD[127..64] VDDSPD 7 38 46 70 85 108 120 148 168 22 30 54 62 77 96 104 112 128 136 143 156 164 172 180 15 VDD0 VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDDQ0 VDDQ1 VDDQ2 VDDQ3 VDDQ4 VDDQ5 VDDQ6 VDDQ7 VDDQ8 VDDQ9 VDDQ10 VDDQ11 VDDQ12 VDDQ13 VDDQ14 VDDQ15 82 5 14 25 36 56 67 78 86 47 WP(NC) WE# 9 NC2 101 NC3 102 1000P/50V/X7RNC4 184 DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 DQS8 DDR DIMM SOCKET 184 PIN H0_DR_-MCS2 <11> H0_DR_-MCS3 <11> 3 11 18 26 34 42 50 58 66 74 81 89 93 100 116 124 132 139 145 152 160 176 VCC_DDR C2025 157 158 71 163 SLAVE ADDRESS = 1010011B VSS0 VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 VSS21 90 63 CS0# CS1# CS2# CS3# D DDR2003 DDRDIMM_184 <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> C H0_DR_MEMBAKA0 <8,10,11> H0_DR_MEMBAKA1 <8,10,11> SMB_MEM_CLK SMB_MEM_DATA SMB_MEM_CLK <8,10,17> SMB_MEM_DATA <8,10,17> VCC_DDR B H0_MEMRESET_L <4,8,10> H0_DR_MCKELO H0_DR_MCKEUP H0_DR_-MSCASA <8,10,11> H0_DR_-MSRASA <8,10,11> H0_DR_MDQS27 H0_DR_MDQS28 H0_DR_MDQS29 H0_DR_MDQS30 H0_DR_MDQS31 H0_DR_MDQS32 H0_DR_MDQS33 H0_DR_MDQS34 H0_DR_MDQS35 <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> <8,10,11> 3 11 18 26 34 42 50 58 66 74 81 89 93 100 116 124 132 139 145 152 160 176 B DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 VSS0 VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 VSS21 C 2 4 6 8 94 95 98 99 12 13 19 20 105 106 109 110 23 24 28 31 114 117 121 123 33 35 39 40 126 127 131 133 53 55 57 60 146 147 150 151 61 64 68 69 153 155 161 162 72 73 79 80 165 166 170 171 83 84 87 88 174 175 178 179 VDDID VDD0 VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDDQ0 VDDQ1 VDDQ2 VDDQ3 VDDQ4 VDDQ5 VDDQ6 VDDQ7 VDDQ8 VDDQ9 VDDQ10 VDDQ11 VDDQ12 VDDQ13 VDDQ14 VDDQ15 H0_DR_MD0 H0_DR_MD1 H0_DR_MD2 H0_DR_MD3 H0_DR_MD4 H0_DR_MD5 H0_DR_MD6 H0_DR_MD7 H0_DR_MD8 H0_DR_MD9 H0_DR_MD10 H0_DR_MD11 H0_DR_MD12 H0_DR_MD13 H0_DR_MD14 H0_DR_MD15 H0_DR_MD16 H0_DR_MD17 H0_DR_MD18 H0_DR_MD19 H0_DR_MD20 H0_DR_MD21 H0_DR_MD22 H0_DR_MD23 H0_DR_MD24 H0_DR_MD25 H0_DR_MD26 H0_DR_MD27 H0_DR_MD28 H0_DR_MD29 H0_DR_MD30 H0_DR_MD31 H0_DR_MD32 H0_DR_MD33 H0_DR_MD34 H0_DR_MD35 H0_DR_MD36 H0_DR_MD37 H0_DR_MD38 H0_DR_MD39 H0_DR_MD40 H0_DR_MD41 H0_DR_MD42 H0_DR_MD43 H0_DR_MD44 H0_DR_MD45 H0_DR_MD46 H0_DR_MD47 H0_DR_MD48 H0_DR_MD49 H0_DR_MD50 H0_DR_MD51 H0_DR_MD52 H0_DR_MD53 H0_DR_MD54 H0_DR_MD55 H0_DR_MD56 H0_DR_MD57 H0_DR_MD58 H0_DR_MD59 H0_DR_MD60 H0_DR_MD61 H0_DR_MD62 H0_DR_MD63 <8,10,11> H0_DR_MD[63..0] DDR2002 DDRDIMM_184 VDDSPD 7 38 46 70 85 108 120 148 168 22 30 54 62 77 96 104 112 128 136 143 156 164 172 180 15 D DDR_VREF A A C2038 C2030 1000P/50V/X7R 0.1u Micro Star Restricted Secret Title CPU0 Register DDR DIMM3,4 Document Number http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 2 R ev 1 Last Revision Date: Tuesday, February 15, 2005 Sheet 9 44 of 5 4 3 2 1 Registered DDR333 SDRAM Sockets Channel B Channel A VCC_DDR VCC_DDR <8,9,11> H0_DR_-MSWEA 1 DDR_VREF C1049 1000P/50V/X7R 167 H0_DR_MAA13 <8,9,11> A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10_AP A11 A12 A13 48 43 41 130 37 32 125 29 122 27 141 118 115 103 H0_DR_MAA0 H0_DR_MAA1 H0_DR_MAA2 H0_DR_MAA3 H0_DR_MAA4 H0_DR_MAA5 H0_DR_MAA6 H0_DR_MAA7 H0_DR_MAA8 H0_DR_MAA9 H0_DR_MAA10 H0_DR_MAA11 H0_DR_MAA12 BA0 BA1 BA2 SCL SDA SA0 SA1 SA2 59 52 113 92 91 181 182 183 CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7 44 45 49 51 134 135 142 144 CK0(DU) CK0#(DU) CK1(CK0) CK1#(CK0#) CK2(DU) CK2#(DU) 16 17 137 138 76 75 NC5 NC(RESET#) 173 10 H0_MEMRESET_L <4,8,9> CKE0 CKE1 CAS# RAS# 21 111 65 154 H0_DR_MCKELO H0_DR_MCKEUP H0_DR_-MSCASA H0_DR_-MSRASA DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 DM8 97 107 119 129 149 159 169 177 140 VREF SLAVE ADDRESS = 1010100B <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> H0_DR_MEMBAKA0 <8,9,11> H0_DR_MEMBAKA1 <8,9,11> SMB_MEM_CLK SMB_MEM_DATA SMB_MEM_CLK <8,9,17> SMB_MEM_DATA <8,9,17> VCC_DDR H0_DR_MEMCHECK0 H0_DR_MEMCHECK1 H0_DR_MEMCHECK2 H0_DR_MEMCHECK3 H0_DR_MEMCHECK4 H0_DR_MEMCHECK5 H0_DR_MEMCHECK6 H0_DR_MEMCHECK7 H0_MEMCLK_H4 H0_MEMCLK_L4 <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> H0_MEMCLK_H4 <4> H0_MEMCLK_L4 <4> <8,9,11> <8,9,11> <8,9,11> <8,9,11> H0_DR_MDQS9 <8,9,11> H0_DR_MDQS10 <8,9,11> H0_DR_MDQS11 <8,9,11> H0_DR_MDQS12 <8,9,11> H0_DR_MDQS13 <8,9,11> H0_DR_MDQS14 <8,9,11> H0_DR_MDQS15 <8,9,11> H0_DR_MDQS16 <8,9,11> H0_DR_MDQS17 <8,9,11> 90 63 <8,9,11> H0_DR_-MSWEA 1 DDR_VREF C1051 1000P/50V/X7R C1052 DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 VCC_DDR 82 184 VDDID 157 158 71 163 DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 DQS8 5 14 25 36 56 67 78 86 47 H0_DR_MDQS18 H0_DR_MDQS19 H0_DR_MDQS20 H0_DR_MDQS21 H0_DR_MDQS22 H0_DR_MDQS23 H0_DR_MDQS24 H0_DR_MDQS25 H0_DR_MDQS26 FETEN 167 H0_DR_MAA13 <8,9,11> A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10_AP A11 A12 A13 48 43 41 130 37 32 125 29 122 27 141 118 115 103 H0_DR_MAA0 H0_DR_MAA1 H0_DR_MAA2 H0_DR_MAA3 H0_DR_MAA4 H0_DR_MAA5 H0_DR_MAA6 H0_DR_MAA7 H0_DR_MAA8 H0_DR_MAA9 H0_DR_MAA10 H0_DR_MAA11 H0_DR_MAA12 BA0 BA1 BA2 SCL SDA SA0 SA1 SA2 59 52 113 92 91 181 182 183 CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7 44 45 49 51 134 135 142 144 CK0(DU) CK0#(DU) CK1(CK0) CK1#(CK0#) CK2(DU) CK2#(DU) 16 17 137 138 76 75 NC5 NC(RESET#) 173 10 CKE0 CKE1 CAS# RAS# 21 111 65 154 DM0 DM1 DM2 DM3 DM4 DM5 DM6 DM7 DM8 97 107 119 129 149 159 169 177 140 WP(NC) WE# VREF 9 NC2 101 NC3 102 1000P/50V/X7RNC4 H0_DR_-MCS4 H0_DR_-MCS5 CS0# CS1# CS2# CS3# DDR DIMM SOCKET 184 PIN FETEN <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> 2 4 6 8 94 95 98 99 12 13 19 20 105 106 109 110 23 24 28 31 114 117 121 123 33 35 39 40 126 127 131 133 53 55 57 60 146 147 150 151 61 64 68 69 153 155 161 162 72 73 79 80 165 166 170 171 83 84 87 88 174 175 178 179 VDDSPD 7 38 46 70 85 108 120 148 168 22 30 54 62 77 96 104 112 128 136 143 156 164 172 180 15 VDD0 VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDDQ0 VDDQ1 VDDQ2 VDDQ3 VDDQ4 VDDQ5 VDDQ6 VDDQ7 VDDQ8 VDDQ9 VDDQ10 VDDQ11 VDDQ12 VDDQ13 VDDQ14 VDDQ15 82 H0_DR_MDQS0 H0_DR_MDQS1 H0_DR_MDQS2 H0_DR_MDQS3 H0_DR_MDQS4 H0_DR_MDQS5 H0_DR_MDQS6 H0_DR_MDQS7 H0_DR_MDQS8 WP(NC) WE# 9 NC2 101 NC3 102 1000P/50V/X7RNC4 184 5 14 25 36 56 67 78 86 47 DDR DIMM SOCKET 184 PIN DQS0 DQS1 DQS2 DQS3 DQS4 DQS5 DQS6 DQS7 DQS8 H0_DR_MD64 H0_DR_MD65 H0_DR_MD66 H0_DR_MD67 H0_DR_MD68 H0_DR_MD69 H0_DR_MD70 H0_DR_MD71 H0_DR_MD72 H0_DR_MD73 H0_DR_MD74 H0_DR_MD75 H0_DR_MD76 H0_DR_MD77 H0_DR_MD78 H0_DR_MD79 H0_DR_MD80 H0_DR_MD81 H0_DR_MD82 H0_DR_MD83 H0_DR_MD84 H0_DR_MD85 H0_DR_MD86 H0_DR_MD87 H0_DR_MD88 H0_DR_MD89 H0_DR_MD90 H0_DR_MD91 H0_DR_MD92 H0_DR_MD93 H0_DR_MD94 H0_DR_MD95 H0_DR_MD96 H0_DR_MD97 H0_DR_MD98 H0_DR_MD99 H0_DR_MD100 H0_DR_MD101 H0_DR_MD102 H0_DR_MD103 H0_DR_MD104 H0_DR_MD105 H0_DR_MD106 H0_DR_MD107 H0_DR_MD108 H0_DR_MD109 H0_DR_MD110 H0_DR_MD111 H0_DR_MD112 H0_DR_MD113 H0_DR_MD114 H0_DR_MD115 H0_DR_MD116 H0_DR_MD117 H0_DR_MD118 H0_DR_MD119 H0_DR_MD120 H0_DR_MD121 H0_DR_MD122 H0_DR_MD123 H0_DR_MD124 H0_DR_MD125 H0_DR_MD126 H0_DR_MD127 <8,9,11> H0_DR_MD[127..64] H0_DR_-MCS4 <11> H0_DR_-MCS5 <11> 3 11 18 26 34 42 50 58 66 74 81 89 93 100 116 124 132 139 145 152 160 176 VCC_DDR C1050 157 158 71 163 SLAVE ADDRESS = 1010101B VSS0 VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 VSS21 90 63 H0_DR_-MCS4 H0_DR_-MCS5 CS0# CS1# CS2# CS3# D DDR6 DDRDIMM_184 H0_DR_-MCS4 <11> H0_DR_-MCS5 <11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> C H0_DR_MEMBAKA0 <8,9,11> H0_DR_MEMBAKA1 <8,9,11> SMB_MEM_CLK SMB_MEM_DATA SMB_MEM_CLK <8,9,17> SMB_MEM_DATA <8,9,17> VCC_DDR VCC_DDR H0_DR_MEMCHECK8 <8,9,11> H0_DR_MEMCHECK9 <8,9,11> H0_DR_MEMCHECK10 <8,9,11> H0_DR_MEMCHECK11 <8,9,11> H0_DR_MEMCHECK12 <8,9,11> H0_DR_MEMCHECK13 <8,9,11> H0_DR_MEMCHECK14 <8,9,11> H0_DR_MEMCHECK15 <8,9,11> H0_MEMCLK_H5 H0_MEMCLK_L5 H0_MEMCLK_H5 <4> H0_MEMCLK_L5 <4> B H0_MEMRESET_L <4,8,9> H0_DR_MCKELO H0_DR_MCKEUP H0_DR_-MSCASA <8,9,11> H0_DR_-MSRASA <8,9,11> H0_DR_MDQS27 H0_DR_MDQS28 H0_DR_MDQS29 H0_DR_MDQS30 H0_DR_MDQS31 H0_DR_MDQS32 H0_DR_MDQS33 H0_DR_MDQS34 H0_DR_MDQS35 <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> <8,9,11> 3 11 18 26 34 42 50 58 66 74 81 89 93 100 116 124 132 139 145 152 160 176 B DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 DQ16 DQ17 DQ18 DQ19 DQ20 DQ21 DQ22 DQ23 DQ24 DQ25 DQ26 DQ27 DQ28 DQ29 DQ30 DQ31 DQ32 DQ33 DQ34 DQ35 DQ36 DQ37 DQ38 DQ39 DQ40 DQ41 DQ42 DQ43 DQ44 DQ45 DQ46 DQ47 DQ48 DQ49 DQ50 DQ51 DQ52 DQ53 DQ54 DQ55 DQ56 DQ57 DQ58 DQ59 DQ60 DQ61 DQ62 DQ63 VSS0 VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 VSS10 VSS11 VSS12 VSS13 VSS14 VSS15 VSS16 VSS17 VSS18 VSS19 VSS20 VSS21 C 2 4 6 8 94 95 98 99 12 13 19 20 105 106 109 110 23 24 28 31 114 117 121 123 33 35 39 40 126 127 131 133 53 55 57 60 146 147 150 151 61 64 68 69 153 155 161 162 72 73 79 80 165 166 170 171 83 84 87 88 174 175 178 179 VDDID VDD0 VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDDQ0 VDDQ1 VDDQ2 VDDQ3 VDDQ4 VDDQ5 VDDQ6 VDDQ7 VDDQ8 VDDQ9 VDDQ10 VDDQ11 VDDQ12 VDDQ13 VDDQ14 VDDQ15 H0_DR_MD0 H0_DR_MD1 H0_DR_MD2 H0_DR_MD3 H0_DR_MD4 H0_DR_MD5 H0_DR_MD6 H0_DR_MD7 H0_DR_MD8 H0_DR_MD9 H0_DR_MD10 H0_DR_MD11 H0_DR_MD12 H0_DR_MD13 H0_DR_MD14 H0_DR_MD15 H0_DR_MD16 H0_DR_MD17 H0_DR_MD18 H0_DR_MD19 H0_DR_MD20 H0_DR_MD21 H0_DR_MD22 H0_DR_MD23 H0_DR_MD24 H0_DR_MD25 H0_DR_MD26 H0_DR_MD27 H0_DR_MD28 H0_DR_MD29 H0_DR_MD30 H0_DR_MD31 H0_DR_MD32 H0_DR_MD33 H0_DR_MD34 H0_DR_MD35 H0_DR_MD36 H0_DR_MD37 H0_DR_MD38 H0_DR_MD39 H0_DR_MD40 H0_DR_MD41 H0_DR_MD42 H0_DR_MD43 H0_DR_MD44 H0_DR_MD45 H0_DR_MD46 H0_DR_MD47 H0_DR_MD48 H0_DR_MD49 H0_DR_MD50 H0_DR_MD51 H0_DR_MD52 H0_DR_MD53 H0_DR_MD54 H0_DR_MD55 H0_DR_MD56 H0_DR_MD57 H0_DR_MD58 H0_DR_MD59 H0_DR_MD60 H0_DR_MD61 H0_DR_MD62 H0_DR_MD63 <8,9,11> H0_DR_MD[63..0] DDR5 DDRDIMM_184 VDDSPD 7 38 46 70 85 108 120 148 168 22 30 54 62 77 96 104 112 128 136 143 156 164 172 180 15 D DDR_VREF A A C1053 C1054 1000P/50V/X7R 0.1u Micro Star Restricted Secret Title CPU0 Register DDR DIMM3,4 Document Number http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 2 R ev 1 Last Revision Date: Tuesday, February 15, 2005 Sheet 10 44 of 5 4 3 2 DDR Terminations 1 LAYOUT: Locate close to Sledgehammer socket. LAYOUT: Locate close to Clawhammer socket. VTT_DDR VTT_DDR CT2008 CT2002 VTT_DDR H0 _ MD4 H0 _ MD0 H0 _ MD5 H0 _ MD1 D H0 _ MDQS9 H0 _ MDQS0 H0 _ MD6 H0 _ MD2 H0 _ MD7 H0 _ MD3 H0 _ MD8 H0 _ MD12 H0 _ MD9 H0 _ MD13 H0 _ MDQS1 H0 _ MDQS10 H0 _ MD14 H0 _ MD15 H0 _ MD10 H0 _ MD11 RN2015 1 3 5 7 RN2017 H0 _ MD17 1 H0 _ MD21 3 H0 _ MDQS2 5 H0 _ MDQS11 7 RN2019 H0_MAA12 1 H0_MAA11 3 H0_MAA9 5 H0_MAA7 7 RN2021 H0 _ MD18 1 H0 _ MD22 3 H0 _ MD23 5 H0 _ MD19 7 RN2028 H0 _ MD24 1 H0 _ MD28 3 H0 _ MD29 5 H0 _ MD25 7 RN2030 H0 _ MDQS3 1 H0 _ MDQS12 3 H0 _ MD30 5 H0 _ MD26 7 RN2032 H0_MAA3 1 H0_MAA2 3 H0_MAA1 5 7 RN2034 H0 _ MD27 1 H0 _ MD31 3 H0 _ ME MCHECK4 5 H0 _ ME MCHECK5 7 RN2036 H0 _ ME MCHECK0 1 H0 _ ME MCHECK1 3 H0 _ MDQS8 5 H0 _ MDQS17 7 RN2037 H0 _ ME MCHECK2 1 H0 _ ME MCHECK6 3 H0 _ ME MCHECK3 5 H0 _ ME MCHECK7 7 RN2039 H0 _ MD32 1 H0 _ MD36 3 H0 _ MD37 5 H0 _ MD33 7 RN2042 H0 _ MDQS4 1 H0 _ MDQS13 3 H0 _ MD34 5 H0 _ MD38 7 RN2044 H0 _ MD39 1 H0 _ MD35 3 H0 _ MD44 5 H0 _ MD40 7 RN2048 H0 _ MD45 1 H0 _ MD41 3 H0 _ MDQS14 5 H0 _ MDQS5 7 RN2051 H0 _ MD42 1 H0 _ MD46 3 H0 _ MD43 5 H0 _ MD47 7 RN2049 H0 _ -MCS1 1 H0 _ -MCS2 3 H0 _ -MCS3 5 H0_MAA13 7 RN2053 H0 _ MD48 1 H0 _ MD52 3 H0 _ MD49 5 H0 _ MD53 7 RN2055 H0 _ MDQS15 1 H0 _ MD54 3 H0 _ MDQS6 5 H0 _ MD55 7 RN2057 H0 _ MD50 1 H0 _ MD51 3 H0 _ MD60 5 H0 _ MD61 7 RN2059 H0 _ MD56 1 H0 _ MD57 3 H0 _ MDQS16 5 H0 _ MD62 7 RN2061 H0 _ MDQS7 1 H0 _ MD63 3 H0 _ MD58 5 H0 _ MD59 7 H0 _ MCKEUP H0 _ MCKELO H0 _ MD20 H0 _ MD16 C B RN2002 1 3 5 7 RN2005 1 3 5 7 RN2007 1 3 5 7 RN2009 1 3 5 7 RN2012 1 3 5 7 22_8P4R H0 _ D R _MD4 2 H0 _ D R _MD0 4 H0 _ D R _MD5 6 H0 _ D R _MD1 8 10_8P4R H0 _ D R _MDQS9 2 H0 _ D R _MDQS0 4 H0 _ D R _MD6 6 H0 _ D R _MD2 8 10_8P4R H0 _ D R _MD7 2 H0 _ D R _MD3 4 H0 _ D R _MD8 6 H0 _ D R _MD12 8 10_8P4R H0 _ D R _MD9 2 H0 _ D R _MD13 4 H0 _ D R _MDQS1 6 H0 _ D R _MDQS10 8 10_8P4R H0 _ D R _MD14 2 H0 _ D R _MD15 4 H0 _ D R _MD10 6 H0 _ D R _MD11 8 10_8P4R H0 _ D R _ MCKEUP 2 H0 _ DR_MCKELO 4 H0 _ D R _MD20 6 H0 _ D R _MD16 8 10_8P4R H0 _ D R _MD17 2 H0 _ D R _MD21 4 H0 _ D R _MDQS2 6 H0 _ D R _MDQS11 8 10_8P4R H0 _ DR_MAA12 2 H0 _ DR_MAA11 4 H0 _ DR_MAA9 6 H0 _ DR_MAA7 8 10_8P4R H0 _ D R _MD18 2 H0 _ D R _MD22 4 H0 _ D R _MD23 6 H0 _ D R _MD19 8 10_8P4R H0 _ D R _MD24 2 H0 _ D R _MD28 4 H0 _ D R _MD29 6 H0 _ D R _MD25 8 10_8P4R H0 _ D R _MDQS3 2 H0 _ D R _MDQS12 4 H0 _ D R _MD30 6 H0 _ D R _MD26 8 10_8P4R H0 _ DR_MAA3 2 H0 _ DR_MAA2 4 H0 _ DR_MAA1 6 8 10_8P4R H0 _ D R _MD27 2 H0 _ D R _MD31 4 H0 _ DR_ ME MCHECK4 6 H0 _ DR_ ME MCHECK5 8 10_8P4R H0 _ DR_ ME MCHECK0 2 4 H0 _ DR_ ME MCHECK1 6 H0 _ D R _MDQS8 8 H0 _ D R _MDQS17 10_8P4R 2 H0 _ DR_ ME MCHECK2 4 H0 _ DR_ ME MCHECK6 6 H0 _ DR_ ME MCHECK3 8 H0 _ DR_ ME MCHECK7 10_8P4R H0 _ D R _MD32 2 H0 _ D R _MD36 4 H0 _ D R _MD37 6 H0 _ D R _MD33 8 10_8P4R 2 H0 _ D R _MDQS4 4 H0 _ D R _MDQS13 H0 _ D R _MD34 6 H0 _ D R _MD38 8 10_8P4R H0 _ D R _MD39 2 H0 _ D R _MD35 4 H0 _ D R _MD44 6 H0 _ D R _MD40 8 10_8P4R H0 _ D R _MD45 2 H0 _ D R _MD41 4 6 H0 _ D R _MDQS14 8 H0 _ D R _MDQS5 10_8P4R H0 _ D R _MD42 2 H0 _ D R _MD46 4 H0 _ D R _MD43 6 H0 _ D R _MD47 8 10_8P4R H0 _ DR_-MCS1 2 H0 _ DR_-MCS2 4 H0 _ DR_-MCS3 6 H0 _ DR_MAA13 8 10_8P4R H0 _ D R _MD48 2 H0 _ D R _MD52 4 H0 _ D R _MD49 6 H0 _ D R _MD53 8 10_8P4R 2 H0 _ D R _MDQS15 H0 _ D R _MD54 4 6 H0 _ D R _MDQS6 H0 _ D R _MD55 8 10_8P4R H0 _ D R _MD50 2 H0 _ D R _MD51 4 H0 _ D R _MD60 6 H0 _ D R _MD61 8 10_8P4R H0 _ D R _MD56 2 H0 _ D R _MD57 4 6 H0 _ D R _MDQS16 H0 _ D R _MD62 8 10_8P4R 2 H0 _ D R _MDQS7 H0 _ D R _MD63 4 H0 _ D R _MD58 6 H0 _ D R _MD59 8 RN2001 1 3 5 7 RN2003 H0 _ D R _MDQS9 1 H0 _ D R _MDQS0 3 H0 _ D R _MD6 5 H0 _ D R _MD2 7 RN2006 H0 _ D R _MD7 1 H0 _ D R _MD3 3 H0 _ D R _MD8 5 H0 _ D R _MD12 7 RN2008 H0 _ D R _MD9 1 H0 _ D R _MD13 3 H0 _ D R _MDQS1 5 H0 _ D R _MDQS10 7 RN2011 H0 _ D R _MD14 1 H0 _ D R _MD15 3 H0 _ D R _MD10 5 H0 _ D R _ MCKEUP 7 RN2014 H0 _ D R _MD11 1 H0 _ DR_MCKELO 3 H0 _ D R _MD20 5 H0 _ DR_MAA12 7 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 RN2016 H0 _ D R _MD16 1 H0 _ D R _MD17 3 H0 _ D R _MD21 5 H0 _ D R _MDQS2 7 RN2018 H0 _ DR_MAA11 1 H0 _ DR_MAA9 3 H0 _ D R _MDQS11 5 H0 _ D R _MD18 7 RN2020 H0 _ D R _MD22 1 H0 _ DR_MAA8 3 H0 _ D R _MD23 5 H0 _ D R _MD19 7 RN2023 H0 _ D R _MD24 1 H0 _ D R _MD28 3 H0 _ D R _MD29 5 H0 _ D R _MD25 7 RN2027 H0 _ D R _MDQS3 1 H0 _ D R _MDQS12 3 H0 _ DR_MAA3 5 H0 _ D R _MD30 7 RN2029 H0 _ D R _MD26 1 H0 _ D R _MD27 3 H0 _ DR_MAA2 5 H0 _ D R _MD31 7 RN2031 H0 _ D R _ ME MCHECK4 1 H0 _ D R _ ME MCHECK5 3 H0 _ DR_MAA1 5 H0 _ D R _ ME MCHECK0 7 RN2033 H0 _ D R _ ME MCHECK1 1 H0 _ D R _MDQS8 3 H0 _ DR_MAA0 5 H0 _ D R _MDQS17 7 RN2035 H0 _ DR_MAA10 1 H0 _ D R _ ME MCHECK2 3 H0 _ D R _ ME MCHECK6 5 H0 _ D R _ ME MCHECK3 7 RN2038 H0 _ DR_MEMBAKA1 1 H0 _ D R _ ME MCHECK7 3 H0 _ D R _MD32 5 H0 _ D R _MD36 7 RN2041 H0 _ D R _MD37 1 H0 _ D R _MD33 3 H0 _ D R _MDQS4 5 H0 _ D R _MDQS13 7 RN2043 H0 _ D R _MD34 1 H0 _ D R _MD38 3 H0 _ D R _MD39 5 H0 _ DR_MEMBAKA0 7 RN2045 H0 _ D R _MD35 1 H0 _ D R _MD44 3 H0 _ D R _MD40 5 H0 _ D R _MD45 7 RN2047 H0 _ D R _MD41 1 H0 _ D R _MDQS14 3 H0 _ D R _MDQS5 5 H0 _ D R _MD42 7 RN2050 H0 _ D R _MD46 1 H0 _ D R _MD43 3 H0 _ D R _MD47 5 H0 _ D R _MD48 7 RN2052 H0 _ D R _MD52 1 H0 _ D R _MD49 3 H0 _ D R _MD53 5 H0 _ DR_MAA13 7 RN2054 H0 _ D R _MDQS15 1 H0 _ D R _MD54 3 H0 _ D R _MDQS6 5 H0 _ D R _MD55 7 RN2056 H0 _ D R _MD50 1 H0 _ D R _MD51 3 H0 _ D R _MD60 5 H0 _ D R _MD61 7 RN2058 H0 _ D R _MD56 1 H0 _ D R _MD57 3 H0 _ D R _MDQS16 5 H0 _ D R _MD62 7 RN2060 H0 _ D R _MDQS7 1 H0 _ D R _MD63 3 H0 _ D R _MD58 5 H0 _ D R _MD59 7 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 47_8P4R 2 4 6 8 H0 _ D R _MD4 H0 _ D R _MD0 H0 _ D R _MD5 H0 _ D R _MD1 VTT_DDR RN2108 7 5 3 1 RN2110 H0 _ MDQS27 7 H0 _ MDQS18 5 H0 _ MD70 3 H0 _ MD66 1 RN2112 H0 _ MD71 7 H0 _ MD67 5 H0 _ MD72 3 H0 _ MD76 1 RN2114 H0 _ MD73 7 H0 _ MD77 5 H0 _ MDQS19 3 H0 _ MDQS28 1 RN2116 H0 _ MD78 7 H0 _ MD79 5 H0 _ MD74 3 H0 _ MD75 1 RN2118 H0 _ MD84 7 H0 _ MD80 5 H0 _ MD81 3 H0 _ MD85 1 RN2120 H0 _ MDQS20 7 H0 _ MDQS29 5 H0 _ MD82 3 H0 _ MD86 1 RN2024 H0_MAA8 7 H0_MAA5 5 H0_MAA6 3 H0_MAA4 1 RN2122 H0 _ MD83 7 H0 _ MD87 5 H0 _ MD88 3 H0 _ MD92 1 RN2124 H0 _ MD93 7 H0 _ MD89 5 H0 _ MDQS21 3 H0 _ MDQS30 1 RN2126 H0 _ MD94 7 H0 _ MD90 5 H0 _ MD91 3 H0 _ MD95 1 RN2128 H0 _ ME MCHECK12 7 H0 _ ME MCHECK13 5 H0 _ ME MCHECK8 3 H0 _ ME MCHECK9 1 RN2130 H0 _ MDQS35 7 H0 _ MDQS26 5 H0 _ ME MCHECK10 3 H0 _ ME MCHECK11 1 RN2132 H0_MAA0 7 H0_MAA10 5 H0_MEMBAKA1 3 H0_MEMBAKA0 1 RN2134 H0 _ ME MCHECK14 7 H0 _ ME MCHECK15 5 H0 _ MD96 3 H0_MD100 1 RN2135 H0_MD101 7 H0 _ MD97 5 H0 _ MDQS22 3 H0 _ MD98 1 RN2137 H0 _ MDQS31 7 H0_MD102 5 H0_MD103 3 H0 _ MD99 1 RN2139 H0_MD108 7 H0_MD104 5 H0_MD109 3 H0_MD105 1 RN2046 H0 _ -MSRASA 7 H0 _ -MSWEA 5 H0 _ -MSCASA 3 H0 _ -MCS0 1 H0 _ MD68 H0 _ MD64 H0 _ MD69 H0 _ MD65 <4> H0 _ -MCS4 <4> H0 _ -MCS5 H0_MD106 H0 _ MDQS23 H0 _ MDQS32 H0_MD111 H0_MD107 H0_MD110 H0_MD112 H0_MD113 H0_MD116 H0_MD117 H0 _ MDQS33 H0_MD118 H0 _ MDQS24 H0_MD119 H0_MD114 H0_MD115 H0_MD124 H0_MD125 H0_MD120 H0_MD121 H0 _ MDQS34 H0_MD126 H0 _ MDQS25 H0_MD127 H0_MD122 H0_MD123 1 3 5 7 RN2142 1 3 5 7 R N2 144 7 5 3 1 RN2 146 7 5 3 1 RN2148 7 5 3 1 R N2 150 7 5 3 1 R N2 152 7 5 3 1 (BOT)10_8P4R H0 _ D R _MD68 8 H0 _ D R _MD64 6 H0 _ D R _MD69 4 H0 _ D R _MD65 2 (BOT)10_8P4R H0 _ D R _MDQS27 8 H0 _ D R _MDQS18 6 H0 _ D R _MD70 4 H0 _ D R _MD66 2 (BOT)10_8P4R H0 _ D R _MD71 8 H0 _ D R _MD67 6 H0 _ D R _MD72 4 H0 _ D R _MD76 2 (BOT)10_8P4R H0 _ D R _MD73 8 H0 _ D R _MD77 6 H0 _ D R _MDQS19 4 H0 _ D R _MDQS28 2 (BOT)10_8P4R H0 _ D R _MD78 8 H0 _ D R _MD79 6 H0 _ D R _MD74 4 H0 _ D R _MD75 2 (BOT)10_8P4R H0 _ D R _MD84 8 H0 _ D R _MD80 6 H0 _ D R _MD81 4 H0 _ D R _MD85 2 (BOT)10_8P4R H0 _ D R _MDQS20 8 H0 _ D R _MDQS29 6 H0 _ D R _MD82 4 H0 _ D R _MD86 2 (BOT)10_8P4R H0 _ DR_MAA8 8 H0 _ DR_MAA5 6 H0 _ DR_MAA6 4 H0 _ DR_MAA4 2 (BOT)10_8P4R H0 _ D R _MD83 8 H0 _ D R _MD87 6 H0 _ D R _MD88 4 H0 _ D R _MD92 2 (BOT)10_8P4R H0 _ D R _MD93 8 H0 _ D R _MD89 6 H0 _ D R _MDQS21 4 H0 _ D R _MDQS30 2 (BOT)10_8P4R H0 _ D R _MD94 8 H0 _ D R _MD90 6 H0 _ D R _MD91 4 H0 _ D R _MD95 2 (BOT)10_8P4R 8 H0 _ DR_ ME MCHECK12 6 H0 _ DR_ ME MCHECK13 4 H0 _ DR_ ME MCHECK8 2 H0 _ DR_ ME MCHECK9 (BOT)10_8P4R H0 _ D R _MDQS35 8 H0 _ D R _MDQS26 6 4 H0 _ DR_ ME MCHECK10 2 H0 _ DR_ ME MCHECK11 (BOT)10_8P4R H0 _ DR_MAA0 8 H0 _ DR_MAA10 6 H0 _ DR_MEMBAKA1 4 H0 _ DR_MEMBAKA0 2 (BOT)10_8P4R 8 H0 _ DR_ ME MCHECK14 6 H0 _ DR_ ME MCHECK15 H0 _ D R _MD96 4 H0 _ D R_MD100 2 (BOT)10_8P4R H0 _ D R_MD101 8 H0 _ D R _MD97 6 H0 _ D R _MDQS22 4 H0 _ D R _MD98 2 (BOT)10_8P4R H0 _ D R _MDQS31 8 H0 _ D R_MD102 6 H0 _ D R_MD103 4 H0 _ D R _MD99 2 (BOT)10_8P4R H0 _ D R_MD108 8 H0 _ D R_MD104 6 H0 _ D R_MD109 4 H0 _ D R_MD105 2 (BOT)10_8P4R H0 _ DR_-MSRASA 8 H0 _ DR_-MSWEA 6 H0 _ DR_-MSCASA 4 H0 _ DR_-MCS0 2 2 4 6 8 2 4 6 8 RN2107 7 5 3 1 RN2109 H0 _ D R _MDQS27 7 H0 _ D R _MDQS18 5 H0 _ D R _MD70 3 H0 _ D R _MD66 1 RN2111 H0 _ D R _MD71 7 H0 _ D R _MD67 5 H0 _ D R _MD72 3 H0 _ D R _MD76 1 RN2113 H0 _ D R _MD73 7 H0 _ D R _MD77 5 H0 _ D R _MDQS19 3 H0 _ D R _MDQS28 1 RN2115 H0 _ D R _MD78 7 H0 _ D R _MD79 5 H0 _ D R _MD74 3 H0 _ D R _MD75 1 RN2117 H0 _ D R _MD84 7 H0 _ D R _MD80 5 H0 _ D R _MD81 3 H0 _ D R _MD85 1 RN2119 H0 _ D R _MDQS20 7 H0 _ D R _MDQS29 5 H0 _ D R _MD82 3 H0 _ D R _MD86 1 RN2121 H0 _ DR_MAA7 7 H0 _ D R _MD83 5 H0 _ D R _MD87 3 1 RN2123 7 5 H0 _ DR_MAA5 3 H0 _ D R _MD88 1 RN2125 H0 _ DR_MAA6 7 H0 _ D R _MD92 5 H0 _ D R _MD93 3 H0 _ D R _MD89 1 RN2127 H0 _ D R _MDQS21 7 H0 _ D R _MDQS30 5 H0 _ DR_MAA4 3 H0 _ D R _MD94 1 RN2129 H0 _ D R _MD90 7 H0 _ D R _MD91 5 H0 _ D R _MD95 3 H0 _ D R _ ME MCHECK12 1 RN2131 H0 _ D R _ ME MCHECK13 7 H0 _ D R _ ME MCHECK8 5 H0 _ D R _ ME MCHECK9 3 H0 _ D R _MDQS35 1 RN2133 H0 _ D R _MDQS26 7 H0 _ D R _ ME MCHECK10 5 H0 _ D R _ ME MCHECK11 3 H0 _ D R _ ME MCHECK14 1 RN2136 H0 _ D R _ ME MCHECK15 7 H0 _ D R _MD96 5 H0 _ D R_MD100 3 H0 _ D R_MD101 1 RN2138 H0 _ D R _MD97 7 H0 _ D R _MDQS22 5 H0 _ D R _MD98 3 H0 _ D R _MDQS31 1 RN2140 H0 _ D R_MD102 7 H0 _ D R_MD103 5 H0 _ D R _MD99 3 H0 _ D R_MD108 1 RN2141 H0 _ D R_MD104 7 H0 _ DR_-MSRASA 5 H0 _ D R_MD109 3 H0 _ DR_-MSWEA 1 RN2143 H0 _ D R_MD105 7 H0 _ DR_-MCS0 5 H0 _ DR_-MSCASA 3 H0 _ DR_-MCS2 1 RN2145 H0 _ DR_-MCS3 7 H0 _ DR_-MCS1 5 H0 _ D R _MDQS32 3 H0 _ D R _MDQS23 1 RN2147 H0 _ D R_MD106 7 H0 _ D R_MD110 5 H0 _ D R_MD107 3 H0 _ D R_MD111 1 RN2149 H0 _ D R_MD112 7 H0 _ D R_MD113 5 H0 _ D R_MD116 3 H0 _ D R_MD117 1 RN2151 H0 _ D R _MDQS33 7 H0 _ D R_MD118 5 H0 _ D R _MDQS24 3 H0 _ D R_MD119 1 RN2153 H0 _ D R_MD114 7 H0 _ D R_MD115 5 H0 _ D R_MD124 3 H0 _ D R_MD125 1 RN2155 H0 _ D R_MD120 7 H0 _ D R_MD121 5 H0 _ D R _MDQS34 3 H0 _ D R_MD126 1 RN2156 H0 _ D R _MDQS25 7 H0 _ D R_MD127 5 H0 _ D R_MD122 3 H0 _ D R_MD123 1 H0 _ D R _MD68 H0 _ D R _MD64 H0 _ D R _MD69 H0 _ D R _MD65 H0 _ DR_-MCS4 <10> H0 _ D R_MD106 H0 _ D R _MDQS23 H0 _ D R _MDQS32 (BOT)10_8P4R H0 _ D R_MD111 H0 _ D R_MD107 H0 _ D R_MD110 H0 _ DR _ -MCS5 <10> H0 _ D R_MD112 8 H0 _ D R_MD113 (BOT)10_8P4R 6 H0 _ D R_MD116 4 H0 _ D R_MD117 2 (BOT)10_8P4R (BOT)10_8P4R H0 _ D R _MDQS33 8 H0 _ D R_MD118 6 H0 _ D R _MDQS24 4 H0 _ D R_MD119 2 (BOT)10_8P4R H0 _ D R_MD114 8 H0 _ D R_MD115 6 H0 _ D R_MD124 4 H0 _ D R_MD125 2 (BOT)10_8P4R H0 _ D R_MD120 8 H0 _ D R_MD121 6 H0 _ D R _MDQS34 4 H0 _ D R_MD126 2 (BOT)10_8P4R H0 _ D R _MDQS25 8 H0 _ D R_MD127 6 H0 _ D R_MD122 4 H0 _ D R_MD123 2 100u/10V 100u/10V (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 (BOT)47_8P4R 8 6 4 2 LAYOUT: Place alternating caps to GND and VDD_25_SUS in a single line along VTT island. LAYOUT: Place alternating caps to GND and VDD_25_SUS in a single line along VTT island. V C C _ D DR D C2221 C2059 C2119 C2131 C2090 C2193 C2124 C2138 C2098 C2100 C2062 C2128 C2078 C2201 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u V C C _ D DR C2532 C2572 C2570 C2567 C2565 C2563 C2556 C2543 C2540 C2536 C2534 C2561 C2596 C2594 (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u 0.1u VTT_DDR VTT_DDR V C C _ D DR V C C _ D DR C2207 C2260 C2187 C2183 C2177 C2165 C2159 C2154 C2152 C2148 C2257 C2253 C2235 C2213 C2106 C2108 C2143 C2592 C2590 C2586 C2584 C2553 C2538 C2528 C2526 C2582 C2580 C2576 C2530 C2588 C2578 C2548 C2574 C2568 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u VTT_DDR VTT_DDR VTT_DDR C2149 C2153 C2050 C2160 C2172 C2180 C2185 C2189 C2199 C2206 C2208 C2218 C2230 C2242 C2256 C2258 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u VTT_DDR C2541 C2539 C2535 C2533 C2529 C2589 C2579 C2573 C2549 C2537 C2531 C2527 C2523 C2525 C2524 C2562 (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u 0.1u VTT_DDR VTT_DDR C2096 C2140 C2130 C2134 C2072 C2081 C2126 C2121 C2115 C2060 C2055 C2028 C2261 C2099 C2103 C2107 C2145 C2583 C2581 C2577 C2575 C2571 C2566 C2564 C2555 C2544 C2559 C2569 C2597 C2595 C2593 C2591 C2587 C2585 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u (BOT)0.1u PLEASE ON SOLDER SIDE VTT_DDR VTT_DDR C2269 C2173 C2018 C2041 C2192 C2216 C2040 4 .7 u/6.3V/X5R-0805 4 .7 u/6.3V/X5R-0805 4 .7 u/6.3V/X5R-0805 4 .7 u/6.3V/X5R-0805 4 .7 u/6.3V/X5R-0805 4 .7 u/6.3V/X5R-0805 4 .7 u/6.3V/X5R-0805 C2171 1000P/50V/X7R C VTT_DDR V C C _ D DR VTT_DDR AROUND VTT POWER RAIL BETWEEN DIMM AND CPU C2262 C2006 C2008 0 .2 2u/16V/X7R C2204 C2054 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R C2232 C2043 C2168 C2046 C2057 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R C2267 CT2000 CT2012 4.7u/0805 4 .7 u/0805 C2065 C2191 C2254 C2002 C2004 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R C2607 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R solder side These caps are along the path from regulator to CPU VTT_DDR ??? VTT_DDR V C C _ D DR C2190 C2266 Put close to dimm socket VCC_DDR C2156 C2112 0 .2 2u/16V/X7R C2069 C2044 C2027 C2039 C2214 C2225 C2066 C2110 C2111 C2157 C2158 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R 0 .2 2u/16V/X7R EMI components VCC_DDR C2114 C2296 C2252 C2271 C2203 C2144 C2071 C2315 C2181 C2064 4.7u/0805 4.7u/0805 4.7u/0805 4.7u/0805 4.7u/0805 4.7u/0805 4 .7 u/0805 4 .7 u/0805 4.7u/0805 4.7u/0805 V C C _ D DR 4.7u/35V-1206 5/14 C2272 B V C C _ D DR C2067 C2013 C2017 C2026 C2212 C2211 C2210 C2270 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u V C C _ D DR C2179 0 .2 2u/16V VCC_DDR C2287 EC2008 EC2017 EC2016 + EC2007 + 0 .2 2u/16V 1200u/4V These caps are at both ends of dimm 1200u/4V 1 0 0 0U/6.3V 1 0 0 0 U/6.3V R N2 154 H0 _ MDQ S [35..0] <4> H0 _ MD Q S [3 5..0] H0 _ MD [1 2 7..0] <4> H0 _ MD [1 2 7..0] H0 _ ME MC HE C K [15..0] <4> H0 _ ME MC HE C K [15..0] H0 _ MA A [13..0] <4> H0 _ MA A [13..0] H0 _ -MC S [3 ..0] <4> H0 _ -MC S [3 ..0] H0 _ MCKELO H0 _ MCKEUP H0_MEMBAKA0 H0_MEMBAKA1 H0 _ -MSRASA H0 _ -MSCASA H0 _ -MSWEA <4> H0 _ MCKELO <4> H0 _ MCKEUP <4> H0_MEMBAKA0 <4> H0_MEMBAKA1 <4> H0 _ -MSRASA <4> H0 _ -MSCASA <4> H0 _ -MSWEA <8,9,10> H0 _ D R _ MD Q S [35..0] <8,9,10> H0 _ D R _ MD [1 27..0] <8,9,10> H0 _ D R _ ME MC HE C K [15..0] <8,9,10> H0 _ D R _ MA A [13..0] <8,9> H0 _ D R _ -MC S [3..0] <8,9,10> H0 _ DR_MCKELO <8,9,10> H0 _ D R _ MCKEUP <8,9,10> H0 _ DR_MEMBAKA0 <8,9,10> H0 _ DR_MEMBAKA1 <8,9,10> H0 _ DR_-MSRASA <8,9,10> H0 _ DR_-MSCASA <8,9,10> H0 _ DR_-MSWEA Co-layout H0 _ DR_ MDQ S [35..0] H0 _ D R _ MD [1 27..0] H0 _ D R _ ME MC HE C K [15..0] H0 _ D R _ MA A [13..0] A H0 _ D R _ -MC S [3..0] H0 _ DR_MCKELO H0 _ D R _ MCKEUP H0 _ DR_MEMBAKA0 H0 _ DR_MEMBAKA1 H0 _ DR_-MSRASA H0 _ DR_-MSCASA H0 _ DR_-MSWEA Micro Star Restricted Secret Title Rev CPU DDR (termination) Document Number M S - 9 620 MICRO-STAR INT'L CO.,LTD. No . 6 9 , L i-D e S t, J ung -He C ity, T aip e i Hs ien, Taiwan http ://www.m s i.c o m .tw 5 0 .2 2u/16V 0 .2 2u/16V Co-layout A C2194 C2076 0 .2 2u/16V0 .2 2u/16V0.22u/16V 0 .2 2u/16V 0 .2 2u/16V0 .2 2u/16V0 .2 2u/16V0 .2 2u/16V 4 3 http://laptop-motherboard-schematic.blogspot.com/ 2 1 0A L as t R e vis io n D ate: T ue s d ay, F e b ruary 15, 2005 S heet of 11 44 5 4 3 2 VTT_DDR VTT_DDR VDD_12_A U2013E K10 J11 H10 H8 K14 J15 K16 J16 J9 D H0_CADOU T15 H0_CADOU T#15 H0_CADOU T14 H0_CADOU T#14 H0_CADOU T13 H0_CADOU T#13 H0_CADOU T12 H0_CADOU T#12 H0_CADOU T11 H0_CADOU T#11 H0_CADOU T10 H0_CADOU T#10 H0_CADOU T9 H0_CADOU T#9 H0_CADOU T8 H0_CADOU T#8 H0_CADOU T7 H0_CADOU T#7 H0_CADOU T6 H0_CADOU T#6 H0_CADOU T5 H0_CADOU T#5 H0_CADOU T4 H0_CADOU T#4 H0_CADOU T3 H0_CADOU T#3 H0_CADOU T2 H0_CADOU T#2 H0_CADOU T1 H0_CADOU T#1 H0_CADOU T0 H0_CADOU T#0 <6> H0_CADOUT[15..0] <6> H0_CADOUT#[15..0] C <6> H0_CLKOUT1 <6> H0_CLKOUT#1 <6> H0_CLKOUT0 <6> H0_CLKOUT#0 <6> H0_CTLOUT0 <6> H0_CTLOUT#0 E14 E13 C15 D15 E16 E15 C17 D17 C19 D19 E20 E19 C21 D21 E22 E21 C14 B14 A16 A15 C16 B16 A18 A17 A20 A19 C20 B20 A22 A21 C22 B22 H0_CLKOUT1 H0_CLKOUT#1 H0_CLKOUT0 H0_CLKOUT#0 E18 E17 C18 B18 H0_C TLOUT0 H0_C TLOUT#0 A14 A13 C13 D13 C2236 C2222 C2223 C2224 0.1u 0.1u 0.1u 0.1u VLDT_1(1) VLDT_1(2) VLDT_1(3) VLDT_1(4) VLDT_1(5) VLDT_1(6) VLDT_1(7) VLDT_1(8) VLDT_1(9) VTT_DDR R2122 L1_CADIN_H(15) L1_CADIN_L(15) L1_CADIN_H(14) L1_CADIN_L(14) L1_CADIN_H(13) L1_CADIN_L(13) L1_CADIN_H(12) L1_CADIN_L(12) L1_CADIN_H(11) L1_CADIN_L(11) L1_CADIN_H(10) L1_CADIN_L(10) L1_CADIN_H(9) L1_CADIN_L(9) L1_CADIN_H(8) L1_CADIN_L(8) L1_CADIN_H(7) L1_CADIN_L(7) L1_CADIN_H(6) L1_CADIN_L(6) L1_CADIN_H(5) L1_CADIN_L(5) L1_CADIN_H(4) L1_CADIN_L(4) L1_CADIN_H(3) L1_CADIN_L(3) L1_CADIN_H(2) L1_CADIN_L(2) L1_CADIN_H(1) L1_CADIN_L(1) L1_CADIN_H(0) L1_CADIN_L(0) L1_CADOUT_H(15) L1_CADOUT_L(15) L1_CADOUT_H(14) L1_CADOUT_L(14) L1_CADOUT_H(13) L1_CADOUT_L(13) L1_CADOUT_H(12) L1_CADOUT_L(12) L1_CADOUT_H(11) L1_CADOUT_L(11) L1_CADOUT_H(10) L1_CADOUT_L(10) L1_CADOUT_H(9) L1_CADOUT_L(9) L1_CADOUT_H(8) L1_CADOUT_L(8) L1_CADOUT_H(7) L1_CADOUT_L(7) L1_CADOUT_H(6) L1_CADOUT_L(6) L1_CADOUT_H(5) L1_CADOUT_L(5) L1_CADOUT_H(4) L1_CADOUT_L(4) L1_CADOUT_H(3) L1_CADOUT_L(3) L1_CADOUT_H(2) L1_CADOUT_L(2) L1_CADOUT_H(1) L1_CADOUT_L(1) L1_CADOUT_H(0) L1_CADOUT_L(0) L1_CLKIN_H(1) L1_CLKIN_L(1) L1_CLKIN_H(0) L1_CLKIN_L(0) L1_CLKOUT_H(1) L1_CLKOUT_L(1) L1_CLKOUT_H(0) L1_CLKOUT_L(0) L1_CTLIN_H(0) L1_CTLIN_L(0) L1_CTLOUT_H(0) L1_CTLOUT_L(0) L1_RSVD1 L1_RSVD2 L1_RSVD3 L1_RSVD4 D11 C11 E9 E10 D9 C9 E7 E8 E5 E6 D5 C5 E3 E4 D3 C3 A11 A12 B10 C10 A9 A10 B8 C8 B6 C6 A5 A6 B4 C4 A3 A4 H 0_CADIN15 H0_CADIN#15 H 0_CADIN14 H0_CADIN#14 H 0_CADIN13 H0_CADIN#13 H 0_CADIN12 H0_CADIN#12 H 0_CADIN11 H0_CADIN#11 H 0_CADIN10 H0_CADIN#10 H 0_CADIN9 H 0_CADIN#9 H 0_CADIN8 H 0_CADIN#8 H 0_CADIN7 H 0_CADIN#7 H 0_CADIN6 H 0_CADIN#6 H 0_CADIN5 H 0_CADIN#5 H 0_CADIN4 H 0_CADIN#4 H 0_CADIN3 H 0_CADIN#3 H 0_CADIN2 H 0_CADIN#2 H 0_CADIN1 H 0_CADIN#1 H 0_CADIN0 H 0_CADIN#0 D7 C7 A7 A8 H0_CLKIN1 H0_CLKIN #1 H0_CLKIN0 H0_CLKIN #0 B12 C12 H0_CTLIN0 H0_CTLIN#0 H0_CADIN[15..0] <6> H0_CADIN#[15..0] <6> H 1_VREF1_DDR H 1_VREF1_DDR C2604 C2248 1000P/50V/X7R 1000P/50V/X7R 4.7u/6.3V/X5R-0805 1000P/50V/X7R 1000P/50V/X7R 1000P/50V/X7R 100u/10V C2268 C2337 C2334 C2280 C2233 H0_CLKIN1 H0_CLKIN#1 H0_CLKIN0 H0_CLKIN#0 <6> <6> <6> <6> H0_CTLIN0 H0_CTLIN#0 <6> <6> CT2011 B R2120 100RST R2121 100RST AF17 AE16 F22 AF22 AG24 AH25 AG26 AH27 AF23 AH24 AF25 AJ26 AG27 AF26 AF28 AE29 AJ29 AH29 AE27 AD26 AD27 AC26 AA26 AA28 AD28 AC27 AB29 AA27 Y27 Y28 V28 U26 Y26 W27 V27 U27 P28 N29 M26 L28 P27 P26 M27 L27 K29 K27 H28 G29 L26 J28 H27 H26 F27 F26 D29 D27 G27 F28 E27 C27 C26 E25 D24 F23 E26 F25 E24 G23 SOLDER SIDE VC C _ DDR 42.2RST 42.2RST H 1 _VREF1_DDR C2251 R27 AG25 AF27 AB27 W29 N27 J27 E29 F24 R28 AF24 AG28 AC28 V26 M28 J26 E28 D25 U31 AJ25 AJ30 AD29 AA31 M30 H30 C30 B25 T31 AL25 AL29 AE31 Y29 M29 H29 C29 C25 0.1u C2250 0.1u C2249 1000P/50V/X7R C2338 C2339 1000P/50V/X7R 0.1u closed to AF22 PIN VTT_SENSE MEMZN MEMZP MEMCKE_UP MEMCKE_LO MEMVREF0 MEMVREF1 MEMADD(13) MEMADD(12) MEMADD(11) MEMADD(10) MEMADD(9) MEMADD(8) MEMADD(7) MEMADD(6) MEMADD(5) MEMADD(4) MEMADD(3) MEMADD(2) MEMADD(1) MEMADD(0) E11 E12 0.22u/16V/X7R MEMCLK_UP_H(3) MEMCLK_UP_L(3) MEMCLK_UP_H(2) MEMCLK_UP_L(2) MEMCLK_UP_H(1) MEMCLK_UP_L(1) MEMCLK_UP_H(0) MEMCLK_UP_L(0) MEMCLK_LO_H(3) MEMCLK_LO_L(3) MEMCLK_LO_H(2) MEMCLK_LO_L(2) MEMCLK_LO_H(1) MEMCLK_LO_L(1) MEMCLK_LO_H(0) MEMCLK_LO_L(0) RSVD_MA(15) RSVD_MA(14) VDD_12_A C2603 R2182 R2184 VTT1 VTT2 VTT3 VTT4 VTT5 VTT6 VTT7 VTT8 VTT9 VTT10 X_51 AF19 VC C _ DDR SledgeHammer 0.22u/16V/X7R AC19 AE19 J19 H19 F20 G19 AE18 AC18 F21 AF18 1 U2013B closed to F22 PIN A MEMDATA(127) MEMDATA(126) MEMDATA(125) MEMDATA(124) MEMDATA(123) MEMDATA(122) MEMDATA(121) MEMDATA(120) MEMDATA(119) MEMDATA(118) MEMDATA(117) MEMDATA(116) MEMDATA(115) MEMDATA(114) MEMDATA(113) MEMDATA(112) MEMDATA(111) MEMDATA(110) MEMDATA(109) MEMDATA(108) MEMDATA(107) MEMDATA(106) MEMDATA(105) MEMDATA(104) MEMDATA(103) MEMDATA(102) MEMDATA(101) MEMDATA(100) MEMDATA(99) MEMDATA(98) MEMDATA(97) MEMDATA(96) MEMDATA(95) MEMDATA(94) MEMDATA(93) MEMDATA(92) MEMDATA(91) MEMDATA(90) MEMDATA(89) MEMDATA(88) MEMDATA(87) MEMDATA(86) MEMDATA(85) MEMDATA(84) MEMDATA(83) MEMDATA(82) MEMDATA(81) MEMDATA(80) MEMDATA(79) MEMDATA(78) MEMDATA(77) MEMDATA(76) MEMDATA(75) MEMDATA(74) MEMDATA(73) MEMDATA(72) MEMDATA(71) MEMDATA(70) MEMDATA(69) MEMDATA(68) MEMDATA(67) MEMDATA(66) MEMDATA(65) MEMDATA(64) MEMDATA(63) MEMDATA(62) MEMDATA(61) MEMDATA(60) MEMDATA(59) MEMDATA(58) MEMDATA(57) MEMDATA(56) MEMDATA(55) MEMDATA(54) MEMDATA(53) MEMDATA(52) MEMDATA(51) MEMDATA(50) MEMDATA(49) MEMDATA(48) MEMDATA(47) MEMDATA(46) MEMDATA(45) MEMDATA(44) MEMDATA(43) MEMDATA(42) MEMDATA(41) MEMDATA(40) MEMDATA(39) MEMDATA(38) MEMDATA(37) MEMDATA(36) MEMDATA(35) MEMDATA(34) MEMDATA(33) MEMDATA(32) MEMDATA(31) MEMDATA(30) MEMDATA(29) MEMDATA(28) MEMDATA(27) MEMDATA(26) MEMDATA(25) MEMDATA(24) MEMDATA(23) MEMDATA(22) MEMDATA(21) MEMDATA(20) MEMDATA(19) MEMDATA(18) MEMDATA(17) MEMDATA(16) MEMDATA(15) MEMDATA(14) MEMDATA(13) MEMDATA(12) MEMDATA(11) MEMDATA(10) MEMDATA(9) MEMDATA(8) MEMDATA(7) MEMDATA(6) MEMDATA(5) MEMDATA(4) MEMDATA(3) MEMDATA(2) MEMDATA(1) MEMDATA(0) MEMDQS(35) MEMDQS(34) MEMDQS(33) MEMDQS(32) MEMDQS(31) MEMDQS(30) MEMDQS(29) MEMDQS(28) MEMDQS(27) MEMDQS(26) MEMDQS(25) MEMDQS(24) MEMDQS(23) MEMDQS(22) MEMDQS(21) MEMDQS(20) MEMDQS(19) MEMDQS(18) MEMDQS(17) MEMDQS(16) MEMDQS(15) MEMDQS(14) MEMDQS(13) MEMDQS(12) MEMDQS(11) MEMDQS(10) MEMDQS(9) MEMDQS(8) MEMDQS(7) MEMDQS(6) MEMDQS(5) MEMDQS(4) MEMDQS(3) MEMDQS(2) MEMDQS(1) MEMDQS(0) MEMRESET_L MEMBANK(1) MEMBANK(0) MEMRAS_L MEMCAS_L MEMWE_L MEMCHECK(15) MEMCHECK(14) MEMCHECK(13) MEMCHECK(12) MEMCHECK(11) MEMCHECK(10) MEMCHECK(9) MEMCHECK(8) MEMCHECK(7) MEMCHECK(6) MEMCHECK(5) MEMCHECK(4) MEMCHECK(3) MEMCHECK(2) MEMCHECK(1) MEMCHECK(0) MEMCS_L(7) MEMCS_L(6) MEMCS_L(5) MEMCS_L(4) MEMCS_L(3) MEMCS_L(2) MEMCS_L(1) MEMCS_L(0) http://laptop-motherboard-schematic.blogspot.com/ 4 3 D H24 H25 V23 M23 AE23 J24 J25 V24 K23 L23 K25 M25 M24 N25 N23 P23 T25 V25 AJ24 AK25 AK27 AJ27 AL24 AK24 AL26 AL27 AJ28 AK30 AJ31 AG29 AL28 AK28 AH31 AG30 AG31 AF30 AD31 AC30 AF29 AF31 AD30 AC29 AB31 AA29 Y31 W31 AC31 AA30 Y30 V29 P31 M31 L30 L29 P29 N31 L31 K31 J30 J29 G31 F29 J31 H31 F31 F30 D31 C31 B30 C28 E31 E30 A29 B28 B27 A26 C24 A24 A28 A27 A25 B24 C B G25 H1_MEMRESET1_L W25 W23 Y25 AA25 Y24 U28 T29 P24 P25 T27 R26 R25 R24 V30 U29 R30 P30 V31 U30 R29 R31 AD23 AE25 AD24 AD25 AC24 AC25 AB25 AA24 A Micro Star Restricted Secret Title Document Number SledgeHammer 5 G20 G21 AE21 AE20 L24 L25 R23 T23 H23 J23 AD21 AD20 Y23 AA23 U25 U24 2 R ev CPU1_K8 DDR & HT 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 12 44 5 4 C2234 D C2229 C2245 C2246 CT2010 1 VCC2_5 100u/10V VCC2_5 H1_TDI R2464 H1_TMS R2465 1K 1K U2013C H1_VDDA25 FB2001 VDD_12_A <38> COREFB1_H <38> COREFB1_L 180nH/1210 <22> CPUCLK1_H <22> CPUCLK1_L CLKIN1_L THERMTRIP_L C1 D2 C2 VDDA1 VDDA2 VDDA3 R2128 R2127 43.2RST 43.2RST E1 D1 L0_REF1 L0_REF0 R2144 R2137 0 0 L7 L6 COREFB_H COREFB_L TP2023 K7 CORESENSE_H CLKIN1_H R2424 (BOT)169RST 2 LAYOUT: Route VDDA trace approx. 50 mils wide (use 2x25 mil traces to exit ball) and 500 mils long. H1_VDDA25 4.7u/6.3V/X5R-0805 3300p/50V/X7R 1000P/50V/X7R 0.22u/16V 3 C2237 C2238 3900P/50V/X7R CLKIN1_H G16 CLKIN1_L H16 3900P/50V/X7R H1_NC_G14 G14 H1_NC_H14 H14 C H1_TMS H1_TCK H1_TRST_L H1_TDI H1_DBREQ_L AE6 AE7 AD7 AF7 J7 H1_SCANCLK1 AE10 H1_SCANCLK2 AE11 CLKIN_H CLKIN_L DBRDY SCANSHIFTEN SCANSHIFTENB SCANIN_H SCANIN_L SCANOUT_H SCANOUT_L SINGLECHAIN B AF15 H1_NC_AE14 AE14 PLLCHRZ_H PLLCHRZ_L H1_TCK R2467 1K D THERMDA_CPU2 <33> VTIN_GND <5,33> R2133 R2118 R2134 R2117 R2119 0 0 0 0 0 H1_VID4 H1_VID3 H1_VID2 H1_VID1 H1_VID0 <32,37> <32,37> <32,37> <32,37> <32,37> modified on 1/30 H1_BP3 H1_BP2 H1_BP1 H1_BP0 LAYOUT: Route FBCLKOUT_H/L differentially with 20/8/5/8/20 spacing and trace width. STRAPPINGS G18 H1_FBCLKOUT_H H18 VCC2_5 AE8 G8 TP2037 H1_NC_G14 R2149 820 H1_NC_AE14 R2181 680 H1_NC_AF13 R2180 680 H1_DBREQ_L R2148 1K C H1_DBRDY U2_R6 R2459 H1_NC_T3 680 V5 U5 TSTOUT H7 ANALOG3 ANALOG2 ANALOG1 ANALOG0 T7 W6 R6 U6 R2460 H1_DBRDY 49.9RST H1_NC_H14 R2126 H1_SCANEN R2198 680 H1_SCANCLK1R2177 680 H1_SCANCLK2 R2178 680 TP2028 TP2027 TP2021 U2_T7 U2_W6 U2_R6 U2_U6 U2_T7 U2_W6 U2_U6 2 4 6 8 RN2062 1 3 5 7 510_8P4R BURNIN_L RESET_L LDTSTOP_L PWROK TP2034 TP2035 TP2022 AG1 AH2 H9 FREE7 FREE11 FREE15 TP2036 TP2029 TP2030 TP2026 AJ2 AA6 AC6 N6 FREE12 FREE21 FREE1 FREE3 RSVD_SMBUSC RSVD_SMBUSD R2131 1K 820 H1_SSENA R2199 680 H1_SSENB R2179 680 H1_BP0 R2114 680 H1_BP1 R2129 680 H1_BP2 R2130 X_680 H1_BP3 R2115 X_680 B DCLKTWO G12 J6 F12 <5,16> CPU_RST# <5,16> HT_STOP# <5,16> CPU_PWRGD H13 G6 F7 H12 1K SCANCLK1 SCANCLK2 SCANEN TP2033 BP(3) BP(2) BP(1) BP(0) R2466 H1_FBCLKOUT_L DBREQ_L AF11 L8 K8 G9 F9 G10 H11 G11 TDO AE13 AE12 T3 T4 TP2025 TP2024 VID(4) VID(3) VID(2) VID(1) VID(0) CPU_THEMTRIP# <5,16> R2423 80.6RST TMS TCK TRST_L TDI H1_SCANEN AF13 AJ1 AH1 BYPASSCLK_H BYPASSCLK_L H1_SSENA H1_SSENB H1_NC_T3 H1_NC_T4 H1_NC_AF13 THERMDA THERMDC FBCLKOUT_H FBCLKOUT_L CPU_THEMTRIP# AE15 H1_TRST_L TP2032 AF9 AE9 TP2031 VDD_12_A H1_NC_T4 R2138 49.9RST R2145 X_49.9RST A A SledgeHammer Micro Star Restricted Secret Title Rev CPU1_K8 HDT 7 MISC Document Number MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 5 4 3 http://laptop-motherboard-schematic.blogspot.com/ 2 0A Last Revision Date: Tuesday, February 15, 2005 Sheet 13 44 of 1 5 4 3 2 1 VDD_12_A VDD_12_A D U2013F U2013A C2247 0.22u/16V/X7R C B C2336 1000P/50V/X7R N7 R7 U7 W7 M8 P8 AA7 V8 Y8 VLDT_0(1) VLDT_0(2) VLDT_0(3) VLDT_0(4) VLDT_0(5) VLDT_0(6) VLDT_0(7) VLDT_0(8) VLDT_0(9) C2241 C2289 0.22u/16V/X7R R5 T5 P3 P4 N5 P5 M3 M4 K3 K4 J5 K5 H3 H4 G5 H5 R3 R2 N1 P1 N3 N2 L1 M1 J1 K1 J3 J2 G1 H1 G3 G2 L0_CADIN_H(15) L0_CADIN_L(15) L0_CADIN_H(14) L0_CADIN_L(14) L0_CADIN_H(13) L0_CADIN_L(13) L0_CADIN_H(12) L0_CADIN_L(12) L0_CADIN_H(11) L0_CADIN_L(11) L0_CADIN_H(10) L0_CADIN_L(10) L0_CADIN_H(9) L0_CADIN_L(9) L0_CADIN_H(8) L0_CADIN_L(8) L0_CADIN_H(7) L0_CADIN_L(7) L0_CADIN_H(6) L0_CADIN_L(6) L0_CADIN_H(5) L0_CADIN_L(5) L0_CADIN_H(4) L0_CADIN_L(4) L0_CADIN_H(3) L0_CADIN_L(3) L0_CADIN_H(2) L0_CADIN_L(2) L0_CADIN_H(1) L0_CADIN_L(1) L0_CADIN_H(0) L0_CADIN_L(0) L0_CADOUT_H(15) L0_CADOUT_L(15) L0_CADOUT_H(14) L0_CADOUT_L(14) L0_CADOUT_H(13) L0_CADOUT_L(13) L0_CADOUT_H(12) L0_CADOUT_L(12) L0_CADOUT_H(11) L0_CADOUT_L(11) L0_CADOUT_H(10) L0_CADOUT_L(10) L0_CADOUT_H(9) L0_CADOUT_L(9) L0_CADOUT_H(8) L0_CADOUT_L(8) L0_CADOUT_H(7) L0_CADOUT_L(7) L0_CADOUT_H(6) L0_CADOUT_L(6) L0_CADOUT_H(5) L0_CADOUT_L(5) L0_CADOUT_H(4) L0_CADOUT_L(4) L0_CADOUT_H(3) L0_CADOUT_L(3) L0_CADOUT_H(2) L0_CADOUT_L(2) L0_CADOUT_H(1) L0_CADOUT_L(1) L0_CADOUT_H(0) L0_CADOUT_L(0) V4 V3 Y5 W5 Y4 Y3 AB5 AA5 AD5 AC5 AD4 AD3 AF5 AE5 AF4 AF3 V1 U1 W2 W3 Y1 W1 AA2 AA3 AC2 AC3 AD1 AC1 AE2 AE3 AF1 AE1 L5 M5 L3 L2 L0_CLKIN_H(1) L0_CLKIN_L(1) L0_CLKIN_H(0) L0_CLKIN_L(0) L0_CLKOUT_H(1) L0_CLKOUT_L(1) L0_CLKOUT_H(0) L0_CLKOUT_L(0) AB4 AB3 AB1 AA1 R1 T1 L0_CTLIN_H(0) L0_CTLIN_L(0) L0_CTLOUT_H(0) L0_CTLOUT_L(0) U2 U3 C2302 1000P/50V/X7R 4.7u/35V-1206 AB10 AC11 AD10 AD8 AB14 AC15 AB16 AC16 AC9 VLDT_2(1) VLDT_2(2) VLDT_2(3) VLDT_2(4) VLDT_2(5) VLDT_2(6) VLDT_2(7) VLDT_2(8) VLDT_2(9) AG11 AG12 AJ10 AH10 AG9 AG10 AJ8 AH8 AJ6 AH6 AG5 AG6 AJ4 AH4 AG3 AG4 AJ11 AK11 AL9 AL10 AJ9 AK9 AL7 AL8 AL5 AL6 AJ5 AK5 AL3 AL4 AJ3 AK3 L2_CADIN_H(15) L2_CADIN_L(15) L2_CADIN_H(14) L2_CADIN_L(14) L2_CADIN_H(13) L2_CADIN_L(13) L2_CADIN_H(12) L2_CADIN_L(12) L2_CADIN_H(11) L2_CADIN_L(11) L2_CADIN_H(10) L2_CADIN_L(10) L2_CADIN_H(9) L2_CADIN_L(9) L2_CADIN_H(8) L2_CADIN_L(8) L2_CADIN_H(7) L2_CADIN_L(7) L2_CADIN_H(6) L2_CADIN_L(6) L2_CADIN_H(5) L2_CADIN_L(5) L2_CADIN_H(4) L2_CADIN_L(4) L2_CADIN_H(3) L2_CADIN_L(3) L2_CADIN_H(2) L2_CADIN_L(2) L2_CADIN_H(1) L2_CADIN_L(1) L2_CADIN_H(0) L2_CADIN_L(0) D L2_CADOUT_H(15) L2_CADOUT_L(15) L2_CADOUT_H(14) L2_CADOUT_L(14) L2_CADOUT_H(13) L2_CADOUT_L(13) L2_CADOUT_H(12) L2_CADOUT_L(12) L2_CADOUT_H(11) L2_CADOUT_L(11) L2_CADOUT_H(10) L2_CADOUT_L(10) L2_CADOUT_H(9) L2_CADOUT_L(9) L2_CADOUT_H(8) L2_CADOUT_L(8) L2_CADOUT_H(7) L2_CADOUT_L(7) L2_CADOUT_H(6) L2_CADOUT_L(6) L2_CADOUT_H(5) L2_CADOUT_L(5) L2_CADOUT_H(4) L2_CADOUT_L(4) L2_CADOUT_H(3) L2_CADOUT_L(3) L2_CADOUT_H(2) L2_CADOUT_L(2) L2_CADOUT_H(1) L2_CADOUT_L(1) L2_CADOUT_H(0) L2_CADOUT_L(0) AH14 AJ14 AG16 AG15 AH16 AJ16 AG18 AG17 AG20 AG19 AH20 AJ20 AG22 AG21 AH22 AJ22 AL14 AL13 AK15 AJ15 AL16 AL15 AK17 AJ17 AK19 AJ19 AL20 AL19 AK21 AJ21 AL22 AL21 AG7 AG8 AJ7 AK7 L2_CLKIN_H(1) L2_CLKIN_L(1) L2_CLKIN_H(0) L2_CLKIN_L(0) L2_CLKOUT_H(1) L2_CLKOUT_L(1) L2_CLKOUT_H(0) L2_CLKOUT_L(0) AH18 AJ18 AL18 AL17 AL11 AL12 L2_CTLIN_H(0) L2_CTLIN_L(0) L2_CTLOUT_H(0) L2_CTLOUT_L(0) AK13 AJ13 AJ12 AH12 L2_RSVD1 L2_RSVD2 L2_RSVD3 L2_RSVD4 AG13 AG14 C B SledgeHammer SledgeHammer A A Micro Star Restricted Secret Title Document Number Rev CPU1_K8_HT0 & HT2 MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 5 4 3 http://laptop-motherboard-schematic.blogspot.com/ 2 0A Last Revision Date: Tuesday, February 15, 2005 Sheet 14 44 of 1 B A SKTOCC_1_L 5 V6 AD12 H2 AA4 T18 V18 Y18 K12 F19 N19 R19 U19 W19 D20 AE4 M20 P20 T20 V20 Y20 AK20 B21 AH21 AK4 B5 AH5 K6 P6 T8 AB6 AF6 M2 F6 D8 G7 AB8 AK8 B9 K18 L9 N9 R9 T2 U9 W9 AA9 AB18 AH9 W13 M10 P10 T10 V10 Y2 Y10 AB12 AF10 F11 L11 N11 R11 U11 W11 AA11 AD2 D12 M12 P12 T12 V12 Y12 AC13 AK12 B13 L13 D4 N13 R13 U13 AA13 AH13 J13 M14 P14 T14 J4 V14 Y14 AD14 AF14 F15 L15 N15 R15 U15 W15 N4 AA15 D16 F18 M16 P16 T16 V16 Y16 AD16 AK16 U4 B17 L17 N17 R17 U17 W17 AA17 AH17 M18 P18 AF20 4 VCC_DDR 4 3 LAYOUT: Place inside of processor. VCCP1 BULK / Decopuling VCCP1 VCCP1 C2598 C2599 C2601 X_(BOT)SP-CAP,220u/2V 4.7u/1206 0.22u/16V/X7R C2600 0.22u/16V/X7R 3 http://laptop-motherboard-schematic.blogspot.com/ EMI Place on CPU Solder side C2602 0.22u/16V/X7R 4.7u/1206 2 C2348 C2301 6.8p/50V/NPO 6.8p/50V/NPO 6.8p/50V/NPO 6.8p/50V/NPO 6.8p/50V/NPO 6.8p/50V/NPO 6.8p/50V/NPO 6.8p/50V/NPO 6.8p/50V/NPO 6.8p/50V/NPO C2279 C2264 C2294 C2255 C2178 C2263 C2312 C2288 C2240 C2346 C2347 C2227 4.7u/35V-1206 4.7u/35V-1206 4.7u/35V-1206 4.7u/35V-1206 4.7u/35V-1206 4.7u/35V-1206 4.7u/35V-1206 C2341 SledgeHammer Title AG2 E2 P13 W16 D23 AH23 VCCP1 AB23 AC23 L19 W21 AA21 J21 M22 P22 T22 V22 Y22 AB22 AJ23 AA19 C23 E23 K26 T26 AE28 G26 N26 W26 AE26 AG23 K20 D28 K28 T28 AB28 AH28 AH26 G28 N28 W28 AB26 AB20 L21 N21 R21 U21 H22 D26 K22 A23 U23 AL23 AC21 AD22 X_(BOT)SP-CAP,220u/2V T9 AC22 Y9 AB9 AD9 D10 J10 AD13 L10 N10 R10 U10 T6 AA10 AC10 AK10 B11 L14 H15 J8 K11 M11 P11 T11 V11 N14 Y11 AA12 N16 AF12 F13 G15 F10 AD15 K13 U14 M13 AB11 AD11 AH11 G13 J12 N12 R12 U12 R14 W12 W14 AA14 AC14 AH15 AK14 B15 K15 M15 B23 P15 T15 V15 Y15 AB15 D14 J14 H17 G24 L16 R16 U16 W18 AA16 AC17 AF16 F16 K17 N24 M17 P17 T17 V17 Y17 AB17 AD17 D18 J18 W24 L18 N18 R18 U18 W10 AA18 AE17 AK18 B19 G30 K19 M19 T19 V19 Y19 AB19 AH19 J20 L20 W30 N20 R20 U20 W20 AA20 AC20 AF21 K21 M21 AB24 P21 T21 V21 Y21 AB21 D22 G22 L22 N22 B26 R22 U22 W22 AA22 AE22 AK22 J22 AE24 AK26 B29 AK23 K24 T24 AE30 AK29 D30 K30 T30 AB30 AH30 AH7 V9 L12 AC12 U2013D VSS6 VDDIO1 VSS7 VDDIO2 VSS8 VDDIO3 VSS9 VDDIO4 VSS10 VDDIO5 VSS11 VDDIO6 VSS12 VDDIO7 VSS92 VDDIO8 VSS13 VDDIO9 VSS14 VDDIO10 VSS15 VDDIO11 VSS16 VDDIO12 VSS17 VDDIO13 VSS18 VDDIO14 VSS19 VDDIO15 VSS20 VDDIO16 VSS21 VDDIO17 VSS93 VDDIO18 VSS22 VDDIO19 VSS23 VDDIO20 VSS24 VDDIO21 VSS25 VDDIO22 VSS26 VDDIO23 VSS27 VDDIO24 VSS28 VDDIO25 VSS29 VDDIO26 VSS30 VDDIO27 VSS94 VDDIO28 VSS31 VDDIO29 VSS32 VDDIO30 VSS33 VDDIO31 VSS34 VDDIO32 VSS35 VDDIO33 VSS36 VDDIO34 VSS37 VDDIO35 VSS95 VDDIO36 VSS38 VDDIO37 VSS39 VDDIO38 VSS40 VDDIO40 VSS41 VDDIO41 VSS42 VDDIO42 VSS43 VDDIO43 VSS44 VDDIO44 VSS45 VDDIO45 VSS46 VDDIO47 VSS96 VDDIO48 VSS47 VDDIOFB_H VDDIOFB_L VSS48 VDDIO_SENSE VSS49 VSS50 VSS51 VSS52 VSS53 VSS54 VSS55 VSS97 VDD117 VSS56 VDD118 VSS57 VDD1 VSS58 VDD2 VSS59 VDD3 VSS60 VDD4 VSS61 VDD5 VSS62 VDD119 VSS63 VDD7 VSS64 VDD8 VSS98 VDD9 VSS65 VDD10 VSS66 VDD11 VSS67 VDD12 VSS68 VDD13 VSS69 VDD14 VSS70 VDD15 VSS71 VDD16 VSS99 VDD17 VSS72 VDD18 VSS82 VDD19 VSS83 VDD20 VSS84 VDD21 VSS85 VDD22 VSS86 VDD23 VSS87 VDD24 VSS88 VDD25 VSS89 VDD26 VSS101 VDD27 VSS90 VDD28 VSS73 VDD29 VSS74 VDD30 VSS75 VDD31 VSS76 VDD32 VSS77 VDD33 VSS78 VDD34 VSS79 VDD35 VSS80 VDD36 VSS100 VDD37 VSS81 VDD38 VSS102 VDD39 VSS103 VDD40 VSS104 VDD41 VSS105 VDD42 VSS106 VDD43 VSS107 VDD44 VSS108 VDD45 VSS109 VDD46 VSS182 VDD47 VSS110 VDD48 VSS111 VDD49 VSS112 VDD50 VSS113 VDD51 VSS114 VDD52 VSS115 VDD53 VSS116 VDD54 VSS117 VDD55 VSS183 VDD56 VSS118 VDD57 VSS119 VDD58 VSS120 VDD59 VSS121 VDD60 VSS122 VDD61 VSS123 VDD62 VSS124 VDD63 VSS125 VDD64 VSS126 VDD65 VSS184 VDD66 VSS127 VDD67 VSS128 VDD68 VSS129 VDD69 VSS130 VDD70 VSS131 VDD71 VSS132 VDD72 VSS133 VDD73 VSS134 VDD74 VSS135 VDD75 VSS185 VDD76 VSS136 VDD77 VSS137 VDD78 VSS138 VDD79 VSS139 VDD80 VSS140 VDD81 VSS141 VDD82 VSS142 VDD83 VSS143 VDD84 VSS144 VDD85 VSS186 VDD86 VSS145 VDD87 VSS146 VDD88 VSS147 VDD89 VSS148 VDD90 VSS149 VDD91 VSS150 VDD92 VSS151 VDD93 VSS152 VDD94 VSS153 VDD95 VSS187 VDD96 VSS154 VDD97 VSS155 VDD98 VSS156 VDD99 VSS157 VDD100 VSS158 VDD101 VSS159 VDD102 VSS160 VDD103 VSS161 VDD104 VSS162 VDD105 VSS188 VDD106 VSS163 VDD107 VSS164 VDD108 VSS165 VDD109 VSS166 VDD110 VSS167 VDD111 VSS168 VDD112 VSS169 VDD113 VSS170 VDD114 VSS171 VDD115 VSS189 VDD116 VSS172 VSS173 VSS174 VSS175 VSS176 VSS177 VSS178 VSS179 VSS180 VSS190 VSS181 VSS191 VSS192 VSS193 VSS194 VSS195 VSS196 VSS197 VSS198 VSS203 VSS199 VSS202 VSS1 VSS91 VSS2 VSS5 VSS3 VSS200 VSS4 VSS201 C2546 P9 F17 P19 N30 F1 F2 K2 P2 T13 V2 AB2 AF2 AK2 B3 AH3 G4 L4 R4 V13 W4 AC4 F5 D6 H6 M7 AB7 Y6 AD6 J17 AK6 B7 F14 P7 V7 Y7 M6 Y13 N8 R8 U8 W8 AA8 AF8 F8 G17 K9 AB13 M9 5 2 1 Place on inside of CPU Cavity ( 10 * 0.22uF/0603 X7R high-freq decoupling Cap. ) CPU D LAYOUT: Place 1 capacitor every 1-1.5" along VDD_CORE perimiter. D C2558 VCCP1 C2091 C2205 C2244 Document Number 1 C2450 C LAYOUT: Place clolse to socket. VCCP1 C 1000P/50V/X7R 1000P/50V/X7R 1000P/50V/X7R 1000P/50V/X7R C2243 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw C2259 VCCP1 CPU1_K8 POWER & GND B <32> A Micro Star Restricted Secret MS-9620 Rev Last Revision Date: Tuesday, February 15, 2005 Sheet of 15 44 0A 5 4 3 2 1 3VDUAL U16A R663 <17,33,36> SLP_S5# +12V SEC 1 OF 7 L0_CADIN0 L0_CADIN1 L0_CADIN2 L0_CADIN3 L0_CADIN4 L0_CADIN5 L0_CADIN6 L0_CADIN7 L0_CADIN8 L0_CADIN9 L0_CADIN10 L0_CADIN11 L0_CADIN12 L0_CADIN13 L0_CADIN14 L0_CADIN15 HT_RXD0 HT_RXD1 HT_RXD2 HT_RXD3 HT_RXD4 HT_RXD5 HT_RXD6 HT_RXD7 HT_RXD8 HT_RXD9 HT_RXD10 HT_RXD11 HT_RXD12 HT_RXD13 HT_RXD14 HT_RXD15 HT_TXD0 HT_TXD1 HT_TXD2 HT_TXD3 HT_TXD4 HT_TXD5 HT_TXD6 HT_TXD7 HT_TXD8 HT_TXD9 HT_TXD10 HT_TXD11 HT_TXD12 HT_TXD13 HT_TXD14 HT_TXD15 N27 N29 P29 P28 T28 U28 U30 V29 P25 P26 P22 T25 U22 V26 V24 V22 AG29 AF29 AE28 AD28 AB28 AB29 AA29 AA27 AF26 AD25 AD24 AC25 AB25 AA22 Y23 Y25 HT_RXD0* HT_RXD1* HT_RXD2* HT_RXD3* HT_RXD4* HT_RXD5* HT_RXD6* HT_RXD7* HT_RXD8* HT_RXD9* HT_RXD10* HT_RXD11* HT_RXD12* HT_RXD13* HT_RXD14* HT_RXD15* HT_TXD0* HT_TXD1* HT_TXD2* HT_TXD3* HT_TXD4* HT_TXD5* HT_TXD6* HT_TXD7* HT_TXD8* HT_TXD9* HT_TXD10* HT_TXD11* HT_TXD12* HT_TXD13* HT_TXD14* HT_TXD15* N28 N30 P30 R29 U27 U29 V30 V28 P24 N26 P23 T26 T22 U26 V25 V23 L0_CLKOUT0 L0_CLKOUT#0 L0_CLKOUT1 L0_CLKOUT#1 AC27 AC28 AB24 AB23 HT_RX_CLK0 HT_RX_CLK0* HT_RX_CLK1 HT_RX_CLK1* HT_TX_CLK0 HT_TX_CLK0* HT_TX_CLK1 HT_TX_CLK1* R28 R27 T23 T24 L0_CLKIN0 L0_CLKIN#0 L0_CLKIN1 L0_CLKIN#1 <6> <6> <6> <6> <6> L0_CTLOUT0 <6> L0_CTLOUT#0 Y28 W27 HT_RXCTL HT_RXCTL* HT_TXCTL HT_TXCTL* W29 W28 L0_CTLIN0 L0_CTLIN#0 <6> <6> M22 N22 HT_REQ*/GPIO HT_STOP* CPU_CLK CPU_CLK* L28 L29 CPU_CLK CPU_CLK# AF27 AF28 HT_CAL_GND1 HT_CAL_GND2 CPU_CLK_66 CPU_PWROK CPU_RST* THERMTRIP*/GPIO CPU_COMP L27 M26 M28 AF25 M25 C PU_PWRGD CPU_PWRGD <5,13> CPU_RST# <5,13> CPU_THEMTRIP# CPU_RST# CPU_THEMTRIP# <5,13> CPU_COMP D L0_CADOUT#0 L0_CADOUT#1 L0_CADOUT#2 L0_CADOUT#3 L0_CADOUT#4 L0_CADOUT#5 L0_CADOUT#6 L0_CADOUT#7 L0_CADOUT#8 L0_CADOUT#9 L0_CADOUT#10 L0_CADOUT#11 L0_CADOUT#12 L0_CADOUT#13 L0_CADOUT#14 L0_CADOUT#15 C <6> <6> <6> <6> VCC3 R464 10K <5,13> HT_STOP# R465 R466 HT_STOP# 49.9R 1% 150R 1% HT_VLD VCORE_VLD MEM_VLD HTVDD_EN VCORE_EN VCC3 L19 B X_F301S0805 AK5 AJ4 AK4 AE3 AD3 AG28 HT_VLD CPU_VLD MEM_VLD HTVDD_EN CPUVDD_EN Q2013 G Q2014 R2500 X_4.7K/6 C2687 +3.3V_PLL_HT AD5 AC6 AB6 AC3 AC5 CK8_TCK CK8_TDI R467 VCORE_EN CK8_TMS CK8_TRST* R664 C2688 103P VCORE_VLD 0R C308 X_0.1u 0402 R2501 <36,37,38> VRM_GD X_0R C <22> <22> 3VDUAL 10K R468 10K R469 10K HTVDD_EN R205 549R 1% R263 R2504 X_1K 1K HT_VLD C305 X_0.1u 0402 <36> HT_PWRGD C466 0.1u 0402 CP18 X_COPPER X_2N3904S X_0.1u/6 L0_CADIN#0 L0_CADIN#1 L0_CADIN#2 L0_CADIN#3 L0_CADIN#4 L0_CADIN#5 L0_CADIN#6 L0_CADIN#7 L0_CADIN#8 L0_CADIN#9 L0_CADIN#10 L0_CADIN#11 L0_CADIN#12 L0_CADIN#13 L0_CADIN#14 L0_CADIN#15 CPU_CLK CPU_CLK# X_2N7002S B VCC_DDR VCC3 TCK TDI TDO TMS TRST* D X_1K/6 L0_CADIN#[15..0] <6> <6> L0_CADOUT#[15..0] C313 X_0.1u 0402 R2499 S AG30 AF30 AE29 AD27 AC29 AB30 AA30 AA28 AE26 AD26 AC24 AC26 AB26 Y22 Y24 Y26 C L0_CADOUT0 L0_CADOUT1 L0_CADOUT2 L0_CADOUT3 L0_CADOUT4 L0_CADOUT5 L0_CADOUT6 L0_CADOUT7 L0_CADOUT8 L0_CADOUT9 L0_CADOUT10 L0_CADOUT11 L0_CADOUT12 L0_CADOUT13 L0_CADOUT14 L0_CADOUT15 D R2498 X_1K MEM_VLD 0R E <6> L0_CADOUT[15..0] L0_CADIN[15..0] <6> B +12V C2689 AG27 R470 10K +3.3V_PLL_CPU X_10U/0805 R2502 CK8-04 SLI VCC3 D X_1K/6 Q2015 L20 X_F301S0805 R2503 X_2N7002S B VDD_12_A X_10U/0805 C C2691 Q2016 X_4.7K/6 C2692 E C2690 103P C467 0.1u 0402 S G CP19 X_COPPER X_2N3904S X_0.1u/6 A A Micro Star Restricted Secret Title R ev NVIDIA CrushK8-04 Part 1 Document Number MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 2 0A MS-9620 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 16 44 5 4 3 MII_COL 2 1 M II_CRS RN80 USB1+ USB1USB0+ USB0- 3VDUAL <29> RGMII_TX[3..0] RGMII_TX0 RGMII_TX1 RGMII_TX2 RGMII_TX3 High:Use PHY Low: No use PHY R174 1.5K 1% RN104 2 4 6 8 MII_MDIO R2469 RGMIITX0 RGMIITX1 RGMIITX2 RGMIITX3 1 3 5 7 R2468 10K 22 22 RGMII_RX0 RGMII_RX1 RGMII_RX2 RGMII_RX3 RGMII_RXCLK RGMII_RXCTL MII_MDC <29> RGMII_RXCLK <29> RGMII_RXCTL <29> MII_MDC C226 0.1u 0402 G29 E30 F29 F28 H27 G28 K24 MII_VREF MII_COL <29> MII_MDIO MII_MDIO R500 <29> RGMII_PWDN# 0R R195 <29> RGMII_25M <31> VCC3 X_22 R268 AC97CLK 22 <31> AC_BITCLK VCC3 AC_SDOUT C <31> R283 10K R287 X_10K R501 10K G/MII_RXD0 G/MII_RXD1 G/MII_RXD2 G/MII_RXD3 G/MII_RXCLK G_RXCTL/MII_RXDV G/MII_MDC AC_SYNC AC _SDIN0 AC_SDIN0 AC_RST# AC_SYNC VCC3 P2 P3 USB0+ USB0- USB_1 USB_1* P8 P9 USB1+ USB1- USB_2 USB_2* R2 R3 USB2+ USB2- USB_3 USB_3* T3 R4 USB3+ USB3- USB_4 USB_4* U3 U4 USB4+ USB4- USB_5 USB_5* U1 U2 USB5+ USB5- USB_6 USB_6* T5 T6 USB6+ USB6- USB_7 USB_7* T7 T8 USB7+ USB7- USB_0 USB_0* E29 K29 K26 J30 K27 K25 K28 MII_VREF MII_RXER/GPIO MII_COL G/MII_MDIO MII_CRS MII_PWRDWN/GPIO MII_INTR/GPIO M24 BUF_25MHZ USB_8 USB_8* U5 V6 USB8+ USB8- Y6 AA5 AC97_CLK AC_BITCLK USB_9 USB_9* V7 V8 USB9+ USB9- Y8 Y7 AB8 AC_SDATA_OUT/GPIO AC_SDATA_IN0/SYS_PERR* AC_SDATA_IN1/SYS_SERR* Y5 AA9 AC_RESET* AC_SYNC/GPIO <31> AC_SDOUT <31> CK804 <26> <26> USB7USB7+ USB6USB6+ 2 4 6 8 15K-8P4R RN86 1 3 5 7 USB1+ USB1- <26> <26> USB2+ USB2- <30> <30> USB3+ USB3- <30> <30> USB5+ USB5USB4+ USB4- 2 4 6 8 15K-8P4R RN79 1 3 5 7 USB4+ USB4- <30> <30> USB5+ USB5- <30> <30> 2 4 6 8 15K-8P4R RN103 1 3 5 7 USB6+ USB6- <26> <26> USB7+ USB7- <26> <26> USB8+ USB8- <30> <30> USB9+ USB9- <30> D44 <30> BAV99W_SOT323 USB9+ USB9USB8+ USB8- 15K-8P4R 3VDUAL RN84 SMB_MEM_DATA SMBCLK SMBDATA SMB_MEM_CLK 3 C310 X_10P VCC3 3 USB_OC0* USB_OC1*/GPIO USB_OC2*/GPIO USB_OC3*/GPIO USB_OC4*/GPIO USB_RBIAS V4 V5 V3 V2 AA4 V9 USB_OC#1 USB_OC#3 USB_OC#5 USB_OC#7 USB_OC#9 R273 732R 1% R278 10K 2 4 6 8 D45 BAV99W_SOT323 <26> <30> <26> <30> <30> D 1 3 5 7 VCC_DDR 3VDUAL C 2.7K-8P4R EXTSMI# R618 4.7K THRM# R619 4.7K SLP_S5# SLP_S3# SIO_PME# R I# R639 R640 R641 R642 X_10K X_10K 10K 10K 3VDUAL 3VDUAL VCC3 L25 +3.3V_PLL_DUAL R282 X_10K R284 10K R502 X_10K R503 10K R507 X_10K SPDIF0 (SIO CLK) AC_RST* 0=MII 1=RGMII* R508 10K 1=24MHz* 0=14.318MHz AB7 AC7 <25> 0=DISABLE_TERM(100ohm PCIE _REF) 1=ENABLE_TERM* 1=EXTERNAL* 0=INTERNAL GPO_SLI R509 3VDUAL 10K DEFAULT=* R288 <21> 10K RTC_RST- AG8 AB2 AB3 AC2 AB1 GPIO_1 GPIO_2/CPU_SLP* GPIO_3/CPU_CLKRUN* GPIO_4/SUS_STAT* GPIO_5/SYS_ERR* AE6 AF6 AD6 AH6 AE2 LID*/GPIO SLP_DEEP* V3P3_DEEP LLB* RTC_RST* VCC3 VCC3 L26 R2506 10K X_F301S0805 CP25 X_COPPER 3VDUAL SPDIF1 (REF CLK) <4> MEM_GPIO1 <4> MEM_GPIO2 <33> BIOS_WP# <29> LAN_RST# AC_SDOUT CP24 X_COPPER C300 C2698 C2697 103P 102P X_10U/0805 SPDIF0/GPIO SPDIF1/GPIO AC_SYNC 0=Normal operation* 1=Slave mode X_F301S0805 A29 R504 X_10K SPDIF_OUT SPDIF1 B USB0+ USB0- 1 VCC3 M II_CRS R GMIIPWDN# G/MII_TXD0 G/MII_TXD1 G/MII_TXD2 G/MII_TXD3 G/MII_TXCLK G_TXCTL/MII_TXEN 1 R181 1.47K 1% H28 J27 J28 J29 H26 J26 2 R498 <29> RGMII_TXCLK R499 <29> RGMII_TXCTL <29> RGMII_RX[3..0] RGMIITX0 RGMIITX1 RGMIITX2 RGMIITX3 RGMIITXCLK RGMIITXCTL R180 2.4K 1% AC_RST# 15K-8P4R RN85 1 3 5 7 SEC 5 OF 7 3VDUAL <31> 2 4 6 8 2 D USB2+ USB2USB3USB3+ U16E PLACE NEAR CK8-04 1 3 5 7 10K 22R-8P4R R617 X_4.7K 2 4 6 8 AH1 C498 C2699 0.1u 0402103P C2700 +3.3V_PLL_USB A20GATE/GPIO INTRUDER* EXT_SMI*/GPIO RI*/GPIO SPKR PWRBTN* SIO_PME*/GPIO KBRDRSTIN*/GPIO SMB_CLK0/GPIO SMB_DATA0/GPIO SMB_CLK1/GPIO SMB_DATA1/GPIO +3.3V_VBAT BUF_SIO_CLK SUSCLK/GPIO THERM*/GPIO RSTBTN* SLP_S5* SLP_S3* PWRGD_SB PWRGD FANRPM/GPIO FANCTL0/GPIO FANCTL1/GPIO TEST AG7 AK3 AH5 AJ3 AF3 AJ2 AJ5 AF2 Y3 W4 W2 W3 AH4 AF1 AG5 AD4 AJ6 AJ7 AH7 AG3 AC4 AA3 AA2 AB4 AE5 A20GATE IN TRUDER# EXTSMI# R I# SPKR PWRBTN# SIO_PME# KBRST# SMB_MEM_CLK SMB_MEM_DATA SMBCLK SMBDATA <33> EXTSMI# <39> R266 1M SPKR <39> PWRBTN# <33,39> SIO_PME# <33> KBRST# <33> SMB_MEM_CLK <8,9,10> SMB_MEM_DATA <8,9,10> SMBCLK <22,23,24,25,27,33,36> SMBDATA <22,23,24,25,27,33,36> VBAT VBAT R269 SLP_S5# SLP_S3# RSMRST# ATX_PWR_OK THRM# FP_RST# <33> <39> SLP_S5# SLP_S3# RSMRST# ATX_PWR_OK <16,33,36> <33,36> <36> <36,39> 22 SIO_24M SIO_24M <33> B C312 X_10P R259 THRM# FP_RST# X_22 SUSCLK SUSCLK <33> C302 X_10P SPEAKER STRAOS ROM TABLE SELECT VCC3 0=USER 1=SAFE (DEFAULT) CK8-04 SLI R281 1K X_10U/0805 A20GATE R510 1K Giga-Lan not use, pulldown below SPKR R621 MII_VREF X_10K MEM_GPIO1 2 4 6 8 RN580 RGMIITXCLK 1 RGMII_RXCTL 3 RGMII_RXCLK 5 MII_MDC 7 X_10K-8P4R 2 4 6 8 RN581 1 3 5 7 X_10K-8P4R A R511 X_1K A RGMII_RX1 RGMII_RX3 RGMII_RX2 RGMII_RX0 Micro Star Restricted Secret Title R ev NVIDIA CrushK8-04 Part 5 Document Number MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 2 0A MS-9620 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 17 44 5 4 D 3 2 1 D BGA740_CRUSHK8_04 U16B SEC 2 OF 7 C <23> <23> <23> <23> <23> <23> <23> <23> <25> <25> <25> <25> <25> <25> <25> <25> PED_RX0 PED_RX1 PED_RX2 PED_RX3 PED_RX4 PED_RX5 PED_RX6 PED_RX7 PED_RX8 PED_RX9 PED_RX10 PED_RX11 PED_RX12 PED_RX13 PED_RX14 PED_RX15 <23> <23> <23> <23> <23> <23> <23> <23> <25> <25> <25> <25> <25> <25> <25> <25> PED_RX0PED_RX1PED_RX2PED_RX3PED_RX4PED_RX5PED_RX6PED_RX7PED_RX8PED_RX9PED_RX10PED_RX11PED_RX12PED_RX13PED_RX14PED_RX15- <25> PE0_PRSNT- R471 VCC3 <24> <24> PED_RX0 PED_RX1 PED_RX2 PED_RX3 PED_RX4 PED_RX5 PED_RX6 PED_RX7 PED_RX8 PED_RX9 PED_RX10 PED_RX11 PED_RX12 PED_RX13 PED_RX14 PED_RX15 H18 F18 J18 H16 E16 D14 J16 H14 E13 H12 E12 J11 D10 H10 F10 E8 PE0_RX0 PE0_RX1 PE0_RX2 PE0_RX3 PE0_RX4 PE0_RX5 PE0_RX6 PE0_RX7 PE0_RX8 PE0_RX9 PE0_RX10 PE0_RX11 PE0_RX12 PE0_RX13 PE0_RX14 PE0_RX15 PED_RX0PED_RX1PED_RX2PED_RX3PED_RX4PED_RX5PED_RX6PED_RX7PED_RX8PED_RX9PED_RX10PED_RX11PED_RX12PED_RX13PED_RX14PED_RX15- G18 E17 J17 G16 F16 E14 J15 G14 F14 G12 F12 J10 E10 G10 E9 F8 PE0_RX0* PE0_RX1* PE0_RX2* PE0_RX3* PE0_RX4* PE0_RX5* PE0_RX6* PE0_RX7* PE0_RX8* PE0_RX9* PE0_RX10* PE0_RX11* PE0_RX12* PE0_RX13* PE0_RX14* PE0_RX15* D22 PE0_PRSNT* D18 E18 PE1_RX PE1_RX* G22 PE1_PRSNT* 10K CK804 PE0_TX0 PE0_TX1 PE0_TX2 PE0_TX3 PE0_TX4 PE0_TX5 PE0_TX6 PE0_TX7 PE0_TX8 PE0_TX9 PE0_TX10 PE0_TX11 PE0_TX12 PE0_TX13 PE0_TX14 PE0_TX15 A18 A17 C17 C16 C15 C14 A14 B13 D13 D11 B11 B10 B9 C9 C8 C7 PED_TX0 PED_TX1 PED_TX2 PED_TX3 PED_TX4 PED_TX5 PED_TX6 PED_TX7 PED_TX8 PED_TX9 PED_TX10 PED_TX11 PED_TX12 PED_TX13 PED_TX14 PED_TX15 PE0_TX0* PE0_TX1* PE0_TX2* PE0_TX3* PE0_TX4* PE0_TX5* PE0_TX6* PE0_TX7* PE0_TX8* PE0_TX9* PE0_TX10* PE0_TX11* PE0_TX12* PE0_TX13* PE0_TX14* PE0_TX15* B18 B17 D17 D15 B15 B14 A13 C13 C12 C11 C10 A10 A9 D9 D8 B7 PED_TX0PED_TX1PED_TX2PED_TX3PED_TX4PED_TX5PED_TX6PED_TX7PED_TX8PED_TX9PED_TX10PED_TX11PED_TX12PED_TX13PED_TX14PED_TX15- PE0_REFCLK PE0_REFCLK* B19 C18 PE1_TX PE1_TX* D19 C19 PE1_REFCLK PE1_REFCLK* D21 C20 PED_TX0 PED_TX1 PED_TX2 PED_TX3 PED_TX4 PED_TX5 PED_TX6 PED_TX7 PED_TX8 PED_TX9 PED_TX10 PED_TX11 PED_TX12 PED_TX13 PED_TX14 PED_TX15 <23> <23> <23> <23> <23> <23> <23> <23> <25> <25> <25> <25> <25> <25> <25> <25> PED_TX0PED_TX1PED_TX2PED_TX3PED_TX4PED_TX5PED_TX6PED_TX7PED_TX8PED_TX9PED_TX10PED_TX11PED_TX12PED_TX13PED_TX14PED_TX15- <23> <23> <23> <23> <23> <23> <23> <23> <25> <25> <25> <25> <25> <25> <25> <25> C RN99 2 4 6 8 PE0_CLK PE0_CLK- R472 VCC3 F20 E20 PE2_RX PE2_RX* R473 10K F22 PE2_PRSNT* R739 X_0R PE3_RX PE3_RX- H20 G20 PE3_RX PE3_RX* E21 PE3_PRSNT* K19 J19 PE4_RX PE4_RX* <24> <24> VCC3 <25> PE2_PRSNT- PE2_RX PE2_RX- <24> PE3_RX <24> PE3_RXR474 R638 VCC3 10K 10K X_0R PE2_TX PE2_TX* B21 C21 PE2_REFCLK PE2_REFCLK* C24 D23 PE3_TX PE3_TX* C22 B22 PE3_REFCLK PE3_REFCLK* C23 B23 PE4_TX PE4_TX* A22 A21 PE_REFCLKIN PE_REFCLKIN* A25 B25 PE_CLK_TEST PE_CLK_TEST* C25 D24 PECLK_COMP_GND E24 PE1_TX PE1_TX- PE1_TX PE1_TX- <24> <24> PE1_CLK PE1_CLK- PE2_TX PE2_TX- PE3_TX PE3_TX- R695 40.2R 1% R479 10K <23,24,25> PE_RST- <23,24,25> PE_WAKE- VCC1_5 E22 E23 PE_RST* PE_WAKE* 0.1u 0402 L21 PE3_TX PE3_TX- <24> <24> RN101 2 4 6 8 PE2_CLK PE2_CLK- R693 40.2R 1% R696 40.2R 1% R694 40.2R 1% 33R-8P4R <24> <24> PE2_REFCLK PE2_REFCLK- 1 3 5 7 B NEAR CK8-04 R697 40.2R 1% TP29 TP30 PE2_REFCLK <25> PE2_REFCLK- <25> R698 40.2R 1% 499R 1% X_F301S0805 CP20 X_COPPER C470 C2701 103P A27 C2702 A28 +1.5V_PLL_PE_AVDD +1.5V_PLL_PE_DVDD VER:A02 change 499 ohm X_10U/0805 +3.3V_PLL_PE_CORE VCC1_5 C472 0.1u 0402 A PE4_TX PE4_TX- R480 <25> <25> <25> <25> <24> <24> B <24> PE4_RX <24> PE4_RX- PE0_REFCLK PE0_REFCLKPE1_REFCLK PE1_REFCLK- NEAR CK8-04 33R-8P4R PE1_RX PE1_RX- PE1_RX PE1_RX- <25> PE1_PRSNT- 3VDUAL PE0_REFCLK PE0_REFCLKPE1_REFCLK PE1_REFCLK- 1 3 5 7 C2705 103P B28 +1.5V_PLL_PE_CORE A26 GND_PLL_PE L22 B26 C2703 C2704 C471 103P 0.1u 0402 X_10U/0805 VCC3 X_F301S0805 CP21 X_COPPER C2706 X_10U/0805 A Micro Star Restricted Secret Title R ev NVIDIA CrushK8-04 Part 2 Document Number MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 2 0A MS-9620 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 18 44 5 4 3 2 1 VCC3 U16C BGA740_CRUSHK8_04 PEX REFCLKIN FREQ SEC 3 OF 7 <22,27,34> AD[31..0] D AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 AD16 AD17 AD18 AD19 AD20 AD21 AD22 AD23 AD24 AD25 AD26 AD27 AD28 AD29 AD30 AD31 H7 K7 J2 L9 J3 J5 H8 H6 K8 J4 H3 G5 G6 G7 H4 G3 C2 C1 D2 C3 B2 D3 E3 E4 B4 A3 A4 B3 C4 C5 A5 D5 C_BE#0 C_BE#1 C_BE#2 C_BE#3 J1 G2 F3 D4 PCI_CBE0* PCI_CBE1* PCI_CBE2* PCI_CBE3* F4 D1 E2 F2 E1 G4 F5 F6 P6 N4 PCI_FRAME* PCI_IRDY* PCI_TRDY* PCI_STOP* PCI_DEVSEL* PCI_PAR PCI_PERR*/GPIO PCI_SERR* PCI_PME*/GPIO PCI_CLKRUN*/GPIO PCI_AD0 PCI_AD1 PCI_AD2 PCI_AD3 PCI_AD4 PCI_AD5 PCI_AD6 PCI_AD7 PCI_AD8 PCI_AD9 PCI_AD10 PCI_AD11 PCI_AD12 PCI_AD13 PCI_AD14 PCI_AD15 PCI_AD16 PCI_AD17 PCI_AD18 PCI_AD19 PCI_AD20 PCI_AD21 PCI_AD22 PCI_AD23 PCI_AD24 PCI_AD25 PCI_AD26 PCI_AD27 PCI_AD28 PCI_AD29 PCI_AD30 PCI_AD31 CK804 PCI_REQ0* PCI_REQ1* PCI_REQ2*/GPIO PCI_REQ3*/GPIO PCI_REQ4*/GPIO N5 N9 M9 M8 P5 5705REQ* 1394REQ* PCI1REQ* SPC IREQ* PCI_GNT0* PCI_GNT1* PCI_GNT2*/GPIO PCI_GNT3*/GPIO PCI_GNT4*/GPIO M7 M6 M5 K4 P7 5705GNT* 1394GNT* PCI1GNT* PCI_INTW* PCI_INTX* PCI_INTY* PCI_INTZ* B5 E6 E5 D6 PC I_INTA* PC I_INTB* PCI_INTC* PCI_INTD* PCI_CLK0 PCI_CLK1 PCI_CLK2 PCI_CLK3 PCI_CLK4 PCI_CLK5 PCI_CLKFB K3 L2 K2 K5 L3 L4 M3 PCICLK0 PCICLK1 PCICLK2 AUDCLK CLK_MS1 PCI_CLK5 PCI_CLKFB 5705REQ* 1394REQ* PCI1REQ* SPCIREQ* <22,27> <22,34> <22> <22> 5705GNT* 1394GNT* PCI1GNT* SPCIGNT* <27> <34> <22> <22> R481 X_8.2K D 1=200MHz 0=100MHz PCI_INTA* PCI_INTB* PCI_INTC* PCI_INTD* RN83 2 4 6 8 R276 R482 8.2K <22> <22> <22,27> <22,34> 22R-8P4R PCICLK_1394 1 PCICLK_5705 3 5 PCICLK_SLOT1 7 PCICLK_1394 <34> PCICLK_5705 <27> SPCICLK <22> PCICLK_SLOT1 <22> CN8 PCICLK1 PCICLK_SLOT1 PCICLK_5705 PCICLK_1394 22 <22,27,34> FRAME# <22,27,34> IR D Y# <22,27,34> TRDY# <22,27,34> STOP# <22,27,34> DEVSEL# <22,27,34> PAR <22,27> SERR# <22,27,34> PERR# <22,27,34> PME# 3VDUAL VCC3 R286 8.2K PME# R272 8.2K PCI_CLKRUN# <22> PCIRST_SLOT1-2* <27> PCIRST_5705* <36> MS6_RST* <34> 1394_RST* B <33> SIO_RST* FRAME# IR D Y# TRDY# STOP# DEVSEL# PAR SERR# PERR# PME# PCI_CLKRUN# R483 33 N2 PCI_RESET0* R484 33 N1 PCI_RESET1* R255 33 N3 PCI_RESET2* R486 33 AF16 PCI_RESET3* R488 33 AE7 LPC_RESET* 2 4 6 8 X_8P4C-10P C <22,27,34> C_BE#[3..0] 1 3 5 7 AF9 AE10 AD10 AC10 LPC_AD0 LPC_AD1 LPC_AD2 LPC_AD3 LPC_FRAME* LPC_DRQ0* LPC_CS*/DRQ1* SERIRQ AC8 AF7 AH8 AD8 LPC_FRAME# LPC_DRQ#0 FLASH_CS# SERIRQ LPC_PWRDWN*/GPIO AE8 LPC_AD0 LPC_AD1 LPC_AD2 LPC_AD3 LPC_AD[3..0] <33> PCI_CLK5 C473 X_10P CLK_MS1 C725 X_10P LPC_DRQ#0 FLASH_CS# SERIRQ R252 R254 R257 8.2K 8.2K 10K C VCC3 LPC_FRAME# <33> LPC_DRQ#0 <33> SERIRQ <33> LPC_CLK0 AB10 SIOPCLK R485 22 LPC_CLK1 AB11 LPCPCLK R487 22 SIO_PCLK <33> LPC_PCLK <33> VCC3 B C474 X_10P CK8-04 SLI 1: command mode above VDD/2 0: command mode below VDD/2 C475 X_10P R489 X_8.2K <33> LPC_FRAME# R490 8.2K A A Micro Star Restricted Secret Title R ev NVIDIA CrushK8-04 Part 3 Document Number MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 2 0A MS-9620 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 19 44 5 4 3 2 1 U16D PLACE CONNECTOR SATA3 GND HT+ HTGND HRHR+ GND D 1 2 3 4 5 6 7 SATA con SATA4 GND 1 HT+ 2 HT- 3 GND 4 HR- 5 HR+ 6 GND 7 SATA con SATA1 GND 1 HT+ 2 HT- 3 GND 4 HR- 5 HR+ 6 GND 7 SATA con SATA2 GND 1 HT+ 2 HT- 3 GND 4 HR- 5 HR+ 6 GND 7 C SEC 4 OF 7 TXP0 TXN0 C476 C477 103P 103P AK9 AJ9 SP_TXP0 SP_TXN0 RXN0 RXP0 C478 C479 103P 103P AJ10 AH10 SP_RXN0 SP_RXP0 TXP1 TXN1 C480 C481 103P 103P AJ11 AH11 SP_TXP1 SP_TXN1 RXN1 RXP1 C482 C483 103P 103P AG11 AH12 SP_RXN1 SP_RXP1 TXP2 TXN2 C484 C485 103P 103P AG13 AH13 SP_TXP2 SP_TXN2 RXN2 RXP2 C486 C487 103P 103P AK13 AJ13 SP_RXN2 SP_RXP2 TXP3 TXN3 C488 C489 103P 103P AJ14 AH14 SP_TXP3 SP_TXN3 RXN3 RXP3 C490 C491 103P 103P AJ15 AH15 SP_RXN3 SP_RXP3 CK804 SATA con <39> SATA_LED SATA_LED TP31 TP32 SP_TSTCLKN SP_TSTCLKP TP33 SP_ATEST AA14 SP_LED*/GPIO AD14 AE14 AF14 AG14 SP_REFCLKN SP_REFCLKP SP_TSTCLKN SP_TSTCLKP AF13 SP_ATEST AC14 AB14 SP_TERMP SP_TERMN R491 2.49K 1% VCC1_5 L23 X_F301S0805 AG12 AF12 +1.5V_PLL_SP_DVDD +1.5V_PLL_SP_AVDD AE12 +1.5V_PLL_SP_CORE CP22 X_COPPER C493 0.1u 0402 C671 103P C670 X_10U/0805 C494 0.1u 0402 C672 103P C675 X_10U/0805 VCC1_5 PDD0 PDD1 PDD2 PDD3 PDD4 PDD5 PDD6 PDD7 PDD8 PDD9 PDD10 PDD11 PDD12 PDD13 PDD14 PDD15 IDE_DATA_P0 IDE_DATA_P1 IDE_DATA_P2 IDE_DATA_P3 IDE_DATA_P4 IDE_DATA_P5 IDE_DATA_P6 IDE_DATA_P7 IDE_DATA_P8 IDE_DATA_P9 IDE_DATA_P10 IDE_DATA_P11 IDE_DATA_P12 IDE_DATA_P13 IDE_DATA_P14 IDE_DATA_P15 AE20 AA17 AB18 AD18 AE18 AJ17 AG17 AD17 AB17 AH17 AK17 AF18 AC18 AG18 AF20 AD20 IDE_ADDR_P0 IDE_ADDR_P1 IDE_ADDR_P2 AH20 AH19 AG21 PD_A0 PD_A1 PD_A2 <35> <35> <35> IDE_CS1_P* IDE_CS3_P* IDE_DACK_P* IDE_IOW_P* IDE_INTR_P IDE_DREQ_P IDE_IOR_P* IDE_RDY_P CBL_DET_P AH21 AJ21 AH18 AB20 AJ19 AC20 AA19 AJ18 AG19 PD_CS#1 PD_CS#3 PD_DACK# PD_IOW# IRQ14 PD_DREQ PD_IOR# PD _IORDY PD_DET <35> <35> <35> <35> <35> <35> <35> <35> <35> IDE_DATA_S0 IDE_DATA_S1 IDE_DATA_S2 IDE_DATA_S3 IDE_DATA_S4 IDE_DATA_S5 IDE_DATA_S6 IDE_DATA_S7 IDE_DATA_S8 IDE_DATA_S9 IDE_DATA_S10 IDE_DATA_S11 IDE_DATA_S12 IDE_DATA_S13 IDE_DATA_S14 IDE_DATA_S15 AG24 AG23 AJ23 AJ22 AF22 AB21 AF21 AK21 AG22 AD22 AE22 AC22 AH22 AH23 AH24 AF24 IDE_ADDR_S0 IDE_ADDR_S1 IDE_ADDR_S2 AJ28 AJ27 AH26 SD_A0 SD_A1 SD_A2 <35> <35> <35> IDE_CS1_S* IDE_CS3_S* IDE_DACK_S* IDE_IOW_S* IDE_INTR_S IDE_DREQ_S IDE_IOR_S* IDE_RDY_S CBL_DET_S AG26 AH27 AK26 AE24 AJ26 AF23 AH25 AJ25 AK28 SD_CS#1 SD_CS#3 SD_DACK# SD_IOW# IRQ15 SD_DREQ SD_IOR# SD _IORDY SD_DET <35> <35> <35> <35> <35> <35> <35> <35> <35> PDD[0..15] <35> D SDD0 SDD1 SDD2 SDD3 SDD4 SDD5 SDD6 SDD7 SDD8 SDD9 SDD10 SDD11 SDD12 SDD13 SDD14 SDD15 SDD[0..15] <35> C B B VCC3 L24 VCC3 AD13 +3.3V_PLL_SP_CORE AF11 GND_PLL_SP IDE_COMP_3P3V IDE_COMP_GND AD16 AE16 XTALIN XTALOUT AJ29 AH29 R492 R493 121R 1% 121R 1% X_F301S0805 CP23 X_COPPER C495 0.1u 0402 C673 103P C676 X_10U/0805 AF5 AG4 Y8 XTALIN_RTC XTALOUT_RTC C496 18p C497 18p 25MHz DIP CK8-04 SLI C319 18p 2 1 C321 18p Y5 32.768 KHz DIP A A Micro Star Restricted Secret Title R ev NVIDIA CrushK8-04 Part 4 Document Number MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 2 0A MS-9620 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 20 44 5 4 3 2 1 VCC1_5 VCC5 U16F B A D25 G21 D20 E19 G19 J20 G17 D16 E15 G15 G13 J14 J13 J12 D12 GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_DGND PE_DGND PE_DGND PE_DGND PE_DGND PE_DGND PE_DGND PE_DGND PE_DGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND PE_AGND M27 M4 N12 F7 N14 N15 N16 N17 N18 N19 AA24 N24 N7 N10 P1 P10 P12 P13 P14 P15 P16 P17 P18 P19 R24 R21 R12 R13 R14 R15 R16 R17 R18 R19 U21 R26 R5 R7 R9 T10 T12 T13 T14 T15 T16 T17 T18 T19 J7 T27 T4 U12 U13 U14 U15 U16 U17 U18 U19 U7 U9 V1 V10 V12 V13 V14 V15 V16 V17 V18 V19 M10 K6 H5 M14 M15 M16 M17 M18 M19 N13 L7 E11 G11 G9 G8 B6 D7 E7 K18 K17 K16 K15 K14 K13 K12 K11 K10 VCC1_5 L27 X_220ohm_3000mA L28 X_220ohm_3000mA C609 102p CP26 X_COPPER C610 0.1u 0402 C611 0.1u 0402 K20 F25 D27 E26 B30 G24 D28 C29 J21 +1.5V +1.5V +1.5V +1.5V +1.5V +1.5V +1.5V +1.5V +1.5V D30 K21 C30 H24 E27 J22 F26 E28 J24 K23 D29 L22 G25 K22 G26 F27 L21 +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D +1.5V_PE_D H22 C28 B29 D26 F24 G23 E25 B27 C26 C27 +1.5V_PE_A +1.5V_PE_A +1.5V_PE_A +1.5V_PE_A +1.5V_PE_A +1.5V_PE_A +1.5V_PE_A +1.5V_PE_A +1.5V_PE_A +1.5V_PE_A AD15 AA15 AB15 AF15 +1.5V_SP_A +1.5V_SP_A +1.5V_SP_A +1.5V_SP_A Y21 VCC1_5 CP27 X_COPPER SEC 7 OF 7 CK804 +1.5V_SP_D +1.5V_SP_D AG2 AG1 +1.5V_DUAL +1.5V_DUAL AH30 A6 AA20 AA18 U10 R10 J9 L10 Y10 W10 AA11 +1.2V_HT +1.2V_HT +1.2V_HT +1.2V_HT +1.2V_HT N21 P21 T21 V21 W21 +3.3V_DUAL +3.3V_DUAL +3.3V_DUAL +3.3V_DUAL AB9 Y9 P4 M21 +3.3V_USB_DUAL +3.3V_USB_DUAL AF4 T9 R404 R701 SP_AGND SP_AGND SP_AGND SP_AGND SP_AGND SP_AGND AG15 AH16 AK14 AB13 AG16 AA13 SP_DGND SP_DGND AD12 AC12 100R 100R D VCC3 C499 0.1u 0402 C677 0.1u 0402 VDD_12_A 3VDUAL C501 0.1u 0402 +1.5V_PLL_HT AA12 AB12 +5V +5V +3.3V +3.3V +3.3V +3.3V +3.3V +3.3V +3.3V +3.3V +3.3V C502 0.1u 0402 C VCC1_5 C612 0.1u 0402 C614 X_0.1u 0603/B C616 X_0.1u 0603/B C618 10U/0805 CK8-04 SLI VDD_12_A VCC3 C2693 C674 X_475P/0805 C505 0.1u 0402 C506 0.1u 0402 C507 0.1u 0402 B C2694 1_5VDUAL C2696 10U/0805 C2695 105p/B C2667 C2665 0.1u 0402 VBAT C2666 C2668 X_0.1u 0603/B C509 C2669 10U/0805 X_0.1u 0603/B R620 1M 0.1u 0402 105p/B X_0.1u 0603/B 0.1u 0402 VCC5_SB VBAT R395 R396 560R 1.5K R645 X_0 SW1 4 2 VDD_12_A 3 1 JBAT1 D14 S-BAT54C_SOT23 3 <17> VBAT1 RTC_RST- C465 X_0.1u 0402 X_1B-OFF-S-BK 1 2 3 C2672 C2670 0.1u 0402 HDR 1*3 C2671 C510 X_0.1u 0603/B0.1u 0402 C615 X_0.1u 0603/B C613 X_0.1u 0603/B JBAT1_1-2 2 1 R315 1K X_0.1u 0603/B Jumper-Green Battery Holder 1_5VDUAL A X_0.1u 0603/B C2675 C2673 0.1u 0402 CK8-04 SLI C508 C2674 X_0.1u 0603/B 0.1u 0402 C2676 105p/B C2677 10U/0805 Micro Star Restricted Secret Title R ev NVIDIA CrushK8-04 Part 6&7 Document Number 4 3 2 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 5 C617 105p/B L29 X_220ohm_2000mA 1 C AK10 AK27 AD7 AB5 A2 B1 K30 AA1 AH9 AA16 AK6 W24 U24 AF10 AC16 AB19 AB27 P27 AH2 AD19 AD21 R22 AE1 AE27 AE30 AE4 AB16 AF19 AG10 AG20 AG25 AH28 AH3 AJ1 AJ30 G27 AK18 AK2 AK22 AK25 AK29 AF17 AA7 C6 M12 W15 H25 V27 K1 W7 W12 W22 F1 AE25 F30 AG6 M13 W13 W17 M23 W26 AD23 W5 K9 AD9 AG9 W14 W18 AA21 W9 Y4 AF8 AA10 W16 W19 AA26 Y27 AD11 AB22 L24 L26 L5 2 D U16G SEC 6 OF 7 CK804 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 21 44 5 4 3 2 1 AD[31..0] <19,27,34> AD[31..0] C_BE#[3..0] <19,27,34> C_BE#[3..0] PCI SLOT 1 (PCI VER: 2.2 COMPLY) VCC3 -12V +12V <16> CPU_CLK <16> CPU_CLK# VCC3 PCI1 VCC5 USB_VCC <19> PCI_INTB* <19,34> PCI_INTD* <31> <31> VIDEOL VIDEOR <19> SPCICLK <19> PCICLK_SLOT1 <19> PCI1REQ* AD31 AD29 AD27 AD25 C_BE#3 AD23 AD21 AD19 AD17 C_BE#2 C IR D Y# <19,27,34> IR D Y# DEVSEL# <19,27,34> DEVSEL# LOCK# PERR# <19,27,34> PERR# <19,27> SERR# SERR# C_BE#1 AD14 AD12 AD10 TRST# +12V TMS TDI +5V INTA# INTC# +5V RESERVED +5V(I/O) RESERVED GND GND RESERVED RST# +5V(I/O) GNT# GND RESERVED AD30 +3.3V AD28 AD26 GND AD24 IDSEL +3.3 AD22 AD20 GND AD18 AD16 +3.3V FRAME# GND TRDY# GND STOP# +3.3V SDONE SBO# GND PAR AD15 +3.3V AD13 AD11 GND AD9 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31 A32 A33 A34 A35 A36 A37 A38 A39 A40 A41 A42 A43 A44 A45 A46 A47 A48 A49 SPCIGNT* VCC3 <19> PCI_INTA* <19> PCI_INTC* <19,27> VCC5 330 AD25 USB_VCC R2505 R1092 2.49KST PCIRST_SLOT1-2* <19> PCI1GNT* B52 B53 B54 B55 B56 B57 B58 B59 B60 B61 B62 AD5 AD3 AD1 ACK64# AD8 AD7 +3.3V AD5 AD3 GND AD1 +5V(I/O) ACK64# +5V +5V C/BE#0 +3.3V AD6 AD4 GND AD2 AD0 +5V(I/O) REQ64# +5V +5V A52 A53 A54 A55 A56 A57 A58 A59 A60 A61 A62 AD28 AD26 AD22 AD20 R1102 1K 5 6 AD18 AD16 9 TRDY# STOP# <19,27,34> TRDY# <19,27,34> STOP# <19,27,34> 10 4 3 R1105 SDONE SBO# 1 1K PAR AD15 PAR R1106 1K 2 11 18 19 24 25 28 <19,27,34> AD13 AD11 CPUCLK0_H CPUCLK0_L <5> <5> Q1 Q1* 21 20 CPUCLK1_H CPUCLK1_L <13> <13> CLK1 CLK1* Q2 Q2* 23 22 FB_IN FB_IN* 13 12 PLL_SEL VCC VCC VCCO VCCO VCCO VCCO VCCA C 7 8 R1103 120 R1107 49.9 R1104 120 R1108 49.9 R1109 49.9 AD6 AD4 C1337 103P AD2 AD0 C1338 103P C1339 103P C1340 103P C1341 103P C1342 103P C1343 103P C1344 103P REQ64# R1110 <19> PCI1REQ* <19,27> 5705REQ* <19> RN94 8.2K-8P4R MR SEL1 SEL0 17 16 B 49.9 C1345 103P C1346 103P VCC3 PCI SLOT DECOUPLING CAPACITORS + RN93 8.2K-8P4R CLK_SEL R1100 120 Q0 Q0* CLOCK BUFFER SPCIREQ* <19,34> 1394REQ* 8.2K 8.2K R2521 8.2K R890 8.2K R295 8.2K R310 8.2K VCC3 EC2023 1000u VCC3 3VDUAL C326 X_0.1u 0402 C286 X_0.1u 0402 C416 X_0.1u 0402 C285 X_0.1u 0402 C325 0.1u 0402 C336 X_0.1u 0402 C335 X_0.1u 0402 C394 X_0.1u 0402 for EMI REQ64# A R2484 R2485 VCC5 EC53 1000u + VCC3 CLK0 CLK0* 120ohm-600mA C_BE#0 VCC5 1 3 5 7 1 3 5 7 R1099 120 VCC3 PCI PULL-UP / DOWN RESISTORS 2 4 6 8 2 4 6 8 CPUCLK1_H CPUCLK1_L AD9 IDSEL = AD22 MASTER = PCI1REQ* PCI1GNT* DEVSEL# TRDY# IR D Y# FRAME# SERR# PERR# LOCK# STOP# 0 0 U59 R1101 1K FRAME# R2490 R2491 R1097 49.9 R1098 1.4K 1% 330 AD24 FRAME# CPUCLK0_H CPUCLK0_L VCC3 3900P AD24 I D1 R230 PCI Slot120 B R1096 49.9 <19,27,34> FB14 AD8 AD7 R1095 169 <19> PME# 0 0 3900P C1336 PME# AD30 R2488 R2489 R1093 X_49.9 R1094 X_49.9 C1335 3VDUAL D VSS VSS VSS VSS <19> SPCIREQ* D -12V TCK GND TDO +5V +5V INTB# INTD# PRSNT#1 RESERVED PRSNT#2 GND GND RESERVED GND CLK GND REQ# +5V(I/O) AD31 AD29 GND AD27 AD25 +3.3V C/BE#3 AD23 GND AD21 AD19 +3.3V AD17 C/BE#2 GND IRDY# +3.3V DEVSEL# GND LOCK# PERR# +3.3V SERR# +3.3V C/BE#1 AD14 GND AD12 AD10 GND 27 26 15 14 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 B17 B18 B19 B20 B21 B22 B23 B24 B25 B26 B27 B28 B29 B30 B31 B32 B33 B34 B35 B36 B37 B38 B39 B40 B41 B42 B43 B44 B45 B46 B47 B48 B49 ACK64# VCC5 VCC3 VCC3 A VCC3 RN92 <19,34> <19> <19,27> <19> PCI_INTD* PCI_INTB* PCI_INTC* PCI_INTA* 2 4 6 8 1 3 5 7 VCC3 C277 C339 C322 C349 C397 X_0.1u 0402 X_0.1u 0402 X_0.1u 0402 X_0.1u 0402 0.1u 0402 C395 C396 C249 C348 C377 0.1u 0402 X_0.1u 0402 X_0.1u 0402 X_0.1u 0402 X_0.1u 0402 C414 0.1u 0402 C412 X_0.1u 0402 C460 0.1u 0402 C461 X_0.1u 0402 8.2K-8P4R SDONE R340 SBO# R341 X_0R X_0R SMBCLK SMBDATA VCC5 <17,23,24,25,27,33,36> <17,23,24,25,27,33,36> VCC5 http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 2 Micro Star Restricted Secret Title PCI Slot 1 & 2 & 3 Document Number R ev 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw Last Revision Date: Tuesday, February 15, 2005 Sheet of 22 44 1 5 4 3 2 1 PCI-E *16 PCI_E1 +12V D <17,22,24,25,27,33,36> SMBCLK <17,22,24,25,27,33,36> SMBDATA VCC3 3VDUAL <18,24,25> PE_WAKE- B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 12V 12V RSVD GND SMCLK SMDAT GND 3.3V JTAG1 3.3VAUX WAKE# PRSNT1# 12V 12V GND JTAG2 JTAG3 JTAG4 JTAG5 3.3V 3.3V PWRGD A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 B12 B13 B14 B15 B16 B17 B18 RSVD GND HSOP0 HSON0 GND PRSNT2# GND GND REFCLK+ REFCLKGND HSIP0 HSIN0 GND A12 A13 A14 A15 A16 A17 A18 B19 B20 B21 B22 B23 B24 B25 B26 B27 B28 B29 B30 B31 B32 HSOP1 HSON1 GND GND HSOP2 HSON2 GND GND HSOP3 HSON3 GND RSVD PRSNT2# GND RSVD GND HSIP1 HSIN1 GND GND HSIP2 HSIN2 GND GND HSIP3 HSIN3 GND RSVD A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31 A32 B33 B34 B35 B36 B37 B38 B39 B40 B41 B42 B43 B44 B45 B46 B47 B48 B49 HSOP4 HSON4 GND GND HSOP5 HSON5 GND GND HSOP6 HSON6 GND GND HSOP7 HSON7 GND PRSNT2# GND RSVD GND HSIP4 HSIN4 GND GND HSIP5 HSIN5 GND GND HSIP6 HSIN6 GND GND HSIP7 HSIN7 GND A33 A34 A35 A36 A37 A38 A39 A40 A41 A42 A43 A44 A45 A46 A47 A48 A49 B50 B51 B52 B53 B54 B55 B56 B57 B58 B59 B60 B61 B62 B63 B64 B65 B66 B67 B68 B69 B70 B71 B72 B73 B74 B75 B76 B77 B78 B79 B80 B81 B82 HSOP8 HSON8 GND GND HSOP9 HSON9 GND GND HSOP10 HSON10 GND GND HSOP11 HSON11 GND GND HSOP12 HSON12 GND GND HSOP13 HSON13 GND GND HSOP14 HSON14 GND GND HSOP15 HSON15 GND PRSNT2# RSVD RSVD GND HSIP8 HSIN8 GND GND HSIP9 HSIN9 GND GND HSIP10 HSIN10 GND GND HSIP11 HSIN11 GND GND HSIP12 HSIN12 GND GND HSIP13 HSIN13 GND GND HSIP14 HSIN14 GND GND HSIP15 HSIN15 GND A50 A51 A52 A53 A54 A55 A56 A57 A58 A59 A60 A61 A62 A63 A64 A65 A66 A67 A68 A69 A70 A71 A72 A73 A74 A75 A76 A77 A78 A79 A80 A81 A82 VCC3 PE_RST- PLACE CONNECTOR <18> PED_TX0 <18> PED_TX0- PED_TX0 PED_TX0- C511 0.1u 0402 C512 0.1u 0402 PED_TX0C PED_TX0C- <25> PE0_CON_PRSNT- <18> PED_TX1 <18> PED_TX1<18> PED_TX2 <18> PED_TX2- C <18> PED_TX3 <18> PED_TX3- <18> PED_TX4 <18> PED_TX4<18> PED_TX5 <18> PED_TX5<18> PED_TX6 <18> PED_TX6<18> PED_TX7 PED_TX1 PED_TX1- C513 0.1u 0402 C514 0.1u 0402 PED_TX1C PED_TX1C- PED_TX2 PED_TX2- C515 0.1u 0402 C518 0.1u 0402 PED_TX2C PED_TX2C- PED_TX3 PED_TX3- C516 0.1u 0402 C517 0.1u 0402 PED_TX3C PED_TX3C- PED_TX4 PED_TX4- C519 0.1u 0402 C520 0.1u 0402 PED_TX4C PED_TX4C- PED_TX5 PED_TX5- C527 0.1u 0402 C528 0.1u 0402 PED_TX5C PED_TX5C- PED_TX6 PED_TX6- C529 0.1u 0402 C530 0.1u 0402 PED_TX6C PED_TX6C- PED_TX7 PED_TX7- C531 0.1u 0402 C532 0.1u 0402 PED_TX7C PED_TX7C- <18> PED_TX7- <25> PED16_TX8 <25> PED16_TX8- B <25> PED16_TX9 <25> PED16_TX9<25> PED16_TX10 <25> PED16_TX10<25> PED16_TX11 <25> PED16_TX11<25> PED16_TX12 <25> PED16_TX12<25> PED16_TX13 <25> PED16_TX13- <25> PED16_TX15 <25> PED16_TX15- PED_TX8C PED_TX8C- C537 0.1u 0402 C538 0.1u 0402 PED_TX9C PED_TX9C- C539 0.1u 0402 C540 0.1u 0402 PED_TX10C PED_TX10C- C541 0.1u 0402 C542 0.1u 0402 PED_TX11C PED_TX11C- C543 0.1u 0402 C544 0.1u 0402 PED_TX12C PED_TX12C- C545 0.1u 0402 C546 0.1u 0402 PED_TX13C PED_TX13C- C547 0.1u 0402 C548 0.1u 0402 PED_TX14C PED_TX14C- C549 0.1u 0402 C550 0.1u 0402 PED_TX15C PED_TX15C- <18,24,25> PLACE CONNECTOR PE0_CON_REFCLK <25> PE0_CON_REFCLK- <25> PED_RX0 PED_RX0- PED_RX1 PED_RX1PED_RX2 PED_RX2PED_RX3 PED_RX3- PED_RX4 PED_RX4PED_RX5 PED_RX5PED_RX6 PED_RX6PED_RX7 PED_RX7- PED_RX0 PED_RX0- <18> <18> PED_RX1 PED_RX1- <18> <18> PED_RX2 PED_RX2- <18> <18> PED_RX3 PED_RX3- <18> <18> PED_RX4 PED_RX4- <18> <18> PED_RX5 PED_RX5- <18> <18> PED_RX6 PED_RX6- <18> <18> PED_RX7 PED_RX7- <18> <18> PED16_RX8 PED16_RX8- <25> <25> PED16_RX9 PED16_RX9- <25> <25> PED16_RX10 PED16_RX10- <25> <25> PED16_RX11 PED16_RX11- <25> <25> PED16_RX12 PED16_RX12- <25> <25> PED16_RX13 PED16_RX13- <25> <25> PED16_RX14 PED16_RX14- <25> <25> PED16_RX15 PED16_RX15- <25> <25> C VCC3 VCC3 3VDUAL +12V C521 0.1u 0402 C522 0.1u 0402 C523 0.1u 0402 C524 0.1u 0402 C525 0.1u 0402 B C555 0.1u 0402 C557 0.1u 0402 C526 0.1u 0402 +12V VCC3 C556 0.1u 0402 + <25> PED16_TX14 <25> PED16_TX14- C535 0.1u 0402 C536 0.1u 0402 D +12V C533 0.1u 0402 C534 0.1u 0402 C558 0.1u 0402 EC58 CD470U16EL11.5 PCI-E *16 Slot A A Micro Star Restricted Secret Title R ev PCI EXPRESS X16 POARTA Document Number MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 2 0A MS-9620 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 23 44 5 4 3 2 1 PCIE1 PCI-E 8PORT +12V D <17,22,23,25,27,33,36> SMBCLK <17,22,23,25,27,33,36> SMBDATA VCC3 3VDUAL <18,23,25> PE_WAKE- PCI-E *4 <18> PE1_TX <18> PE1_TX- VCC3 C2679 0.1u 0402 C2680 0.1u 0402 C1302 0.1u16VC3KX7R <18> PE2_TX <18> PE2_TX- +12V 1 C1303 0.1u16VC3KX7R C1304 0.1u16VC3KX7R 2 TC1 470u16V <18> PE3_TX <18> PE3_TX- C2681 0.1u 0402 C2682 0.1u 0402 C2683 0.1u 0402 C2684 0.1u 0402 + C <18> PE4_TX <18> PE4_TX- C2685 0.1u 0402 C2686 0.1u 0402 3VDUAL C1305 0.1u16VC3KX7R C1306 10u6.3VC5MX5R B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 12V 12V RSVD GND SMCLK SMDATA GND 3.3V JTAG1 3.3VAUX WAKE_# PRSNT1_# 12V 12V GND JTAG2 JTAG3 JTAG4 JTAG5 3.3V 3.3V PWRGD A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 B12 B13 B14 B15 B16 B17 B18 RSVD GND HSOP0+ HSOP0GND PRSNT2_# GND GND REFCLK+ REFCLKGND HSIP0+ HSIP0GND A12 A13 A14 A15 A16 A17 A18 B19 B20 B21 B22 B23 B24 B25 B26 B27 B28 B29 B30 B31 B32 HSOP1+ HSOP1GND GND HSOP2+ HSOP2GND GND HSOP3+ HSOP3GND RSVD PRSNT2_# GND RSVD GND HSIP1+ HSIP1GND GND HSIP2+ HSIP2GND GND HSIP3+ HSIP3GND RSVD A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31 A32 PE2_CON_PRSNT- <25> +12V D VCC3 PE_RST- <18,23,25> PE2_CON_REFCLK <25> PE2_CON_REFCLK- <25> PE1_RX PE1_RX- PE1_RX PE1_RX- <18> <18> PE2_RX PE2_RX- <18> <18> PE3_RX PE3_RX- <18> <18> PE4_RX PE4_RX- <18> <18> C PE2_RX PE2_RXPE3_RX PE3_RXPE4_RX PE4_RX- PCI-E 8PORT B B 25 W limit +3.3V 3A +12V 2.1A +3.3VDUAL 375mA Micro-Star Int'l Co., Ltd. A A No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw Title PCI-E SLOT http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 Size A4 Document Number Rev Date: Tuesday, February 15, 2005 MS-9620 2 0A Sheet 24 1 of 44 5 4 3 2 PCI_E4 X PCI-E *8 D <17,22,23,24,27,33,36> SMBCLK <17,22,23,24,27,33,36> SMBDATA VCC3 3VDUAL <18,23,24> PE_WAKE- C619 C620 <23> PE0_CON_PRSNT- B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 12V 12V RSVD GND SMCLK SMDAT GND 3.3V JTAG1 3.3VAUX WAKE# PRSNT1# 12V 12V GND JTAG2 JTAG3 JTAG4 JTAG5 3.3V 3.3V PWRGD A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 B12 B13 B14 B15 B16 B17 B18 RSVD GND HSOP0 HSON0 GND PRSNT2# GND GND REFCLK+ REFCLKGND HSIP0 HSIN0 GND A12 A13 A14 A15 A16 A17 A18 HSOP1 HSON1 GND GND HSOP2 HSON2 GND GND HSOP3 HSON3 GND RSVD PRSNT2# GND RSVD GND HSIP1 HSIN1 GND GND HSIP2 HSIN2 GND GND HSIP3 HSIN3 GND RSVD HSOP4 HSON4 GND GND HSOP5 HSON5 GND GND HSOP6 HSON6 GND GND HSOP7 HSON7 GND PRSNT2# GND RSVD GND HSIP4 HSIN4 GND GND HSIP5 HSIN5 GND GND HSIP6 HSIN6 GND GND HSIP7 HSIN7 GND HSOP8 HSON8 GND GND HSOP9 HSON9 GND GND HSOP10 HSON10 GND GND HSOP11 HSON11 GND GND HSOP12 HSON12 GND GND HSOP13 HSON13 GND GND HSOP14 HSON14 GND GND HSOP15 HSON15 GND PRSNT2# RSVD RSVD GND HSIP8 HSIN8 GND GND HSIP9 HSIN9 GND GND HSIP10 HSIN10 GND GND HSIP11 HSIN11 GND GND HSIP12 HSIN12 GND GND HSIP13 HSIN13 GND GND HSIP14 HSIN14 GND GND HSIP15 HSIN15 GND <18> PE0_REFCLK <18> PE0_REFCLKX +12V Hold down pin VCC3 PE_RST- PE1_CON_PRSNT# PED8_TX1 PED8_TX1- C621 C622 0.1u 0402 0.1u 0402 PED8_TX1C PED8_TX1C- PED8_TX2 PED8_TX2- C623 C626 0.1u 0402 0.1u 0402 PED8_TX2C PED8_TX2C- PED8_TX3 PED8_TX3- C PED8_TX4 PED8_TX4- C624 C625 C627 C628 B19 B20 B21 B22 B23 B24 B25 B26 B27 B28 B29 B30 B31 B32 PED8_TX3C PED8_TX3C- 0.1u 0402 0.1u 0402 PED8_TX4C PED8_TX4C- 0.1u 0402 0.1u 0402 <18,23,24> PLACE CONNECTOR PED8_TX0C PED8_TX0C- 0.1u 0402 0.1u 0402 PE1_CON_PRSNT# J5 PLACE CONNECTOR PED8_TX0 PED8_TX0- PE1_CON_REFCLK PE1_CON_REFCLK- X_Hold down pin PCI_E3 +12V PED8_TX5 PED8_TX5- C629 C630 0.1u 0402 0.1u 0402 PED8_TXC5 PED8_TX5C- PED8_TX6 PED8_TX6- C631 C632 0.1u 0402 0.1u 0402 PED8_TX6C PED8_TX6C- PED8_TX7 PED8_TX7- C633 C634 0.1u 0402 0.1u 0402 PED8_TX7C PED8_TX7C- B33 B34 B35 B36 B37 B38 B39 B40 B41 B42 B43 B44 B45 B46 B47 B48 B49 B50 B51 B52 B53 B54 B55 B56 B57 B58 B59 B60 B61 B62 B63 B64 B65 B66 B67 B68 B69 B70 B71 B72 B73 B74 B75 B76 B77 B78 B79 B80 B81 B82 B <24> PE2_CON_REFCLK <24> PE2_CON_REFCLK- PE1_CON_REFCLK PE1_CON_REFCLK- <18> PE2_PRSNT<24> PE2_CON_PRSNT- PED8_RX0 PED8_RX0- A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31 A32 PED8_RX1 PED8_RX1PED8_RX2 PED8_RX2PED8_RX3 PED8_RX3<23> PE0_CON_REFCLK <23> PE0_CON_REFCLK- A33 A34 A35 A36 A37 A38 A39 A40 A41 A42 A43 A44 A45 A46 A47 A48 A49 PED8_RX4 PED8_RX4- PED8_RX0 PED8_RX0- From CK8-04 Pro PED8_RX1PED8_RX1 PED8_RX6 PED8_RX6- X4 X16 PED8_RX5 PED8_RX5- PRSNT# PE0_PRSNT# A50 A51 A52 A53 A54 A55 A56 A57 A58 A59 A60 A61 A62 A63 A64 A65 A66 A67 A68 A69 A70 A71 A72 A73 A74 A75 A76 A77 A78 A79 A80 A81 A82 REFCLK LANE TX/RX PE0_REFCLK PE1_REFCLK PE0_0-15 PE1_1-4 X8 PRSNT# REFCLK LANE TX/RX PE1_PRSNT# PE1_REFCLK PE0_0-7 PE0_PRSNT# PE0_REFCLK PE0_8-15 PED8_RX5PED8_RX5 PED8_RX6PED8_RX6 X4 PED8_RX7PED8_RX7 PE2_PRSNT# PE2_REFCLK PE1_1-4 <17> GPO_SLI PED8_TX0 PED8_TX0PED8_TX1 PED8_TX1- Connect to PCIE Slot PED8_TX2 PED8_TX2- X16 Naming VCC3 PED8_RX3PED8_RX3 PE1_PRSNT# X8 PCI-E *16 Slot VCC3 PED8_RX2PED8_RX2 PED8_RX4PED8_RX4 PED8_RX7 PED8_RX7- XX0_CON_XXXX X8 XX1_CON_XXXX X4 PED8_TX3 PED8_TX3- XX2_CON_XXXX PED8_TX4 PED8_TX4PED8_TX5 PED8_TX5- 3VDUAL PED8_TX6 PED8_TX6C635 0.1u 0402 C636 0.1u 0402 C637 0.1u 0402 C638 0.1u 0402 C639 0.1u 0402 1 NV-SLI Connector J6 C640 0.1u 0402 PED8_TX7 PED8_TX7- A <18> <18> PED_TX15PED_TX15 1 3 5 7 9 11 13 15 17 19 21 23 PE2_CON_REFCLK PE2_CON_REFCLK# GND PE2_CON_PRSNT# PE1_CON_PRSNT# GND GND PE1_REFCLK PE1_REFCLK# GND GND GND 25 27 29 31 33 35 KEY KEY KEY KEY KEY KEY 37 39 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79 81 83 85 87 89 91 93 95 97 99 101 103 105 107 109 111 113 115 117 119 121 123 125 127 129 131 133 135 137 139 141 143 145 147 149 151 153 155 157 159 161 163 165 167 169 171 173 175 177 179 181 183 185 187 189 191 193 195 197 199 201 203 205 207 209 211 213 215 217 219 221 223 225 227 229 231 233 235 237 239 241 GND RESERVED RESERVED GND RESERVED RESERVED GND RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED GND GND PE1_CON_REFCLK# PE1_CON_REFCLK GND PE0_X8_RX0 PE0_X8_RX0# GND PE0_X8_RX1# PE0_X8_RX1 GND PE0_X8_RX2# PE0_X8_RX2 GND PE0_X8_RX3# PE0_X8_RX3 GND PE0_X8_RX4# PE0_X8_RX4 GND PE0_X8_RX5# PE0_X8_RX5 GND GND PE0_X8_RX6# PE0_X8_RX6 GND GND RESERVED RESERVED RESERVED RESERVED RESERVED GND PE0_X8_RX7# PE0_X8_RX7 GND RESERVED RESERVED GND RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED PE0_X8_TX0 PE0_X8_TX0# GND PE0_X8_TX1 PE0_X8_TX1# GND PE0_X8_TX2 PE0_X8_TX2# GND PE0_X8_TX3 PE0_X8_TX3# GND PE0_X8_TX4 PE0_X8_TX4# GND PE0_X8_TX5 PE0_X8_TX5# GND PE0_X8_TX6 PE0_X8_TX6# GND PE0_X8_TX7 PE0_X8_TX7# GND GND PE0_TX15# PE0_TX15 GND PE2_PRSNT# GND GND GND GND PE2_REFCLK PE2_REFCLK# GND PE1_PRSNT# GND RESERVED RESERVED 2 4 6 8 10 12 14 16 18 20 22 24 KEY KEY KEY KEY KEY KEY 26 28 30 32 34 36 PE0_X16_RX8 PE0_X16_RX8# GND PE0_X16_RX9 PE0_X16_RX9# GND PE0_X16_TX10 PE0_X16_TX10# GND PE0_X16_RX11 PE0_X16_RX11# GND PE0_X16_RX12 PE0_X16_RX12# GND PE0_X16_RX13 PE0_X16_RX13# GND PE0_X16_RX14 PE0_X16_RX14# GND PE0_X16_RX15 PE0_X16_RX15# GND PE0_X16_TX8# PE0_X16_TX8 GND PE0_X16_TX9# PE0_X16_TX9 GND PE0_X16_TX10# PE0_X16_TX10 GND PR0_X16_TX11# PE0_X16_TX11 GND PE0_X16_TX12# PE0_X16_TX12 GND PE0_X16_TX13# PE0_X16_TX13 GND PE0_X16_TX14# PE0_X16_TX14 GND GND PE0_X16_TX15# PE0_X16_TX15 GND PE0_RX15# PE0_RX15 GND PE0_RX14# PE0_RX14 GND PE0_RX13# PE0_RX13 GND PE0_RX12# PE0_RX12 GND PE0_RX11# PE0_RX11 GND PE0_RX10# PE0_RX10 GND PE0_RX9# PE0_RX9 GND GND PE0_RX8# PE0_RX8 GND GND GND GND GND RESERVED RESERVED GND PE0_TX14# PE0_TX14 GND PE0_TX8 PE0_TX8# GND PE0_TX9 PE0_TX9# GND PE0_TX10 PE0_TX10# GND PE0_TX11 PE0_TX11# GND PE0_TX12 PE0_TX12# GND GND PE0_TX13 PE0_TX13# GND PE1_PRSNT- <18> PE1_REFCLK <18> PE1_REFCLK- <18> PE0_PRSNT- <18> PE2_REFCLK <18> PE2_REFCLK- <18> D 38 40 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80 82 84 86 88 90 92 94 96 98 100 102 104 106 108 110 112 114 116 118 120 122 124 126 128 130 132 134 136 138 140 142 144 146 148 150 152 154 156 158 160 162 164 166 168 170 172 174 176 178 180 182 184 186 188 190 192 194 196 198 200 202 204 206 208 210 212 214 216 218 220 222 224 226 228 230 232 234 236 238 240 242 PED16_RX8 PED16_RX8- <23> <23> PED16_RX9 PED16_RX9- <23> <23> PED16_RX10 PED16_RX10- <23> <23> PED16_RX11 PED16_RX11- <23> <23> PED16_RX12 PED16_RX12- <23> <23> PED16_RX13 PED16_RX13- <23> <23> PED16_RX14 PED16_RX14- <23> <23> PED16_RX15 PED16_RX15- <23> <23> PED16_TX8PED16_TX8 <23> <23> PED16_TX9PED16_TX9 <23> <23> PED16_TX10PED16_TX10 <23> <23> PED16_TX11PED16_TX11 <23> <23> PED16_TX12PED16_TX12 <23> <23> PED16_TX13PED16_TX13 <23> <23> PED16_TX14PED16_TX14 <23> <23> PED16_TX15PED16_TX15 <23> <23> PED_RX15PED_RX15 <18> <18> PED_RX14PED_RX14 <18> <18> PED_RX13PED_RX13 <18> <18> PED_RX12PED_RX12 <18> <18> PED_RX11PED_RX11 <18> <18> PED_RX10PED_RX10 <18> <18> PED_RX9PED_RX9 <18> <18> PED_RX8PED_RX8 <18> <18> PED_TX14PED_TX14 <18> <18> PED_TX8 PED_TX8- <18> <18> PED_TX9 PED_TX9- <18> <18> PED_TX10 PED_TX10- <18> <18> PED_TX11 PED_TX11- <18> <18> PED_TX12 PED_TX12- <18> <18> PED_TX13 PED_TX13- <18> <18> C B A NV-SLI Connector +12V Micro Star Restricted Secret Title + C641 0.1u 0402 5 C642 0.1u 0402 R ev PCI EXPRESS X1 POART EC66 CD470U16EL11.5 4 3 MS-9620 Document Number http://laptop-motherboard-schematic.blogspot.com/ Normal Mode = Low SLI Mode = High 2 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 1 0A Last Revision Date: Tuesday, February 15, 2005 Sheet 25 44 of 5 4 3 2 1 REAR USB PORT 5VDUAL USB_VCC2 F3 1.5A FUSE C111 0.1u 0402 + R631 5.1K 1% D <17> EC19 1000u/6.3V D USB_OC#5 USB_OC#5 R632 10K C112 0.1u 0402 STACKED USB CONNECTOR LAN_USB2A RN588 1 3 5 7 5 6 7 8 1 2 3 4 USB_D6USB_D6+ 2 4 6 8 USB_D7USB_D7+ UP D OWN 23 24 25 26 27 28 29 30 USB/LAN_TR 0-8P4R L33 C <17> <17> <17> <17> 8 7 6 5 USB6USB6+ USB7USB7+ USB_D6USB_D6+ USB_D7USB_D7+ 1 2 3 4 C USB_VCC2 5 X_CMC-L02-9007030-C71 6 4 USB_D7- USB_D6+ 1 3 USB_D7+ 2 USB_D6- 5VDUAL D49 X_IPC220CZ6 /SO6 KBVCC F2 1.5A FUSE R633 5.1K 1% B <17> USB_OC#1 C88 0.1u 0402 + R65 X_47K B EC13 1000u/6.3V USB_OC#1 CP1 C90 0.1u 0402 R634 10K X_COPPER KBVCC CP14 LAN_USB1A USB_D0USB_D0+ RN589 1 3 5 7 2 4 6 8 UP D OWN X_COPPER 5 23 24 25 26 27 28 29 30 USB_D0- 6 USB_D0+ 1 2 USB_D1USB_D1+ 5 6 7 8 1 2 3 4 4 USB_D1- 3 USB_D1+ D50 X_IPC220CZ6 /SO6 USB/LAN_TR 0-8P4R L34 A <17> <17> <17> <17> USB1USB1+ USB0USB0+ 8 7 6 5 1 2 3 4 VCC5 USB_D1USB_D1+ USB_D0USB_D0+ VCC5 A X_CMC-L02-9007030-C71 C138 X_0.1u 0402 Micro Star Restricted Secret C203 X_0.1u 0402 Title Document Number 4 3 2 R ev 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 5 Rear USB Port 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 26 44 5 4 VC C3 2 D VAUX_12 C_BE#0 C_BE#1 C_BE#2 C_BE#3 VAU XPRSNT J12 C3 J3 F2 F1 H3 H1 G3 J1 J2 A2 H2 C2 A3 A4 A6 <19,22,34> PME# 100 R1075 R1076 <17,22,23,24,25,33,36> SMBCLK <17,22,23,24,25,33,36> SMBDATA X_4.7K 100 LOW _PWR B C8 H4 A10 C9 M11 F4 J14 N11 N10 VAUX_25 E12 H5 H6 H7 H8 J5 J6 J7 J8 J9 J10 K5 K6 K7 K8 K9 K10 L5 L10 M14 N14 P8 P12 P13 P14 TRD[3]TRD[3]+ TRD[2]TRD[2]+ TRD[1]TRD[1]+ TRD[0]TRD[0]+ LINKLEDB SPD100LEDB SPD1000LEDB TRAFFICLEDB RDAC 15mm x 15mm BGA196 SPROMDOUT SPROMDIN SOLDER SIDE C1315 TRST# TDI TCK TMS TDO REGCTL25 REGSEN25 XTALVDD XTALI XTALO REGSEN12 REGCTL12 C1328 0.1u10VC2KX7R L7 K11 K4 J11 J4 H10 M8 L14 L11 Y9 25MHZ-18pf/30ppm P7 H14 L50 C1332 0.1u10VC2KX7R L8 M9 N8 PLLVDD3 PLLVDD2 SI SO SCLK CS# L8 M9 N8 B7 D4 D5 D6 D7 D8 D9 E2 E5 E6 E7 E8 E9 F5 F6 F7 F8 F9 F10 G4 G5 G6 G7 G8 G9 G10 H9 K2 L6 L9 M6 M12 M13 N1 N12 N13 C1334 0.1u10VC2KX7R C1314 VAUX_12 SOLDER SIDE 0.1u10VC2KX7R VAUX_25 0.1u10VC2KX7R C1313 0.1u10VC2KX7R L49 Place near GIGA-bits PCI controlor . 600OHM/100M C1316 F12 F13 VC C3 CLOSED TO CHIP VAUX_25 E14 LAN_B_M DIN3 E13 LAN_B_MDIP3 0.1u16VC3KX7R 0.1u10VC2KX7R D14 LAN_B_M DIN2 D13 LAN_B_MDIP2 C1317 C1321 C1323 C1318 C1320 C1324 0.1u16VC3KX7R C14 LAN_B_M DIN1 C13 LAN_B_MDIP1 C1322 0.1u10VC2KX7R 0.1u16VC3KX7R C1319 0.1u16VC3KX7R 0.1u10VC2KX7R B14 LAN_B_M DIN0 B13 LAN_B_MDIP0 SOLDER SIDE G13 H13 G12 G14 LAN_LINKB_100J LAN_LINKB_1000J LAN_AC T_BJ D10 R1068 1.24KR3F H12 K13 J13 EE WPJ M10 P10 EECLK EED ATA 3.3V 3.3mA 2.5V 230 mA 1.2V 312mA 3 VDUAL 3VDUAL R1070 N9 P9 R1071 R1072 U 53 1K D11 D12 C12 A12 B12 C 0.1u10VC2KX7R SOLDER SIDE R1073 EE WPJ 7 EECLK 6 EED ATA 5 EC100 100u25VEL 1 C11 VAUX_25_CTL VAUX_25 Q120 BCP69_X-F 1 B9 B10 Q119 BCP69_X-F VCC A0 WP# A1 SCL A2 SDA GND 1 2 3 4 AT24C128N/16K*8/10mS_X-F M33-2412803-A26 B11 C10 8 1K 3 VDUAL 4.7K VAUX_25 VAUX_12_CTL B C1326 C1325 0.1u10VC2KX7R 0.01u25VC3KX7R EC101 100u25VEL A9 L7 K11 K4 J11 J4 H10 M8 L14 L11 VAUX_12 R1077 X_300R3F 3VDUAL Near LAN Controllor R568 C1330 0.01u25VC3KX7R EC102 100u25VEL 330 C840 0.1u 0402 E10 G11 E11 H11 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS C1331 2.2u-0805 L51 C1312 1000P/50V/X7R 1K REGSUP12 27p50VC3JNPO 600OHM/100M EECLK EEDATA M66EN 27p50VC3JNPO VAUX_12 GPIO0 GPIO1 GPIO2 REGSUP25 C1329 600OHM/100M VC C3 0.1u10VC2KX7R AVDDL AVDDL CSTSCHG CLKRUN# SMB_CLK SMB_DATA LOW_PWR C1327 VAUX_12 C1311 + A D22R1074 0.1u10VC2KX7R 600OHM/100M 3 <19> PCICLK_5705 VAUXPRSNT REQ# GNT# FRAME# IRDY# DEVSEL# STOP# TRDY# PAR PERR# SERR# INTA# PCI_RST# PCI_CLK IDSEL PME# C1310 0.1u10VC2KX7R 0.1u10VC2KX7R P1 G2 A1 K14 L13 P11 A13 F14 C1309 L48 2 4 4.7K <19,22> 5705REQ* <19> 5705GNT* <19,22,34> FRAME# <19,22,34> I R D Y# <19,22,34> DEVSEL# <19,22,34> STOP# <19,22,34> T R D Y# <19,22,34> PAR <19,22,34> PE RR# <19,22> SE RR# <19,22> PCI_INTC* <19> PCIRST_5705* CBE_0# CBE_1# CBE_2# CBE_3# VDDP VDDP VDDP AVDD AVDD VAUX_12 C1308 3 VDUAL 3 R1069 3VDUAL M4 L3 F3 C4 VESD1 VESD2 VESD3 A14 A11 F11 K12 L12 2 4 <19,22,34> C_BE#[3..0] BIASVDD VDDIO VDDIO VDDIO VDDIO AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 AD16 AD17 AD18 AD19 AD20 AD21 AD22 AD23 AD24 AD25 AD26 AD27 AD28 AD29 AD30 AD31 VAUX_25 + C N7 M7 P6 P5 N5 M5 P4 N4 P3 N3 N2 M1 M2 M3 L1 L2 K1 E3 D1 D2 D3 C1 B1 B2 B4 A5 B5 B6 C6 C7 A8 B8 3 VDUAL 0.1u10VC2KX7R 0.1u10VC2KX7R B IASVDD VAUX_25 BCM5705 _ 3 VDUAL R1078 R1079 0R C573 0.1u 0402 LOW _PWR X_4.7K C1333 2.2u-0805 R567 0 C 574 X_C0.01U50X L ED_C LAN_AC T_BJ LP WR LAN_B_MDIP0 LAN_B_M DIN0 LAN_B_MDIP1 LAN_B_M DIN1 LAN_B_MDIP2 LAN_B_M DIN2 LAN_B_MDIP3 LAN_B_M DIN3 LG ND LAN_LINKB_1000J LAN_LINKB_100J LAN_USB2B 19 GREEN 20 ORANGE POWER 13 TD1+ 18 TD112 TD2+ 17 TD211 TD3+ 16 TD310 TD4+ 15 TD49 14 GND 21 AMBER 22 LEFT A D0 A D1 A D2 A D3 A D4 A D5 A D6 A D7 A D8 A D9 A D10 A D11 A D12 A D13 A D14 A D15 A D16 A D17 A D18 A D19 A D20 A D21 A D22 A D23 A D24 A D25 A D26 A D27 A D28 A D29 A D30 A D31 VAUX_25 600OHM/100M + <19,22,34> AD[31..0] C1307 VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDC VDDIO_PCI VDDIO_PCI VDDIO_PCI VDDIO_PCI VDDIO_PCI VDDIO_PCI VDDIO_PCI VDDIO_PCI VDDIO_PCI VDDIO_PCI A7 B3 C5 E1 E4 G1 K3 L4 N6 P2 L47 U 52 1 RIGHT D 3 USB/LAN_TR A VAUX_25 R2519 300 LAN_LINKB_1000J LAN_LINKB_100J LAN_AC T_BJ R2520 300 C2709 102P http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 A Micro-Star Int'l Co., Ltd. C2711 102P No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw C2712 102P Title BCM 5705 2 Size C Document Number Date: Tuesday, February 15, 2005 R ev 0A MS-9620 Sheet 1 27 of 44 5 4 3 2 1 D D CPU_FAN1 +12V 2 4 D40 X_1N4148_SOD123 4.7K R649 FAN CONTROL C643 X_0.1u 0402 FANPWM2 FANPWM1 +12V C645 0.1u 0402 C646 0.1u 0402 1 2 3 4 5 6 7 FAN1_IN FAN2_IN VCC12 C1 C2 CHRPMP GND FAN1_DRV FAN1_SEN FAN2_DRV FAN2_SEN FAN3_DRV FAN3_SEN FAN3_IN 14 13 12 11 10 9 8 <33> FAN CON R652 X_0R0805 U31 <33> <33> FANIO2 R650 10K 3 2 1 C644 0.1u 0402 R651 10K 27K C_FAN1 3 1 R648 Q70 N-APM2054N_SOT89 R653 6.49K 1% W83391TS C647 0.1u 0402 CPU_FAN2 C C +12V FANPWM3 2 4 <33> D41 R654 4.7K Q71 N-APM2054N_SOT89 R655 C648 X_0.1u 0402 FANIO1 3 2 1 C649 0.1u 0402 R657 10K 27K C_FAN2 3 1 X_1N4148_SOD123 <33> R656 10K FAN CON R658 X_0R0805 R659 6.49K 1% +12V 2 4 D56 B R2444 Q72 X_N-2N7002_SOT23 G C2662 X_0.1u 0402R2446 10K FANIO3 <33> B 3 2 1 C2661 0.1u 0402 D GPO12 S <33> 27K S_FAN1 3 1 X_1N4148_SOD123 R2443 4.7K Q2008 N-APM2054N_SOT89 R2445 10K FAN CON R2447 X_0R0805 D R2448 6.49K 1% +12V Q73 X_N-2N7002_SOT23 D57 2 4 R2450 C2663 X_0.1u 0402 A 3 2 1 D 5 CK_804_FAN R2451 10K A FAN CON +12V R2453 X_0R0805 Q2011 X_N-2N7002_SOT23 G 2 GPO14 S <33> C2664 0.1u 0402 R2452 10K 27K S_FAN2 3 1 X_1N4148_SOD123 R2449 4.7K Q2009 N-APM2054N_SOT89 CK_FAN 3 2 1 1 G + GPO17 S <33> EC68 X_CD100U16EL11 Micro Star Restricted Secret Title FAN CON Rev ICS9DB206 Document Number R2454 6.49K 1% MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 4 3 http://laptop-motherboard-schematic.blogspot.com/ 2 0A MS-9620 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 28 44 5 4 3 2 1 9VSB VCC_LAN 3VDUAL NEW BOM CHNAGE "I71-LM35803-T07" C208 0.1u 0402 TRUE C197 0.1u 0402 C169 0.1u 0402 G ND C199 0.1u 0402 G ND C182 0.1u 0402 G ND C180 0.1u 0402 G ND G ND C187 0.1u 0402 G ND C156 0.1u 0402 G ND 1K 3 + 2 - G ND U11A YLM358S-SOIC8 1 R172 C168 0.1u 0402 100RST 4.7K RGMII_TXCLK TRUE TRUE C185 X_10P C RGMII_RXCLK <17> RGMII_RXCLK <17> RGMII_RXCTL PLUMBING PLUMBING PLUMBING TRUE <17> RGMII_RX[3..0] R158 RGMII_RXCTL RGMII_RX0 RGMII_RX1 RGMII_RX2 RGMII_RX3 ? 22R R579 7 5 3 1 22R 8 6 4 2 RN579 22R-8P4R R149 X_0R 76 Y1 25MHz DIP 31 125CLK 77 C167 18P C165 18P NC FOR 25MHZ INPUT VCC_LAN 70 72 69 68 67 2 4 8 TCK TDO TMS TRSTn TDI 44 49 52 59 64 104 AVDD AVDD AVDD AVDD AVDD AVDD 73 89 97 5 11 30 122 2 6 12 17 23 27 78 85 90 96 117 118 34 71 VDDOX VDDOX 432R 1% 5 + 6 - R206 3.32K 1% MDI[0]+ MDI[0]- 41 42 A_MDI_0+ A_MDI_0- MDI[1]+ MDI[1]- 46 47 A_MDI_1+ A_MDI_1- MDI[2]+ MDI[2]- 56 57 A_MDI_2+ A_MDI_2- MDI[3]+ MDI[3]- 61 62 A_MDI_3+ A_MDI_3- RSET 39 RESETn 36 LAN_RST# COMA 37 M II_PWRDN MDC MDIO 35 33 7 1 U11B YLM358S-SOIC8 Q22 N-APM2054N_SOT89 VCC1_1 + SEL_FREQ R132 4.87K 1% GND C139 103P EC55 100UF/25V C R123 49.9R 1% R122 XTAL1 XTAL2 R202 VREF1_25 LED_DUP 10/100SEL LED_100 HSDACHSDAC+ COL CRS 75 LED_TX 91 92 95 98 99 100 54 53 7 RX_CLK 8 RX_ER RGMIIRXCTL UNNAMED_40_88E1111CAA_I627_RXDV 4 RX_DV RGMIIRX0 3 RXD0 RGMIIRX1 128 RXD1 RGMIIRX2 126 RXD2 RGMIIRX3 125 RXD3 124 RXD4 123 RXD5 121 RXD6 120 RXD7 114 115 <17> RGMII_25M TX_CLK GTX_CLK TX_ER TX_EN TXD0 TXD1 TXD2 TXD3 TXD4 TXD5 TXD6 TXD7 VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSSC CONFIG0 COMFIG1 CONFIG2 CONFIG3 CONFIG4 CONFIG5 CONFIG6 RGMII_TXCTL RGMII_TX0 RGMII_TX1 RGMII_TX2 RGMII_TX3 <17> RGMII_TXCTL <17> RGMII_TX[3..0] 10 14 13 16 18 19 20 24 25 26 28 29 S_OUTS_OUT+ LED_TX LED_RX LED_DUPLEX LED_LINK1000 LED_LINK100 LED_LINK10 9 15 21 22 38 40 43 45 48 51 55 58 60 63 65 66 83 84 93 94 101 102 106 108 111 103 116 119 127 1 74 88 87 86 82 81 80 79 <17> RGMII_TXCLK D EC35 100UF/25V GND 4 112 113 VDDOH VDDOH VDDOH S_CLKS_CLK+ VDDO VDDO VDDO VDDO S_INS_IN+ 109 110 DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD DVDD U8 105 107 VCC_LAN Q23 N-APM2054N_SOT89 + 9VSB TRUE 1 R203 100RST G ND R138 ? 2 4 R201 VREF1_25 C152 0.1u 0402 3 C223 0.1u 0402 D G ND C153 0.1u 0402 4 G ND C166 0.1u 0402 3 8 VCC1_1 49.9R 1% C140 103P R125 49.9R 1% R124 INTn 32 NC 50 MII_MDC MII_MDIO 49.9R 1% C141 103P C142 103P R139 X_4.7K R126 49.9R 1% R127 49.9R 1% G ND R128 49.9R 1% R129 49.9R 1% M88E1111 MII_MDC MII_MDIO LAN_RST# <17> <17> <17> RGMII_PWDN# <17> B LED_DUP 10/100SEL LED_TX VCC_LAN B R137 4.7K CP17 2 VCC_LAN 1 X_COPPER LED_TX R69 VCC_LAN C108 0.1u 0402 PHY HW CONFIG VCC_LAN PHY ADDRESS = 00001 ASYMMETRIC PAUSE ENABLED AUTO-NEG, ADVERTISE ALL MODES, PREFER MASTER RGMII ON COPPER ENERGY DETECT & COPPER/FIBER SELECT DISABLED MDC/MDIO MANAGEMENT SELECTED A R73 300 C95 102P LAN_USB1B 19 20 13 18 12 17 11 16 10 15 9 14 21 22 0R A_MDI_0+ A_MDI_0A_MDI_1+ A_MDI_1A_MDI_2+ A_MDI_2A_MDI_3+ A_MDI_3- 10/100SEL LED_100 R74 300 C97 102P AMBER+ AMBERNC TD1+ TD1TD2+ TD2TD3+ TD3TD4+ TD4- NC GREEN+ GREENUSB/LAN_TR C104 102P C102 102P A SEE 88E1111 DATASHEET DOC MV-S200649-00 REV A PP. 71-74 FOR DETAILS Micro Star Restricted Secret Title 88E1111CAA LAN Document Number 5 4 3 2 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ R ev 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 29 44 5 4 3 2 FRONT USB PORT 1 USB_VCC 5VDUAL F4 USB_VCC 1.5A FUSE If install JUSB2 must change FS5 to 2.6A <17> D + C841 X_0.1u 0402 C419 0.1u 0402 USB_VCC 5 EC50 1000u/6.3V USB_OC#7 USB_OC#7 RN585 1 3 5 7 USB_D3- 6 4 USB_D2- USB_D3+ 1 3 USB_D2+ R626 10K D D46 X_IPC220CZ6 /SO6 2 2 4 6 8 R625 5.1K 1% 0-8P4R L30 JUSB1 <17> <17> <17> <17> 1 2 3 4 USB3+ USB3USB2USB2+ USB_D3+ USB_D3USB_D2USB_D2+ 8 7 6 5 1 3 5 7 9 USB_D3USB_D3+ X_CMC-L02-9007030-C71 2 4 6 8 10 USB_D2USB_D2+ HDR 2*5(-9)-Yellow USB 2.0 PIN HEADER (Yellow) 5VDUAL F8 USB_VCC3 1.5A FUSE C C USB_VCC3 <17> + C417 EC2024 0.1u 0402 1000u/6.3V 5 2 4 6 8 R627 5.1K 1% RN586 1 3 5 7 USB_OC#3 USB_OC#3 0-8P4R USB_D4- 6 4 USB_D5- USB_D4+ 1 3 USB_D5+ 2 R628 10K D47 X_IPC220CZ6 /SO6 L31 <17> <17> <17> <17> 1 2 3 4 USB4USB4+ USB5USB5+ USB_D4USB_D4+ USB_D5USB_D5+ 8 7 6 5 JUSB2 1 3 5 7 9 USB_D4USB_D4+ X_CMC-L02-9007030-C71 2 4 6 8 10 USB_D5USB_D5+ HDR 2*5(-9)-Yellow USB 2.0 PIN HEADER (Yellow) B B USB_VCC1 5VDUAL F7 USB_VCC1 1.5A FUSE USB_VCC1 R629 5.1K 1% C598 0.1u 0402 + 2 4 6 8 <17> USB_OC#9 5 RN587 1 3 5 7 USB_OC#9 EC2025 USB_D8- 6 4 USB_D9- 1000u/6.3V USB_D8+ 1 3 USB_D9+ 2 R630 10K 0-8P4R D48 X_IPC220CZ6 /SO6 L32 <17> <17> <17> <17> A USB8USB8+ USB9USB9+ 8 7 6 5 1 2 3 4 USB_D8USB_D8+ USB_D9USB_D9+ JUSB3 1 3 5 7 9 USB_D8USB_D8+ X_CMC-L02-9007030-C71 2 4 6 8 10 USB_D9USB_D9+ A HDR 2*5(-9)-Yellow Micro Star Restricted Secret * USB Trace width : 7.5 mils * USB Trace Spacing : 20 mils * Differential USB Signlas Trace, Spacing : 7.5 mils 5 4 USB 2.0 PIN HEADER (Yellow) Document Number Front USB Port 2 R ev 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 3 Title 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 30 44 5 4 3 2 1 AUDIO CODEC AUDIO1B LINE_NEXT_R VCC3 AS 2.2U/0805 C2609 2.2U/0805 CEN-OUT 7 8 C2610 2.2U/0805 SROUT_R C2611 2.2U/0805 SROUT_L EC2018 C2614 X_104P default used external 14.318 C2615 X_104P ELS10/16/S LINE_OUT_R ELS10/16/S LINE_OUT_L C2612 C2613 100P 100P LINE_OUT 9 17 AUDIO_6CH + D 6 LINE_NEXT_L SPDIFO CODEC VCC3_3 NEED CAP CLOSE AS POSSIBLE. VCC3 C2608 LFE-OUT R2426 0/0805 +5VR D EC2019 + C2616 For EMI C2618 X_22P AC_SDIN0 <17> <17> AC_SYNC AC_RST# R2430 X_10K R2428 22 R2429 22 R2431 X_10K C2624 22P 1 C2620 X_680P C2621 X_680P 13 18 AUDIO_6CH VREFOUT C2625 104P EC2020 C2623 104P C2626 C2627 C2628 C2629 105P 102P 102P 55_105P AUDIO1A MIC2 ELS10/16/S 1 <22> VIDEOR 2.2U/0805 LIN2_R C2635 2.2U/0805 JD2 2.2U/0805 JD1 C2636 CP28 +12V R2434 1 3 VIN VOUT + C2640 104P AGND +5VR U2015 YLT1087S-0.8A R2435 2 3.3/1206 MIC2 2 L52 X_0 +12VR AGND C2638 1U/0805 C2639 X_103P CP29 C2631 X_680P 2 C2630 X_680P 4.7K 4.7K VCC5 C2637 X_103P X_COPPER R2433 MIC1 C2634 1U/0805 2 <22> VIDEOL C2633 1 LIN E_IN_R R2432 LIN2_L VREFOUT C 15 AUDIO_6CH EC2022 0/0805 ADJ 2.2U/0805 EC2021 10U/16V/S + R2436 10U/16V/S 100RST 1 C2632 5 3 1 1 LINE_IN_L 2 VREFOUT AC97CLK MIC_IN 16 MIC1 EMI <17> 14 2 4 ALC850 13 14 15 16 17 18 19 20 21 22 23 24 C 1U/0805 FR_MIC C2622 LINE_IN 2 36 35 34 33 32 31 30 29 28 27 26 25 1 LOUTR LOUTL SMC AVSS4/JS2 VRDA VRAD AFILT2 AFILT1 VREF_OUT VREF AVSS1 AVDD1 PHONE AUXL AUXR JS1 JS0 CDL CD_GND CDR MIC1 MIC2 LINL LINR <17> DVDD1 XTL_IN XTL_OUT DVSS1 SDATA_OUT BIT_CLK DVSS2 SDATA_IN DVDD2 SYNC RESET# PC_BEEP 11 12 LINE_IN_L + 1 2 3 4 5 6 7 8 9 10 11 12 10 2 104P R2427 X_10M LIN E_IN_R U2014 SPDIFO NC ID1# ID0# LFE_OUT CEN_OUT NC SROUT_R AVSS2 SROUT_L AVDD2 MONO C2619 X_24.576MHZ <17> AC_SDOUT <17> AC_BITCLK AUDIO1C 104P 48 47 46 45 44 43 42 41 40 39 38 37 C2617 X_22P Y10 C2641 104P X_COPPER B B C2643 C2644 104P 104P AUDIO1D SROUT_R 30 31 C2647 C2645 1U/0805 CD_GND C2646 1U/0805 C D_L 4 3 2 1 R2437 300RST CEN-OUT C2649 C2650 +5VR 102P 102P R2438 X_0 LINE_NEXT_L JAUDIO Remove R289 when install Front Audio C/W_OUT 28 23 AUDIO_6CH R2439 10K JAUD1 FR_MIC Remove R291 when install Front Audio LINE_OUT_R LINE_OUT_R 102P JCD1 YJ104-B JCD LINE_OUT_L 25 26 27 SR_OUT 32 33 AUDIO_6CH C2648 CD_R AUDIO1E LFE-OUT 29 SROUT_L C2642 1U/0805 R2440 X_0 LINE_NEXT_R R2441 10K 102P LINE_OUT_L 1 MIC AUD_GND 3 MIC_BIAS AUD_VCC 4 5 AUD_FPOUT_R AUD_RET_R 6 7 HP_ON 9 AUD_FPOUT_L +5VR SPDIFO SPDIFO C2655 C2657 1U/0805 R2442 X_200R1% X_102P 4 C2656 561P 1 4 1 LINE_OUT_L C2658 Title FR_MIC C2659 C2660 JAUD1(5-6) J7 X_102P X_102P YJUMPER-MG JACK-RCA2Pspring_black 3 JAUD1(9-10) X_102P http://laptop-motherboard-schematic.blogspot.com/ 4 LINE_NEXT_L C2651 C2652 X_102P X_102P Micro Star Restricted Secret LINE_OUT_R AUDIO_6CH 5 8 10 X_102P 3 2 AUDIO1F VCC 20 SPDIF_OUT 21 19 GND 22 GND 24 IOGND IOGND C2654 104P CUT AUD_RET_L +5VR LINE_NEXT_R C2653 JAUD1 only for full spec A 2 2 YJUMPER-MG Document Number ALC850 R ev 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 31 44 A 5 4 3 2 1 KB/MS/LPT/COM Port/FAN KBVCC VID[0..4] PS2 KEYBOARD & MOUSE CONNECTOR VCC2_5 2 4 6 8 C1 0.1u 0402 R1 1K RN1 4.7K-8P4R R1080 X_1K H 1_VID1 R1081 X_1K H 1_VID2 R1082 X_1K H 1_VID3 R1083 X_1K H 1_VID4 R1084 X_1K H 1_VID0 1 3 5 7 D JKBMS1 MSDATA <33> MSCLK KBDATA <33> KBCLK X_120ohm-600mA MS_DT MSCLK# FB2 X_120ohm-600mA MS_CK KBDAT# KBCLK# FB4 X_120ohm-600mA KB_DT FB3 X_120ohm-600mA KB_CK 7 8 11 12 10 MS 1 2 5 6 1 3 5 7 <33> FB1 CN1 8P4C-180P 9 4 H1_VID1 <13,37> H1_VID2 <13,37> H1_VID3 <13,37> H1_VID4 <13,37> H1_VID0 <13,37> D VCC5 VCC3 R1085 KB 3 1K KBMS CON 14 1 VID0 U54A 14 <33> MSDAT# <5,38> VID0 VID1 VID2 VID3 VID4 2 4 6 8 3 H 1_VID0 U55A <15> SKTOCC_1_L 2 7 1 D52 74LCX86-SO14 A VCC5 3 C 2 7 74F00-SOIC14 RSTB# <33> RAFD# <33> <33> RINIT# RSLIN# RSTB# 1 PRD0 3 RAFD# 5 PRD1 7 RN64 2 STB# 4 PR ND0 6 AFD# 8 PR ND1 33R-8P4R PRD2 1 PRD3 3 RINIT# 5 RSLIN# 7 RN62 2 PR ND2 4 PR ND3 6 PINIT# 8 SLIN# 33R-8P4R PR ND7 1 PR ND6 2 PR ND5 3 PR ND4 4 RSLCT 6 RPE 7 R B USY 8 RACK# 9 SLIN# PINIT# PR ND3 PR ND2 PR ND1 AFD# PR ND0 STB# 1 5 2 3 4 6 7 8 9 10 RERR# R38 FB11 SLIN# 1 2 3 4 6 7 8 9 1 5 2 3 4 6 7 8 9 10 5 D4 2 4 6 8 PARALLAL PORT CN4 8P4C-180P VID2 PR ND7 PR ND6 PR ND5 PR ND4 7 5 3 1 8 6 4 2 LPT1 STB# PR ND0 PR ND1 PR ND2 PR ND3 PR ND4 PR ND5 PR ND6 PR ND7 RACK# R B USY RPE RSLCT CN5 8P4C-180P 10 5 RN63 2.7K-10P8R 10 8.2K 1N4148S 74LCX86-SO14 U54C D54 8 H 1_VID2 RN60 2.7K-10P8R 14 9 2 1 3 5 7 PR ND1 AFD# PR ND0 STB# 7 5 3 1 8 6 4 2 CN7 8P4C-180P SLIN# PINIT# PR ND3 PR ND2 7 5 3 1 8 6 4 2 CN6 8P4C-180P 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 AFD# RERR# PINIT# PSLIN# 14 12 VID3 H 1_VID3 A VRM_OUTEN_L <37,38> U55B C 10 7 C 2 PR ND4 4 PR ND5 6 PR ND6 8 PR ND7 33R-8P4R RACK# R B USY RPE RSLCT 6 1N4148S 74LCX86-SO14 U54D 5 D55 11 A 74F00-SOIC14 R1088 C 13 7 2 B 4.7K Q121 LOW ENABLE MMBT3904 1K U55C 9 LPT Port U55D 8 12 11 RERR# C22 180P 2.7K 1 R1087 1N4148S 74LCX86-SO14 10 PSLIN# C 4 14 <33> 1 3 5 7 RN61 1N4148S R1086 C 14 PRD4 PRD5 PRD6 PRD7 C D4 A 74F00-SOIC14 13 7 VCC5 6 5 7 E H 1_VID1 D53 14 PRD[0..7] U54B 7 <33> 14 4 VID1 1 1N4148S PRD[0..7] CP16 74F00-SOIC14 7 0R X_COPPER <33> <33> <33> <33> <33> B RSLCT RERR# RACK# R BUSY RPE RSLCT RERR# RACK# R B USY RPE CPU0-B CPU1-B BACKPLATE BACKPLATE CP15 X_COPPER B VBAT1-1 U22-H MSI BIOS1-1 PCI_E4_2 Core Cell SERIAL PORT 1 C6 0.1u 0402 D2 1N4148S PLCC-32 Socket Battery +12VCOM <33> <33> <33> RTSA# DTRA# SOUTA NRIA# NCTSA# N DSRA# NSINA NDC DA# RTSA# DTRA# SOUTA 20 2 3 4 7 9 VCC RIN1 RIN2 RIN3 RIN4 RIN5 V+ ROUT1 ROUT2 ROUT3 ROUT4 ROUT5 16 15 13 11 DIN1 DIN2 DIN3 GND DOUT1 DOUT2 DOUT3 V- 1 19 18 17 14 12 RIA# CTSA# DSRA# SINA DC DA# NRTSA 5 NDTRA 6 NSOUTA 8 10 -12VCOM D3 <33> <33> <33> <33> <33> NDC DA# NSINA NSOUTA NDTRA 1 2 3 4 5 1N4148S COM1 6 7 8 9 N DSRA# NRTSA NCTSA# NRIA# MS-95D6-0A SLI card PCB PCB1 PCI_E4_1 U16-FAN1 COM Port -12V MSI 0.1u 0402 75232S-SSOP20 C12 A RIA# CTSA# DSRA# SINA DCDA# 11 VCC5 MS6-Heat Sink +12V 10 U3 NRTSA N DSRA# NCTSA# NRIA# 1 3 5 7 2 4 6 8 CN3 8P4C-180P NDC DA# NSOUTA NSINA NDTRA 1 3 5 7 2 4 6 8 CN2 8P4C-180P C835 0.1u 0402 MS-9620-0A PCB Micro Star Restricted Secret -12V Title C836 0.1u 0402 NB Heat Sink + FAN KB/MS/LPT/COM Port/FAN Document Number 4 3 2 R ev 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ 5 A X_MS-4044-0A SLI birdge card PCB Last Revision Date: Tuesday, February 15, 2005 Sheet of 32 44 1 4 2 LPC SUPER I/O W83627F/HF/THF FLOPPY CONNECTOR 1 U6 D SERIRQ LPC_DRQ#0 LPC_FRAME# LPC_AD0 LPC_AD1 LPC_AD2 LPC_AD3 <19> LPC_AD[3..0] R622 R623 R740 GPO13 GPO14 GPO15 X_4.7K X_4.7K X_4.7K <37,38> <28> <28> <28> <37,38> <37,38> 27 26 25 24 GPO13 GPO15 GPO10 GPO10 GPO17 GPO12 GPO14 GPO11 GPO16 GPO14 GPO11 GPO16 SIOVREF THERMDA_CPU1 THERMDA_CPU2 VTIN AGND AVI1 AVI2 AVI3 AVI4 AVI5 AVI6 AVI7 C <28> <28> <28> <28> <17> FANPWM1 FANIO1 FANPWM2 FANIO2 THRM# CHASSIS <17> SIO_PME# <39> DLED1 <17,22,23,24,25,27,36> SMBDATA <17,22,23,24,25,27,36> SMBCLK R2486 R2487 <39> GPX2/P15/GP14 GPY1/GP15 GPSA1/P12/GP10 GPSA2/GP17 GPX1/P14/GP12 GPY2/P16/GP14 GPSB1/P13/GP11 GPSB2/GP16 MSO/IRQIN0 MSI/GP20 101 102 103 104 93 94 95 96 97 98 99 100 VREF VTIN3 VTIN2 VTIN1 AGND -5VIN -12VIN +12VIN AVCC +3.3VIN VCOREB VCOREA 106 107 108 109 110 VID4 VID3 VID2 VID1 VID0 116 113 115 112 111 FANPWM1 FANIO1 FANPWM2 FANIO2 OVT# 105 118 76 19 OVT#(VID5) BEEP CASEOPEN# PME# 89 91 92 WDTO/GP24 SDA/GP22 SCL/GP21 67 68 64 90 72 73 18 PSOUT# PSIN SUSLED/GP35 PLED/GP23 PWRCTL#/GP31 SUSCIN/GP30 CLKIN 61 74 VSB VBAT 28 VCC3 X_0 X_0 DLED4 <17,36> SLP_S3# SIO_24M VCC5_SB VBAT B C28 0.1u 0402 VCC3 VCC5 VTIN_VCC C94 0.1u 0402 LAD0 LAD1 LAD2 LAD3 125 123 128 121 126 124 127 122 120 119 <17,39> PWRBTN# <17> LRESET# LCLK SERIRQ LDRQ# LFRAME# 12 48 77 114 For W83627HF only, in 83627F are NC <19> SIO_RST* <19> SIO_PCLK <19> SERIRQ <19> LPC_DRQ#0 <19> LPC_FRAME# 30 21 23 22 29 VCC_1 VCC_2 VCC_3 VCC_4 DRVDEN0 DRVDEN1(SMI#) INDEX# MOA# FANIO3/DSB# DSA# FANPWM3/MOB# DIR# STEP# WRDATA# WE# TRACK0# WP# RDDATA# HEAD# DSKCHG# 1 2 3 4 5 6 7 8 9 10 11 13 14 15 16 17 PD0 PD1 PD2 PD3 PD4 PD5 PD6 PD7 SLCT PE BUSY ACK# SLIN# INIT# ERR# AFD# STB# 42 41 40 39 38 37 36 35 31 32 33 34 43 44 45 46 47 IRRX/GP25 CIRRX/GP34 IRTX/GP26 SUSCLKIN(SLP_S5#) 88 69 87 75 DCDA# DSRA# SINA RTSA# SOUTA CTSA# DTRA# RIA# 56 50 53 51 54 49 52 57 DCDB# DSRB# SINB RTSB# SOUTB CTSB# DTRB# RIB# 84 79 82 80 83 78 81 85 GA20 KBRST KBDATA KBCLK MSDATA MSCLK KBLOCK#(BEEP) 59 60 63 62 66 65 58 RSMRST#/GP33 PWROK/GP32 70 71 VSS1 VSS2 VSS3 VSS4(AGND) Intel Front IR Header FDD1 83627THF SIO_RST* 1 DR VDEN0 INDEX# MOT_A# FANIO3 DRV_A# <28> FANPWM3 DIR# STEP# WT_DT# WT_EN# TRACK0# FDD_WP# RDATA# HEAD# D SKCHG# 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 <28> SYSTEM Thermal DR VDEN0 R1089 SIOVREF J IR1 10KST SMD DIR# STEP# WT_DT# WT_EN# TRACK0# FDD_WP# RDATA# HEAD# D SKCHG# X_0R RTSA# SOUTA DC DB# DSRB# 1 3 5 IRTX VTIN 1 3 5 4 6 4 6 IRRX D HDR 2*3(-2) R1090 THERMDA_CPU1 <5> 30KST C2707 X_102P VTIN_GND R1091 THERMDA_CPU2 <13> C2708 X_102P VTIN_GND HRD 2*17-Black VCC3 VCC3 BIOS PROTECT BLOCK RN91 C373 PRD[0..7] <32> <32> <32> <32> <32> <32> <32> <32> <32> RSLCT RPE R B USY RACK# RSLIN# RINIT# RERR# RAFD# RSTB# W_A20GATE R405 W_KBRST# R406 <32> 10K 10K A20GATE KBRST# R407 20K <17> <17> R408 20K Un_protected LOW Protected <39> SUSCLK SLP_S5# DCDA# DSRA# SINA RTSA# SOUTA CTSA# DTRA# RIA# R40 4.7K <17> <16,17,36> <32> <32> 83627THF <32> <32> <32> <32> <32> <32> VCC5 2 4 6 8 JBIOS1 1 3 5 7 LPC_RST PRES3 BIOS_WP# 10K-8P4R 1 2 X_HDR 1*2 <17> LPC_AD0 LPC_AD1 LPC_AD2 BIOS_WP# LPC_AD3 LPC_AD2 LPC_AD1 LPC_AD0 2 4 6 8 1 3 5 7 8.2K-8P4R Nvidia recommand pullup. VCC3 Default VCC3 C347 0.1u 0402 10U/1206 HIGH RN90 DLED3 C346 X_0.1u 0402 BIOS Update Config. IRRX IRTX R49 YT103S-1N DRV_A# 30KST PRD0 PRD1 PRD2 PRD3 PRD4 PRD5 PRD6 PRD7 RSLCT RPE R B USY RACK# RSLIN# RINIT# RERR# RAFD# RSTB# VCC5 RT3 INDEX# MOT_A# BIOS1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 VPP RST# FGPI3 FGPI2 FGPI1 FGPI0 WP# TBL# ID3 ID2 ID1 ID0 FWH0 FWH1 FWH2 GND VCC CLK FGPI4 IC(VIL) GNDA VCCA GND VCC INIT# FWH4 RFU RFU RFU RFU RFU FWH3 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 LPC_PCLK PRES4 pin 29 internal pulldown. <19> C pin 27 IC internal no connect. VCC3 R308 LPC_FRAME# 4.7K LPC_AD3 SST49LF004B 4MB 2 4 6 8 SOUTB CTSB# 1 3 5 7 VCC5 VBAT W_A20GATE W_KBRST# KBDAT KBCLK MSDAT MSCLK BEEP KBDATA KBCLK MSDATA MSCLK <32> <32> <32> <32> DLED2 <39> VCC3 VCC5 RN65 4.7K-8P4R C24 X_100p VCC5 SIO_RST* C86 X_0.1u 0402 C425 X_0.1u 0402 C217 X_0.1u 0402 R409 330 LPC_RST default is high BIOS_WP# VTIN_GND 4.7K R322 X_8.2K D15 S-BAT54A_SOT23 3 VCC3 VCC3 JLPC_RST B VCC3 VCC3 C68 C93 X_0.1u 0402 X_0.1u 0402 VTIN_GND R344 VCC5 Reservered GPI PRES4 20 55 86 117 2 Super I/O 3 1 5 Reservered GPI PRES3 <5,13> LPC_PCLK R323 8.2K R335 X_8.2K R333 8.2K R410 33R SIO_RST* LPC_AD0 LPC_AD1 LPC_AD2 LPC_AD3 LPC_FRAME# VCC3 WB-W83627HF-AW-VG R411 10K JLPC1 1 3 5 7 9 11 13 2 4 6 8 10 12 14 JLPC_RST VCC5 HDR 2*7 BOX-small LPC I/O STRAPPING RESISTOR 1 X_4.7K 10K RTSA# H: H: H: H: SPEAKER BLOCK 1 R50 4.7K Q5 NPN-MBT3904LT1-S-SOT23 1 2 1 2 1 AVI7 2 Micro Star Restricted Secret 2 R2482 28KR1% R41 2M CHASSIS 10K Title R2483 28KR1% NOTE: LOCATE CLOSE STATUS PANEL http://laptop-motherboard-schematic.blogspot.com/ 4 3 W627THF LPC I/O / FWH Document Number N31-1020011-C09 HDR 1*2 5 A R2480 1 C J CI1 B X_COPPER 1 BEEP CP2 X_FB 120ohm 0603 X_FB 120ohm 0603 R2477 28KR1% VCCP0 AVI4 2 2 1 10K <39> FB6 FB5 R2479 VCCP1 VBAT ALARM AVI5 2 10K Chasiss Intrusion VCC5 R2475 28KR1% R2476 VCC_DDR Enable KBC 48MHZ CFAD=4E PNP no Default 2 R58 L: Disable KBC L: 24MHZ L: CFAD=2E L: PNP Default R51 10K VCC5 C41 0.1u 0402 VTIN_GND 1 4.7K X_COPPER VTIN_VCC AVI6 2 SOUTB R48 E A CP3 R2472 VCC1_5 SOUTA 4.7K 2 VCC5 SOUTA SOUTB RTSA# DTRA# R56 1 VCC5 Thermal Resistor 2 R ev 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 33 44 5 4 3 2 1394a OHCI Link Layer Controller 1 +12V D5 A_BRS340-S-CASE403-03 A C F1 C PWR CPWR_0 FUSE 1.5A/24V C833 0.1u 0402 VCC3 C_BE#3 C_BE#2 C_BE#1 C_BE#0 107 122 4 15 CBE3# CBE2# CBE1# CBE0# PAR FRAME# IR D Y# TRDY# STOP# AD23 R372 100R DEVSEL# 1394REQ* 1394GNT* PERR# PCI_INTD* 3 123 124 126 128 108 127 96 95 2 91 PAR FRAME# IRDY# TRDY# STOP# IDSEL DEVSEL# REQ# GNT# PERR# INTA# PCICLK_1394 93 39 49 24 114 35 62 65 76 75 90 89 81 80 79 78 77 TPBIAS1 TPA1+ TPA1TPB1+ TPB1- XTPBIAS2 XTPA2P XTPA2M XTPB2P XTPB2M 88 87 86 85 84 TPBIAS2 TPA2+ TPA2TPB2+ TPB2- XCPS XREXT 92 PCIRST# 37 PME# R373 4.99K 1% 54.9R 54.9R 54.9R 54.9R TPA0+ TPA0TPB0+ TPB0- 1% 1% 1% 1% D J1 8 2 3 4 5 6 1 7 CPWR_0 C30 0.1u 0402 TPB0+ TPB0TPA0+ TPA0- SHLD PWR TPB+ TPBTPA+ TPAGND SHLD 1394 CON-Rear R358 11K 1% 63 R354 1K 1% 66 R359 6.34K 1% D6/CMCJMP PHYRESET CTL0/PC0JMP CTL1/PC1JMP D7/PC2JMP 54 55 53 LINKON/TSIJMP LREQ/TSOJMP D5 D4 D3 D2 D1 D0 MODE0 MODE1 SCLK LPS/CMC NC 57 56 51 48 47 46 45 44 43 42 40 38 67 CPWR_F +12V D13 A_BRS340-S-CASE403-03 A C C406 47P F6 CPWR_F C432 102P C378 0.1u 0402 CPWR_1 TPBIAS1 P3VA R327 C410 334P 2K 94 103 111 121 1 9 16 26 34 4.7K 60 XO 61 R374 4.99K 1% C R367 R366 R365 R364 54.9R 54.9R 54.9R 54.9R TPA1+ TPA1TPB1+ TPB1- 1% 1% 1% 1% J1394_1 TPA1+ TPB1+ CPWR_1 EECK EEDI 32 31 30 29 XI C433 103P EC54 100U/25V C834 0.1u 0402 R306 P3VA 1 3 5 7 9 TPA1- 2 4 6 8 10 TPB1CPWR_1 HDR 2*5(-9) Green 4.7K C381 10P F5 R338 PGND1 PGND2 R305 VCC3 XTPBIAS1 XTPA1P XTPA1M XTPB1P XTPB1M 52 58 41 50 B X_0R VSSC1 VSSC2 R300 115 36 PME# RAMVSS <19> 1394_RST* <19,22,27> PME# TPBIAS0 TPA0+ TPA0TPB0+ TPB0- PCICLK 25 <19> PCICLK_1394 74 73 72 71 70 SCL/EECK SDA/EEDI EEDO EECS GNDATX0 GNDARX0 GNDARX1 GNDATX1 GNDARX2 GNDATX2 <19,22,27> DEVSEL# <19,22> 1394REQ* <19> 1394GNT* <19,22,27> PERR# <19,22> PCI_INTD* 59 64 68 69 82 83 <19,22,27> PAR <19,22,27> FRAME# <19,22,27> IR D Y# <19,22,27> TRDY# <19,22,27> STOP# XTPBIAS0 XTPA0P XTPA0M XTPB0P XTPB0M C409 334P FUSE 1.5A/24V VSS1 VSS2 VSS3 VSS4 VSS5 VSS6 VSS7 VSS8 VSS9 C_BE#[3..0] R363 R362 R361 R360 U21 VDDATX0 VDDARX0 VDDATX1 VDDARX1 VDDATX2 VDDARX2 AD31 AD30 AD29 AD28 AD27 AD26 AD25 AD24 AD23 AD22 AD21 AD20 AD19 AD18 AD17 AD16 AD15 AD14 AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 PVDD1 PVDD2 97 98 99 100 101 104 105 106 109 110 112 116 117 118 119 120 5 6 7 10 11 12 13 14 17 18 19 21 22 23 27 28 EC7 100U/25V TPBIAS0 RAMVDD AD31 AD30 AD29 AD28 AD27 AD26 AD25 AD24 AD23 AD22 AD21 AD20 AD19 AD18 AD17 AD16 AD15 AD14 AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 C <19,22,27> C_BE#[3..0] VDD1 VDD2 VDD3 VDD4 VDD5 VDD6 AD[31..0] <19,22,27> AD[31..0] VDDC1 VDDC2 102 113 125 8 20 33 D C29 103P C25 102P P3VA CPWR_F Y6 24MHz DIP CPWR_2 FUSE 1.5A/24V 1M C387 10P C415 103P B VT6306 3*Port TPBIAS2 C411 334P R375 4.99K 1% R371 R370 R369 R368 54.9R 54.9R 54.9R 54.9R 1% 1% 1% 1% TPA2+ TPA2TPB2+ TPB2- J1394_2 TPA2+ 1 3 5 7 9 TPB2+ CPWR_2 TPA2- 2 4 6 8 10 TPB2CPWR_2 HDR 2*5(-9) Green VCC3 VCC3 VCC3 For Intel 1394 pinheader C380 0.1u 0402 VCC3 A C342 0.1u 0402 C369 0.1u 0402 C344 0.1u 0402 P3VA L10 C343 C345 0.1u 0402 X_0.1u 0402 C341 0.1u 0402 R302 4.7K R301 4.7K A VCC3 P3VA U19 X_L02-8008044-J07 EECK EEDI CP12 X_COPPER C360 0.1u 0402 C372 0.1u 0402 C390 0.1u 0402 C405 0.1u 0402 C340 0.1u 0402 6 5 C407 0.1u 0402 7 R307 X_510 http://laptop-motherboard-schematic.blogspot.com/ 5 4 3 2 SCLK VCC SDA A0 A1 A2 WP GND 8 1 2 3 4 X_ATMEL AT24C02 Micro Star Restricted Secret Title 1394a Link Layer Controller Document Number R ev 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 34 44 5 4 3 2 1 ATA 33/66/100 Connector PRIMARY IDE BLOCK SECONDARY IDE BLOCK PDD[0..15] <20> IDE2 HDR 2*20 BOX 2 SDD8 4 SDD9 6 SDD10 8 SDD11 10 SDD12 12 SDD13 14 SDD14 16 SDD15 18 D <36> HD_RST# R155 PDD7 PDD6 PDD5 PDD4 PDD3 PDD2 PDD1 PDD0 HD_RST# 33 <20> PD_DREQ <20> PD_IOW# <20> PD_IOR# <20> P D_IORDY <20> PD_DACK# <20> IRQ14 <20> PD_A1 <20> PD_A0 <20> PD_CS#1 <39> PD_LED R118 5.6K VCC3 R77 4.7K HDRST#P 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 R89 10K IDE1 HDR 2*20 BOX 2 PDD8 4 PDD9 6 PDD10 8 PDD11 10 PDD12 12 PDD13 14 PDD14 16 PDD15 18 HD_RST# R154 SDD7 SDD6 SDD5 SDD4 SDD3 SDD2 SDD1 SDD0 22 24 26 28 30 32 34 36 38 40 PD_DET PD_A2 PD_CS#3 C109 X_4700p_X7R R111 4.7K HDRST#S 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 33 <20> SD_DREQ <20> SD_IOW# <20> SD_IOR# <20> S D_IORDY <20> SD_DACK# <20> IRQ15 <20> SD_A1 <20> SD_A0 <20> SD_CS#1 <39> SD_LED <20> <20> <20> R119 5.6K R87 15K R90 4.7K R93 10K D SDD[0..15] 22 24 26 28 30 32 34 36 38 40 SD_DET SD_A2 SD_CS#3 C115 X_4700p_X7R R97 4.7K <20> <20> <20> <20> R88 15K VCC3 VCC3 VCC3 VCC5 VCC5 R635 X_8.2K C C PDD7 R156 SDD7 R636 X_8.2K 10K R153 10K IR Q14 IR Q15 J I1 J I2 DIFF100_TOP+ DIFF100_TOPX_HDR 1*2 X_HDR 1*2 X_HDR 1*2 J I3 X_HDR 1*2 J I4 DIFF100_INT+ D IFF100_INT- B B FM8 FM7 FM6 FM5 FM4 FM3 X X X X X X X_FM X_FM X_FM X_FM X_FM X_FM X X X X 7 8 7 8 6 2 5 2 5 2 5 MH1 MH2 MH3 X_HDR 1*2 J I5 J I6 60OHM_TOP 60OHM_INT X_HDR 1*2 4 FM1 9 3 FM22 6 4 FM17 9 3 FM20 6 4 Mounting Holes X_HDR 1*2 9 3 Optics Orientation Holes 7 8 Simulation J I7 60OHM_BOT X_FM X_FM X_FM 6 9 6 2 5 2 5 MH4 MH6 MH9 MH8 MH7 Micro Star Restricted Secret Title 4 9 5 3 6 2 4 9 5 3 6 2 4 9 5 3 6 2 4 9 5 MH5 3 2 R ev 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw X_FM 4 ATA 33/66/100 Connector Document Number http://laptop-motherboard-schematic.blogspot.com/ 5 A 7 8 7 8 7 8 7 8 7 8 6 2 3 X 9 4 X X_FM FM2 3 X X_FM FM21 4 X X_FM FM19 3 X_FM FM18 7 8 A 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 35 44 5 4 3 2 ACPI Controller CHOK6 C603 X_C10000P16X HT_PWRGD SMBCLK SMBDATA RSMRST# SLP_S5# SLP_S3# R352 1K D S EC61 CD1000U6.3EL15 G C606 C2.2U10X0805 Q60 N-P50N03LD EC62 CD1000U6.3EL15 EC63 CD1000U6.3EL15 C2.2U10X0805 CLOSE TO CHIP <16> <17,22,23,24,25,27,33> <17,22,23,24,25,27,33> <17> <16,17,33> <17,33> R607 10R/0805 1.5x * 12mohm * 8A / 72uA = 2 <= 2Kohm VCC5 VCC5 C SLP_S3# VCC1_5 CH-4.2U10A C605 MS-6+ SOP14 4.7K E C Q38 2N3904S B R353 10K 1% D C604 0.1u 0402 R606 200R Q59 N-P50N03LD CHOK7 G R604 + PLED2 R350 330 BOOT H_DRV PGND ISEN L_DRV VDD VDDA + <39> R351 X_330 ISET VREF_IN FB COMP SS GND PWROK CD1000U10EL15 + PLED1 C608 C2200P16X C602 C0.22U16X 8 9 10 11 12 13 14 D 3VDUAL 3VDUAL R348 330 EC60 S X_5.1K 1% R345 330 + C669 C4.7U10Y0805 CH-3.3U4A D39 S-1N5817_DO214AC U29 7 6 5 4 3 2 1 R602 D X_0R C600 X_C0.22U16Y R601 X_33R 1% VREF_IN R603 51K 1% R599 +12V R600 49.9K 1% VCC5_SB EC59 + CD1000U10EL15 VCC5 C599 X_0.1u 0402 R598 5.1K 1% <39> 1 VCC5_SB R346 1K C34 X_2200p Q7 48 47 46 45 44 43 42 41 40 39 38 37 VCC3 VCC3 VDDA_25 C371 105p/0805 VCC3 R332 10K Q62 20N03 G 2 + C358 105P 5V_DRV + 1 EC38 470u/10V VCC5 VCC3 LED1 LED-G#_D5 EC2030 1000u 5 3 6 2 7 1 VREF1_25 R734 1K C101 X_103P VCC_DDR VCC_DDR + 6 - 3VDIMM VCC_DDR 2 D EC56 1000u 3 S D 2 S +12V 4 3 Micro Star Restricted Secret 3VDUAL VCC_DDRVCC3 Title C133 475P/0805 EC45 100u 2 EC40 1000u EC31 1000u + Q84 N-P45N02LD_TO252 IPF06N03LA/50A/5.4m/TO252 VCC2_5 3 1 5V_DRV G R737 75 1% A + EC4 1000u EC8 1000u Q2010 VCC_DDR VCC3 http://laptop-motherboard-schematic.blogspot.com/ 5 R738 1K 1% + EC9 1000u EC15 1000u 4 D S EC2028 EC2029 X_470u/10V X_470u/10V IPF06N03LA/50A/5.4m/TO252 + EC3 470u 1.24K 1% N-APM2054N_SOT89 + R735 + R3 300R 1% 1.25V/2.9A VTT_DDR + W83310DS G D S 3.3VDIMM C464 X_103P + VIN GND VREF1 VOUT C726 X_103P VCC_DDR 75 1% R2 300R 1% 4 X_470u/10V Q66 G D S + FDD8896_TO252 1 2 3 4 + NC VREF2 ENABLE VCNTL BOOT_SEL 1 7 + U1 9 8 7 6 5 Q83 N-APM2054N_SOT89 G U26B LM358MX_SOIC8 Q122 5 R736 + Q2012 EC42 100u 9VSB 8 + + G 200 1% 3.3VDIMM 3VDUAL EC2027 VCC_DDR 1_5VDUAL - VCC5_SB NN-P07D03LV_SO8 FDD8896_TO252 EC1 1000u Q82 N-APM2054N_SOT89 4 EC2031 470u/10v 4 3VDIMM VCC_DDR 3VDUAL 1 R733 1K 1% VCC3 3VDUAL A 1 B C225 X_102P C463 105P EC2 470u/10V Q64 + R732 Q21 + DDR VTT Power U26A LM358MX_SOIC8 VDD_12_A 3VDUAL TO252R-H 2 3 8 D S 1K C727 X_103P EC16 1000u 2.2R/0805 EC44 X_100u R731 + R309 VREF1_25 EC27 X_470u C462 X_105P R889 100 VTT_DDR 9VSB 33 VCC3 VCC5_SB S 3VDUAL R616 C359 0.47u VCC_DDR VCC5 + H66 C Low RDS ON MOSFET MS-6 Rev:RBF PS_ON# Q63 2N7002S 4.7K G EC51 1000u/6.3V VREF_IN + R321 VCC5 C382 105p/0805 + SLP_S3# C383 0.1u 0402 36 35 34 33 32 31 30 29 28 27 26 25 R330 10K <39> 8 + NN-P07D03LV_SO8 R318 4.7K B 1 5VDUAL C311 C63 X_0.1u 0402 X_0.1u 0402 Q61 20N03 G C60 X_102P 9VSB C1 C2 CHRPMP AGND1 5VUSB_DRV 5V_DRV VAGP_DRV VAGP_SEN WD_DET 1.2VLDT_DRV 1.2VLDT_SEN TMP_FAULT# 13 14 15 16 17 18 19 20 21 22 23 24 C374 C370 0.1u 0402 0.1u 0402 VCC5_SB 7 2 VRM_GD <16,37,38> VRM_GD <37,38> PWM_EN VREF1_25 VCC5 FP_RST# PCIRST# HDD_RST# DEV_RST# VDD_GD VDD_EN 1.25VREF VCC5 SLOT_RST# VCC3 2.5VDDA AGND0 6 2 5VDUAL 3 1 2 3 4 5 6 7 8 9 10 11 12 MS6_RST* HD_RST# 3 5VDUAL 8 R343 4.7K + R723 330 D R336 330 C 5V_DRV 5 S U22 PLED1/EXTRAM PLED0/3VDLDEC# CPU_PWGD CHIP_PWGD I2C_CLK I2C_DATA RSMRST# S5# S3# PWR_OK 5VSB GND VCC5 PSIN# PSOUT# MEMBT SS 5VSB DDRTYPE VDIMM_LSEN VDIMM_LDRV VDIMM_HSEN VDIMM_HDRV 3VSB_SEN 3VSB_DRV VCC5 4 D C393 105P <19> <35> 5V DUAL Power VCC5_SB PWM Mode = High 4 E ATX_PWR_OK <17,39> 4.7K 4 R349 B Q37 2N3904S EC43 1000u MS-6 ACPI Controller Document Number R ev 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 1 Last Revision Date: W ednesday, February 16, 2005 Sheet of 36 44 5 4 3 Voltage Regular Module 2 VCC5 ATX12V Power Connector +12V C124 X_0.1u 0402 JPW R3 VCCP_IN 3 1.1uH-25A 12V GND 1 12V GND 2 + EC84 330u16VFP C18 2.2U/1206/50V JPW R2 1 2 3 4 H86 GND GND GND GND VCC5 VCC5 POW ERCONN2X4 R691 4.7R/0805 24 10k/0805 C656 105p/0805 Q89 R2509 1 2 3 4 C658 104p/0805/X7R C659 X_102P COREFB0_L R7 51R C660 X_102P 11 VCC5 R677 X_150K 6 UGATE2 PHASE2 ISEN2 OFST LGATE2 25 R676 1.8K 1K PVCC3 BOOT3 13 14 B 18 21 R681 OCSET ICOMP ISUM 16 IREF 41 C665 103P 2.2R C663 10k/0805 105p/0805 C667 820u2.5VOS EC110 + 820u2.5VOS EC105 + 820u2.5VOS EC108 + C661 102P V IN BSC032N03S 1 2 3 4 UGATE3 20 PHASE3 22 ISEN3 19 LGATE3 17 C943 105p/0805 Q94 1 2 3 4 R683 1R/0805 CHOK10 0.6uH 40A BSC059N03S R684 1.8K Q95 10k/0805 R686 0R/0805 BSC059N03S 1 2 3 4 R2512 820u2.5VOS EC106 Q96 R685 2.2R 1% 1 2 3 4 BOTTOM PAD CONNECT TO GND THROUGH 10vias + 820u2.5VOS EC107 B + VCORE_P0 C666 102P BSC032N03S R687 + R678 2.2R 1% Q93 R2511 C664 104p/0805/X7R VRM10 15 BSC032N03S 5 REF GND E R682 820u2.5VOS EC109 Q92 1 2 3 4 R143 4.7R/0805 C662 103P 4 MMBT3904 FS 5 5 R27 120K 1 2 3 4 R2510 VCCP_IN Q123 B BSC059N03S Q91 10k/0805 R679 0R/0805 23 Remove:2 PHASE 36 1 CHOK9 0.6uH 40A BSC059N03S 28 RGND R680 51K 1% +10mV OFFSET R674 1R/0805 27 VSEN 1 12 2 OVL1 100 5 R675 1 R4 51R C942 105p/0805 Q90 1 2 3 4 2 2.2R 1 26 R673 2 PVCC2 1 VDIFF BOOT2 COREFB0_H 1 R692 4.7R/0805 2 10 C V IN BSC032N03S 1 1K VCCP1 0.8V~1.55V/80A + C654 102P BSC032N03S FB 820u2.5VOS 820u2.5VOS + EC103 EC104 R670 2.2R 1% 1 2 3 4 5 R672 C 1 2 3 4 Q88 2 R2508 R671 0R/0805 34 COMP VCCP_IN 9 <32,38> VRM_OUTEN_L Q87 470p C VCCP1 LGATE1 10k/0805 5 C655 8 R669 1.8K BSC059N03S 1 C5 562P CHOK8 0.6uH 40A BSC059N03S 29 2 10K C20 103P R668 1R/0805 31 32 C941 105p/0805 Q86 1 2 3 4 5 R17 ISEN1 1 2 3 4 C8 105p/0805 2 7 C653 0.1u 0402 Q85 2.2R 2 C652 0.1u 0402 R2507 R667 C651 104p/0805/X7R UGATE1 PHASE1 VIN 33 30 5 0R PVCC1 BOOT1 5 V IN R666 4.7R/0805 10k/0805 5 R25 <16,36,38> VRM_GD <36,38> PWM_EN VID4 VID3 VID2 VID1 VID0 DACSEL/VID5 PGOOD ENLL VCC 38 39 40 1 2 3 35 37 H1_VID4 H1_VID3 H1_VID2 H1_VID1 H1_VID0 TO252R-H VCCP_IN C601 C4.7U10Y0805 U32 ISL6566CR C10 X_103P 5 D1 X_1N5817 R22 1K VCCP_IN 5 R665 1K D 8 7 6 5 +12V +12V +12V +12V 5 VCC5 <5> C4 X_0.1u 0402 Power Con 2*2 X_10u/16v/1206 <5> C15 X_0.1u 0402 2 + EC6 330u16VFP 2 + EC12 330u16VFP 2 + EC18 330u16VFP 2 2 + EC23 330u16VFP D C19 X_0.1u 0402 C96 X_0.1u 0402 1 VCC5 1 1 1 1 4 C11 <13,32> <13,32> <13,32> <13,32> <13,32> VCC5 VIN 1 CHOK1 VCC5 BSC032N03S 16.5K 1% 473p/X7R R688 R689 R690 20K 1% 20K 1% 20K 1% OVL1 VCC5 R9 3K 1% VCC5 R24 1K 4.7K Q35 2N3904S GPO16 R291 X_4.7K Q34 X_2N3904S VSET2 http://laptop-motherboard-schematic.blogspot.com/ 4 3 Q1 X_2N7002 G VSET1 <33,38> 5 D R292 R21 X_1K 2 S GPO11 A Q2 2N7002 S C Q32 2N3904S E <33,38> Q54 X_2N3904S B 4.7K G E R431 X_1K R293 VSET0 Q53 X_2N3904S B VCCP1 GPO10 C <33,38> S R429 X_1K A VCC5 Q3 2N7002 G VRM_GD R6 X_16K D VCC5 R8 2K 1% D R26 1K Micro Star Restricted Secret Title R ev K8 VRM ISL6559CB Document Number MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 1 0A Last Revision Date: Tuesday, February 15, 2005 Sheet 37 44 of 5 4 3 Voltage Regular Module 2 VCC5 VCC5 VCC5 1 VCC5 ATX12V Power Connector C944 0.1u 0402 C945 0.1u 0402 C946 0.1u 0402 C947 0.1u 0402 H99 D D V IN TO252R-H VCC5 VCC5 VCC5 C952 103P R932 4.7R/0805 VCCP_IN CHOK12 0.6uH 40A 1 2 3 4 R941 0R/0805 VCCP_IN R2515 1 2 3 4 C964 104p/0805/X7R C965 X_102P R949 51R C966 X_102P 11 VCC5 R951 X_150K 6 UGATE2 PHASE2 10k/0805 ISEN2 OFST LGATE2 25 R950 1.8K R2516 1 2 3 4 VCCP_IN Remove:2 PHASE 36 C 5 Q124 R956 120K FS REF PVCC3 C969 103P BOOT3 E 4 MMBT3904 R958 1K 13 14 B 18 R2517 2.2R C971 104p/0805/X7R VRM10 OCSET ICOMP UGATE3 20 PHASE3 22 ISEN3 19 IREF 41 GND ISUM 16 C972 103P LGATE3 17 C974 820u2.5VOS EC92 + 820u2.5VOS EC95 + C968 105p/0805 Q107 CHOK14 0.6uH 40A BSC059N03S R960 1.8K R2518 BSC059N03S Q108 1 2 3 4 R962 0R/0805 820u2.5VOS EC93 Q109 R961 2.2R 1% 1 2 3 4 BOTTOM PAD CONNECT TO GND THROUGH 10vias + 820u2.5VOS EC94 B + VCORE_P0 C973 102P BSC032N03S R963 + 1 2 3 4 R959 1R/0805 10k/0805 15 820u2.5VOS EC91 C967 102P V IN BSC032N03S 1 2 3 4 + R952 2.2R 1% Q106 C970 105p/0805 820u2.5VOS EC90 Q105 1 2 3 4 BSC032N03S R955 4.7R/0805 10k/0805 21 R957 BSC059N03S Q104 R953 0R/0805 23 1 CHOK13 0.6uH 40A BSC059N03S 28 RGND R954 51K 1% +10mV OFFSET R947 1R/0805 27 VSEN 1 12 C962 105p/0805 Q103 1 2 3 4 2 OVL0 100 5 R948 5 R946 51R <32,37> VRM_OUTEN_L Q102 C963 105p/0805 1 2.2R 2 24 26 R945 1 PVCC2 C 2 VDIFF R943 4.7R/0805 10k/0805 1 10 BOOT2 <13> COREFB1_L 1 C960 102P 5 1K VCCP0 0.8V~1.55V/80A + V IN BSC032N03S 5 R944 <13> COREFB1_H 1 2 3 4 BSC032N03S FB 820u2.5VOS 820u2.5VOS + EC88 EC89 R940 2.2R 1% 1 34 COMP Q101 470p 9 B Q100 2 R2514 2 LGATE1 R939 1.8K BSC059N03S 2 BSC059N03S 1 8 C VCCP0 R937 1R/0805 29 2 C959 562P C954 105p/0805 Q99 1 2 3 4 5 C961 1 2 3 4 C955 105p/0805 31 32 Q98 2.2R 10k/0805 ISEN1 5 7 C958 0.1u 0402 R942 10K R2513 R936 C956 104p/0805/X7R UGATE1 PHASE1 C957 0.1u 0402 33 30 2 0R PVCC1 BOOT1 5 R938 <16,36,37> VRM_GD <36,37> PWM_EN VID4 VID3 VID2 VID1 VID0 DACSEL/VID5 PGOOD ENLL 5 38 39 40 1 2 3 35 37 VID4 VID3 VID2 VID1 VID0 VCC <5> <5,32> <5,32> <5,32> <5,32> R935 4.7R/0805 10k/0805 5 V IN C953 C4.7U10Y0805 U57 ISL6566CR 5 D51 X_1N5817 R934 1K 5 R933 1K 5 C951 0.1u 0402 BSC032N03S 16.5K 1% R964 R965 R966 473p/X7R 20K 1% 20K 1% 20K 1% OVL0 VCC5 R967 3K 1% VCC5 R973 1K 4.7K Q114 2N3904S GPO16 R977 X_4.7K Q117 X_2N3904S VSET2 http://laptop-motherboard-schematic.blogspot.com/ 4 3 Q116 X_2N7002 G VSET1 <33,37> 5 D R975 R974 X_1K 2 S GPO11 A Q113 2N7002 S C Q111 2N3904S E <33,37> Q115 X_2N3904S B 4.7K G E R976 X_1K R972 VSET0 Q112 X_2N3904S B VCCP0 GPO10 C <33,37> S R971 X_1K A VCC5 Q110 2N7002 G VRM_GD R969 X_16K D VCC5 R968 2K 1% D R970 1K Micro Star Restricted Secret Title R ev K8 VRM ISL6559CB Document Number MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw 0A Last Revision Date: Tuesday, February 15, 2005 Sheet 38 44 of 1 5 4 3 2 1 ATX connector / Front Panel ESD Protect C424 X_181P D9 1N4148S SATA_LED <20> D10 1N4148S PD_LED <35> D12 1N4148S SD_LED <35> VCC5 D D 8 6 4 2 VCC5 RN97 330R-8P4R 2 4 6 8 For MSI / Intel Front Panel RN96 330R-8P4R 3VDUAL 7 5 3 1 VCC5 VCC3 R401 <17> HD D+ 330 10K R637 FP_RST# 33 1 HDD+ PLED 2 PLED1 3 HDD- SLED 4 PLED2 5 RESET- PWSW+ 6 7 RESET+ PWSW- 8 9 NC PLED1 <36> PLED2 <36> 1 3 5 7 JFP1 R387 R608 22K JDB1 R609 33 PWRBTN# <17,33> C423 105p <33> <33> <33> <33> DLED1 DLED2 DLED3 DLED4 DLED1 DLED2 DLED3 DLED4 1 3 5 7 2 4 6 8 10 D DLED1 D DLED2 D DLED3 D DLED4 HDR 2*5(-9) C422 105p 2 4 6 8 HDR 2*5(-10) JFP2 1 GND SPEAKER 2 PLED2 3 SLED BUZ+ 4 PLED1 5 PLED BUZ- 6 VCCSPK 8 Q40 2N3904S 1 3 5 7 C RN95 330R-8P4R R381 Q41 2N3904S Q42 2N3904S C X_0R Q39 2N3904S VCC5 HDR 2*4(-7) RN98 <33> 1 3 5 7 ALARM JGS1 2 4 6 8 <17> EXTSMI# EXTSMI# 1 2 X_HDR 1*2 D11 X_1N4148S 150R-8P4R C421 0.1u 0402 R383 <17> Q43 2N3904S SPKR 2.2K VCC5 B B ATX Connector JPWR1 VCC3 -12V C162 102P C158 0.1u 0402 R146 10K <36> C161 102P PS_ON# 13 14 15 16 17 18 19 20 21 22 23 24 3.3V -12V GND4 PS_ON GND5 GND6 GND7 3VSBY 5V 5V 5V GND8 3.3V 3.3V GND1 5V GND2 +5V GND3 PWROK 5VSBY 12V 12V 3.3V 1 2 3 4 5 6 7 8 9 10 11 12 VCC3 C159 0.1u 0402 VCC5_SB R2425 X_0R R460 10K VCC3 +12V PS_ON#A VCC5 C106 0.1u 0402 C107 0.1u 0402 POWERCONN2X12 <5> VCC3 VCC5 ATXPWOK R75 10K ATXPWOK E C105 0.1u 0402 VCC5 C110 0.1u 0402 A C404 0.1u 0402 C Q55 2N3904S C2678 0.1u 0402 ATX_PWR_OK <17,36> B VCC5_SB + A EC2026 1000u/16V R461 10K Micro Star Restricted Secret Title VCC3 ATX connector / Front Panel Document Number 5 4 3 2 0A MS-9620 MICRO-STAR INT'L CO.,LTD. No. 69, Li-De St, Jung-He City, Taipei Hsien, Taiwan http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ R ev 1 Last Revision Date: Tuesday, February 15, 2005 Sheet of 39 44 5 4 3 2 1 MS-9620 CLOCK BLOCK DIAGRAM D D DDR MEM 0 P/N 2 DDR DIMM # 6 DDR DIMM # 5 2 DDR MEM 3 P/N CPUCLK BUFFER DDR DIMM # 4 CPU0 CPUCLK/200MHZ DDR DIMM # 3 CPUCLK 200MHZ DDR MEM 2 P/N DDR DIMM # 2 2 CPUCLK 0 200MHZ DDR DIMM # 1 RTC_CRYSTAL DDR MEM 1 P/N 32.768MHZ Crystal 2 DDR MEM 4 P/N 2 DDR MEM 5 P/N 2 LPC_CLK C C FWH CPUCLK 1 200MHZ S MA CONNECTOR CK8-04 EXP_SLOT1_100MHZ_CLK_P/N PCI EXPRESS X8 SLOT # 1 PE1_CLK EXP_SLOT1_100MHZ_CLK_P/N PCI EXPRESS X8 SLOT # 1 PE2_CLK EXP_SLOT1_100MHZ_CLK_P/N PCI EXPRESS X4 SLOT # 1 25MHZ Crystal PE0_CLK CPU1 PCI_SLOT1_33MHZ_CLK_P/N PCICLK_SLOT1 PCI SLOT B B SIO_CLK RGMII_CLK 88E1111 PHY GbE LAN SIO_24M SIO 25MHZ Crystal PCI_SLOT1_33MHZ_CLK_P/N PCICLK_5705 BROADCOM 5705 GbE LAN RGMIITCLK_125MHZ RGMII RGMIIRCLK_125MHZ PCICLK_1394 PCI_SLOT1_33MHZ_CLK_P/N 25MHZ Crystal AC97_CLK A A AC97CLK_24.576MHZ BITCLK_12.288MHZ Micro-Star Int'l Co., Ltd. VIA6306_1394 No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw AC97 Title http://laptop-motherboard-schematic.blogspot.com/ 24MHZ System Clock Block Diagram Size Document Number Custom MS-9620 Crystal Date: 5 4 3 2 Tuesday, January 25, 2005 R ev 0A Sheet 1 40 of 44 5 4 3 2 1 MS-9620 SYSTEM RESET & POWER ON SEQUENCINGBLOCK DIAGRAM D D CPU0 DIMM_RST CPU1 CPU_RST C C FP_RST RSTBT SIO_RST SIO 1394_RST PCI_RST 5705_RST MS6_RST FWH B B BROADCOM 5705 VIA1394 PCI1 MS6 IDE_RST A A IDE1 Micro-Star Int'l Co., Ltd. IDE2 No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw http://laptop-motherboard-schematic.blogspot.com/ Title ABR Block Diagram Size Document Number Custom MS-9620 Date: 5 4 3 2 Tuesday, January 25, 2005 Rev 0A Sheet 1 41 of 44 5 4 3 2 1 D D MS-9162 SMBus Block Diagram 3VDUAL 3.3V DIMM 1 DIMM 2 R R ICH7 SMBUS * Slave Address = 0XA0 SMBUS_MEM DIMM 3 * Slave Address = 0XA2 BCM 5705 GbE DIMM 5 C * Slave Address = 0XA1 DIMM 4 * Slave Address = 0XA3 DIMM 6 C PCI 32 / 33 Slot * Slave Address = 0XA4 * Slave Address = 0XA5 ( SLOT # 1 ) PCI-Express X8 Slot PCI-Express X8 Slot PCI-Express X4 Slot B B A A Micro-Star Int'l Co., Ltd. No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw Title http://laptop-motherboard-schematic.blogspot.com/ System SMBus Block Diagram Size Document Number Custom MS-9620 Date: 5 4 3 2 Tuesday, January 25, 2005 R ev 0A Sheet 1 42 of 44 5 4 3 2 1 MS-9620 DDR Routing Block Diagram D D CS_0/1 CS_2/3 CS_4/5 C C CKEH/L H0_MEMCLK_H0/L0 H0_MEMCLK_H1/L1 H0_MEMCLK_H2/L2 B B H0_MEMCLK_H3/L3 H0_MEMCLK_H4/L4 H0_MEMCLK_H5/L5 DIMM1 DIMM2 DIMM3 DIMM4 DIMM5 DIMM6 A A Micro-Star Int'l Co., Ltd. No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw Title http://laptop-motherboard-schematic.blogspot.com/ DDRII Routing Block Diagram Size Document Number Custom MS-9620 Date: 5 4 3 2 Tuesday, January 25, 2005 R ev 0A Sheet 1 43 of 44 5 4 3 2 1 General SPEC CK_804 Vcore Adjust GPIO Pin D VSET2 VSET1 1 0 VSET0 Voltage 1.65V 0 1 0 1 1.6V 1 1 0 1.55V 1 1 1 1.5V GPIO Pin Type GPO10 O Function VSET0 GPO11 O VSET1 GPO16 O VSET1 Function I MEM_GPIO1 GPI 2 I MEM_GPIO2 GPI 3 I BIOS_WP# GPI 4 I LAN_RST# GPI 7 I GPO_SLI D PCI Config. SIO WB 83627 C Type GPI 1 IDSEL CLOCK REQ&GNT INTC# AD22 PCICLK1 0 INTD# AD23 PCICLK0 1 AD24 PCICLK3 DEVICE ICH INT Pin 5705 GIGALAN C VIA6306 1394 PCI1 INT A#B#C#D MSI BLUETOOTH PCICLK2 AD25 2 3 B B A A Title GENERAL SPEC Size B * GPIO18 will toggle at 1Hz frequency. Date: 5 4 3 http://laptop-motherboard-schematic.blogspot.com/ 2 Document Number MS-9620 Friday, January 28, 2005 Rev 0A Sheet 1 44 of 44