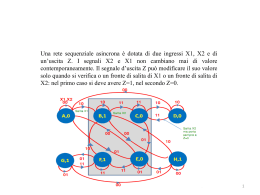

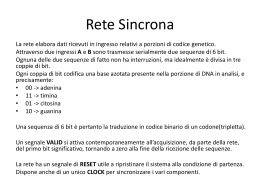

Tris Il progetto si propone di simulare il gioco del Tris: a turno i giocatori scrivono il proprio simbolo (per comodità useremo ‘0’ e ‘1’) all’interno di una delle caselle di una griglia 3x3. Ottiene la vittoria il primo giocatore che riesce a disporre tre dei suoi simboli in una linea retta verticale, orizzontale o diagonale. N.B. In questa simulazione è possibile per i giocatori sovrascrivere una casella contenente un altro simbolo. Se un giocatore cerca di scrivere al di fuori della griglia fornendo coordinate sbagliate perderà il proprio turno (le coordinate per riga e colonna sono comprese tra “00” e “10”). Ciascuna casella del gioco viene simulata da un Flip-Flop D che possiede due uscite significative : -Q0 : indica il segno inserito nella casella -Q1 : bit di controllo, il valore è ‘1’ se la casella è stata scritta dopo l’ultimo RESET Le 8 linee evidenziate nel disegno rappresentano le 8 possibili combinazioni vincenti del gioco del Tris Ciascuna combinazione vittoriosa viene analizzata da un blocco di controlli logici identico a quello evidenziato in figura: un NOR3 ed un AND3 sulle uscite Q0 dei FFD, posti a loro volta in OR, per controllare l’uguaglianza dei segni, e un AND3 sulle uscite Q1 per controllare la validità dei segni (ovvero che le “caselle” siano state scritte). L’OR di queste 8 combinazioni segnala quindi il termine del gioco (il segnale in output è in logica negativa!). SIMULAZIONE BEHAVIORAL Come è possibile osservare nelle due parti di simulazione evidenziate, il segnale Victory (in logica negativa) passa a ‘0’ non appena si presenta una combinazione vincente, e finché il segnale di RESET non viene posto a ‘1’ qualsiasi ingresso successivo alla vittoria viene ignorato dal sistema. Quando si presenta una “vittoria” il segnale Winner indica quale tra i due giocatori abbia vinto! SIMULAZIONE POST-ROUTE La simulazione Post-Route si presenta sostanzialmente identica a quella Behavioral, con l’unica differenza che il segnale Winner presenta un ritardo di circa 7 ns dal fronte positivo di Input_enable, mentre il segnale Victory un ritardo di 9 ns.

Scaricare