Reti Sincrone 1 I problemi con le reti asincrone • Il comportamento dipende dai ritardi sugli anelli di retroazione con possibilità di malfunzionamenti (disallineamento dei ritardi sugli anelli di retroazione) • Il comportamento dipende dalle alee degli ingressi (che comunque NON possono essere temporalmente allineati in assoluto) e impedisce il riconoscimento di sequenze ripetute degli ingressi (ad esempio riconoscere la sequenza 00-00-11-01 che risulta essere indistinguibile da 00-11-01) SOLUZIONE • Ottenere artificialmente l’allineamento degli ingressi e degli anelli di retroazione 2 Segnale di sincronismo X0..n Y0..k Z0..m Rete combinatoria s/r0..k FF SR0..k t Segnale di sincronismo • Se la durata dell’impulso t è inferiore al tempo di reazione della rete combinatoria (ovvero il minimo ritardo della rete combinatoria) le nuove funzioni di eccitazione s/r0..k calcolate della rete combinatoria non raggiungono l’AND di blocco prima che le uscite degli AND stessi siano portate a zero rendendo stabili le uscite dei FF SR (il FF SR con gli ingressi entrambi a zero NON cambia stato. Solo al successivo impulso t le nuove funzioni di eccitazione (e quindi le nuove variabili di stato) sono avviate alla rete combinatoria senza che la retroazione faccia in tempo ad agire. Allineamento delle retroazioni • Si noti che così facendo anche l’effetto degli ingressi viene “allineato” • Le uscite sono esattamente “allineate” se la rete è di tipo Moore (dipendenti solo dalle variabili di stato) 3 Segnale di sincronismo • Il segnale di sincronismo viene sempre indicato con il nome di clock • Normalmente il segnale di clock è un segnale ripetitivo e cadenzato (quest’ultima caratteristica pressoché sempre ma non necessariamente rispettata) T Clock • Un FF SR dotato di segnale di clock viene chiamato SR sincrono (che però NON è mai usato nella realtà) • Quali problemi vi sono con un segnale di clock come quello riportato in figura ? L’impulso dovrebbe essere strettissimo dal momento che una rete combinatoria può consistere anche di un solo filo nel qual caso il ritardo da combattere sarebbe solo quello legato alla propagazione del segnale elettrico sui fili !!! Di fatto irrealizzabile 4 I FF sincroni • Esistono molti FF di tipo sincrono ma oggi si usa UNICAMENTE il FF D il cui comportamento è stato studiato come rete asincrona ma che qui viene utilizzato come FF sincrono (nella pratica nella sua versione 74xx74) D Q D CK !Q • Il FF D si chiama così perché D sta per Delay (ritardo). Infatti l’uscita Q segue l’ingresso D con un periodo T di ritardo (se il segnale di ingresso D è sincrono – ovvero generato contemporaneo al clock - nel rispetto di setup e hold - ad esempio da una rete controllata da altri FF D) oppure al primo fronte positivo del clock. • Il triangolo sul clock (CK) indica che è edge triggered ovvero che scatta sul fronte positivo del clock D PR D CK CL Q !Q I segnali !CL e !PR agiscono in modo asincrono ovvero immediatamente senza attendere il clock 5 Reti sequenziali sincrone X0..n Y0..k Z0..m Rete combinatoria Q0..k y0..k Si veda lo schema delle reti asincrone con la retroazione tramite FF RS in cui S=!R D0..k CK CK FFD0..k Clock • La sintesi si effettua come nel caso della rete asincrona con retroazione diretta ma ingressi che rimangono costanti sono ingressi considerati dalla rete come diversi (in quanto presi in considerazione in istanti diversi e quindi in possibile presenza di stati diversi) • Ciò che conta in questo caso è il fronte positivo del clock: la distanza fra successivi (nel rispetto di setup e hold – v. reti asincrone) NON ha importanza • Ovviamente il periodo (la frequenza) del clock deve essere superiore (inferiore) al massimo ritardo insito nella rete combinatoria. La rete combinatoria deve essersi stabilizzata a seguito di un fronte del clock prima che il successivo fronte si presenti fronti positivi 6 Reti Sequenziali Sincrone (RSS) S k S* ? S k (k) FFD CK S* k FFD sull’anello di retroazione Tutti con lo stesso clock di periodo T CK I S S* U t-T t Nel caso specifico: Moore o Mealy ? t+T t+2·T Lo stato cambia anche se non cambia l’ingresso ? L’uscita cambia anche se non cambia l’ingresso ?7 Il FFD come elemento fondamentale delle RSS Se all’ingresso CK viene inviato un segnale periodico (clock) il FFD ritarda (D = Delay) il segnale di uscita Q, rispetto al segnale di ingresso D, di un tempo pari al periodo di clock T se il cambiamento del segnale D è contemporaneo a quelli clock (nel rispetto di setup e hold) Qn+1 = Dn NB: essendo qui il tempo discretizzato si usa n e n+1 al posto di T e T+t D D Q Q Q* Q* FFD CK CK CK D Q T T T T NB: il concetto di contemporaneità potrebbe apparire in contrasto con la necessità di rispettare i tempi di setup e hold. Di fatto gli ingressi di una rete sincrona sono nella larga maggioranza provenienti da altre reti che hanno lo stesso clock e quindi sono generati con i ritardi delle reti soggette al clock, rispettando quindi di fatto i tempi previsti. Di fatto le variazioni degli ingressi sono sempre un po’ posteriori alla variazione del clock. Si veda in seguito il comportamento dei registri a traslazione 8 Alcune considerazioni sulle RSS • Lo stato della rete cambia solo in corrispondenza dei fronti di salita del clock che si susseguono con periodo T • La rete risponde ogni T ⇒ se si desidera massimizzare la velocità di risposta della uscita è necessario adottare il modello di Mealy • La sequenza degli stati della rete è svincolata dai ritardi della rete combinatoria (purché la distanza fra i fronti positivi del segnale clock sia superiore al massimo ritardo della rete combinatoria)! Quindi nessun problema di corse critiche • All’interno di uno stesso progetto (ad esempio un processore) sono tipicamente presenti più RSS e non necessariamente per tutte le RSS il clock è lo stesso e/o coincide con il clock del processore • Le RSS sono più facili da progettare delle RSA 9 Clock gating e glitch sul clock Nelle reti sincrone è necessario evitare variazioni spurie (glitches) del segnale di clock che possono provocare commutazioni indesiderate dei FFD (che sono sensibili ai fronti). Ad esempio, per via dei ritardi tra gli n segnali I[n-1..0] e/o le alee introdotte dalla rete combinatoria di decodifica, a causa del “clock gating“, può verificarsi quanto segue. X I[n-1..0] t Rete di Decodifica CK P CK D CK_G Q Q Q* Q* FFD CK P NO !! CK_G Glitch sul clock → possibile commutazione spuria del FFD Naturalmente tutto dipende dalla larghezza dell’impulso spurio: se molto stretto il FF potrebbe non sentirlo. Quindi il clock gating non è proibito ma è un rischio da evitare in caso di incertezza. 10 Clock gating e glitch sul clock Per transizioni che debbono o meno verificarsi in funzione del valore della rete di decodifica bisogna condizionare il segnale D come in figura. Se la rete di decodifica genera il valore 1 l’uscita Q assume al clock il valore di X altrimenti l’uscita Q copia sé stessa e rimane invariata X 0 0 1 1 D SEL SEL t I[n-1..0] Rete di Decodifica P Q Q Q* Q* FFD CK CK 11 Clock gating e clock-skew Il clock gating, oltre a generare potenziali glitch introduce “clock-skew” (disallineamento). Ad esempio, consideriamo due RSS soggette al FF1 e al FF2 I2 FFD-1 CK CK I1 A Q D A* Q* CK P CK_G B Q D FFD-2 CK B* Q* tAND I clock delle due reti sono sfasati di un tempo pari al ritardo introdotto dall’AND (in generale dalla eventuale RC) interposto. Tale fenomeno (“clock-skew”) è potenzialmente dannoso in quanto il FF2 potrebbe fare campionare alla propria RC in presenza dello stesso fronte di clock i nuovi valori prodotti dalla RC alimentata dal FF1 CK CK_G tAND tAND NB: Il “clock-skew” non è causato solo dal clock gating ma anche (ad esempio) da percorsi elettrici di lunghezza diversa. 12 Sincronizzazione degli ingressi • Finora si è dato implicitamente per scontato che gli ingressi di una rete sincrona commutino in modo sincrono con il clock • Ciò è verificato se gli ingressi provengono da una rete sincrona di tipo Moore nella quale le uscite sono funzione solo dello stato che commuta solo al fronte positivo del clock X0..n Rete combinatoria y0..k Y0..k FFD0..k Q0..k D0..k CK CK Clock Rete combinatoria Z0..m • Nella realtà le cose stanno diversamente. Si pensi al caso di pulsanti esterni che costituiscano l’ ingresso della rete. Il cambiamento può avvenire in un istante qualsiasi. • Nella rete di figura (Moore) le uscite sono comunque certamente sincronizzate con il clock e se gli ingressi X0..n cambiano in un momento qualsiasi non sincronizzato il cambiamento viene percepito dai FF di retroazione solo al fronte positivo del clock e quindi il comportamento delle uscite della rete è il medesimo che si avrebbe se gli ingressi fossero sincronizzati 13 Sincronizzazione degli ingressi • La cosa cambia però se la rete è di tipo Mealy Z0..m X0..n Y0..k Rete combinatoria Q0..k y0..k D0..k CK CK FFD0..k Clock • In questo caso un cambiamento asincrono degli ingressi provoca, in generale, un cambiamento asincrono delle uscite 14 … Cassaforte … sincrona …. Esempio: la cassaforte (dotata di una doppia tastiera - due ingressi) si apre solo se gli ingressi hanno assunto NEL TEMPO le configurazioni 00-01-01-10. Ogni violazione della sequenza riporta il sistema nello stato iniziale. NB Essendo gli ingressi campionati la sequenza di ingresso 01-01 è possibile e significativa 11 11 Per ogni stato tutte le combinazioni di ingresso !!!!!! A,0 00 00 00 11 00 B,0 01 11 D,0 00 11 01 10 E,1 10 10 10 Gli stati NON sono stabili per gli ingressi che li hanno provocati 01 C,0 10 01 01 00 11 00 G,0 11 10 01 F,0 10 01 01 NB: si può supporre che gli ingressi cambino allo stesso istante delle variabili di stato ma la cosa non è necessaria . Se la rete è di tipo Moore anche se gli ingressi cambiano a metà di un periodo di clock il comportamento dal punto di vista degli stati e quindi delle uscite è assolutamente lo stesso (ogni variazione è rilevata solo alla fine del 15 periodo) Cassaforte sincrona 11 X1 X2 00 11 A,0 00 11 00 01 B,0 11 01 C,0 D,0 00 11 01 10 E,1 10 10 10 00 01 11 10 A B F A G 0 B B C A G 0 C B D A G 0 D B F A E 0 E B F A G 1 F B F AA- G 0 G B F A 0 00 10 01 00 11 01 00 G,0 11 10 01 F,0 10 01 G 01 NB: in questo esempio non vi sono condizioni di indifferenza. Anziché di stati compatibili si parla qui di stati equivalenti. Ove poi due stati per gli stessi ingressi abbiano uscite identiche e portino agli stessi stati si parla di stati indistinguibili. Naturalmente la descrizione a parole può evidenziare che alcune combinazioni di ingresso per alcuni stati non si presentano. In questo caso si ritorna al concetto di compatibilità 16 Cassaforte sincrona X1 X2 00 01 11 10 A B F A G 0 B CF B B C A G 0 C FD CD C B D A G 0 D CF GE CF GE DF GE D B F A E 0 E B F A F F B F AA- G 0 --- CF DF GE G B F A G 0 G --- CF DF GE 00 01 11 10 A B C D a b a a a 0 b b g a a 0 g b d a a 0 d b a a e e b a a a X1 X2 G E 1 0 1 -- E F Classi di equivalenza [AFG] => a [B] => b [C] => g [D] => d [E] => e Ovviamente 5 stati: 4 facenti parte della sequenza e uno esterno NB: nel caso di tabelle completamente specificate le classi (massime) di equivalenza non hanno mai stati in comune. 17 Vanno usate tutte quindi. Non esiste problema di chiusura. Cassaforte sincrona X1 X2 Nessun problema di corse: codifica libera (possibilmente ottima) 00 01 11 10 a b a a a 0 b b g a a 0 g b d a a 0 d b a a e e b a a a 0 a b g d e => => => => => 000 001 011 010 100 1 Sintetizzando con FFD la sintesi degli ingressi Di si ottiene sintetizzando le funzioni Yi (Yn+1=Dn) Y1 Y2 X1 X2 00 01 11 10 Y3 000 001 000 000 000 0 001 001 011 000 000 0 011 001 010 000 000 0 010 001 000 000 100 100 001 000 000 000 1 101 -- -- -- -- -- 111 -- -- -- -- -- 110 -- -- -- -- -- D1= X1!X2Y2!Y3 D2=!X1X2Y3 D3=!X1!X2+!X1!Y2Y3 Z =Y1 18 0 Sintesi Direttorio cassaforte sincrona 19 Sintesi – simulazione funzionale 00 01 01 10 N.B. Gli ingressi cambiano in modo NON sincrono con il clock ma l’ uscita è sincrona essendo la rete di tipo Moore 20 Sintesi – simulazione timing d Si notino i ritardi delle uscite dei FF e dei gates da esse dipendenti rispetto al fronte positivo del clock (ad esempio d): se la frequenza del clock fosse eccessiva il sistema NON funzionerebbe più correttamente 21 E con Mealy ? X1 X2 X1 X2 00 01 11 10 A B F A G 0 B B C A G 0 C B D A G 0 D B F A E 0 E B F A G 1 F B F AA- G 0 G B F A 0 G 00 01 11 10 A B,0 F,0 A,0 G,0 B B,0 C,0 A,0 G,0 C B,0 D,0 A,0 G,0 D B,0 F,0 A,0 E,1 E B,1 F,1 A,1 G,1 Potrei mettere una indifferenza F B,0 F,0 G B,0 F,0 sull’uscita ?? Si: si possono mettere indifferenze sulle A,0A-G,0 uscite che cambiano. Anticipazione o ritardo del A,0 G,0 cambiamento Sintetizzare e simulare con Altera 22 • • • • All’esame orale è necessario portare un esercizio di reti sincrone e uno di reti asincrone NON “mutuato” da altri … I due esercizi debbono essere portati su una chiavetta (o dispositivo equivalente) debbono contenere una spiegazione e anche la progettazione/simulazione con Altera Il candidato deve dimostrare di sapere usare il sistema Altera e spiegare i progetti portati Gli esercizi di reti sincrone hanno spesso il diagramma degli stati ma solo per verifica… 23 Monoimpulsore A Generare un impulso di uscita di un periodo di clock per ingresso 1. Un ulteriore impulso viene generato solo se l’ingresso torna a 1 dopo essere stato a 0. L’uscita deve essere sincronizzata con il clock D D1 Q1 FFD Clock CK !Q1 D2 Q2 FFD CK !Q2 Z1 Z !Q2 Q1 D Clock Qui l’ingresso asincrono D è sincronizzato dai FF. Uscita Z sincrona 24 Monoimpulsore A 0 1 A,0 B,1 0 Moore necessariamente ! 1 0 C,0 Q1 Q1 D Q1 0 1 Z A A B 0 A B A C 1 C A C - 0 1 D 1 Z 00 00 00 10 0 B 10 01 -- - 0 C 11 11 00 11 0 - - - 01 10 00 11 1 1 Z 00 00 10 0 Q2 D Q2 01 00 10 0 11 01 11 0 10 01 11 1 Q2 0 -- Q1=D Q2= DQ1 Z=Q1!Q2 MA… D Q1=D Q2= Q1 Z=Q1!Q2 Clock D1 Q1 FFD CK !Q1 D2 Q2 FFD CK !Q2 Z 25 Monoimpulsore B D D1 Q1 FFD Clock CK !Q1 D2 Q2 FFD CK !Q2 Z2 Qui la rete è di tipo Mealy e quindi con ingresso asincrono è possibile che vi sia uscita asincrona Z2 !Q2 Q1 D Clock L’ingresso asincrono D agisce direttamente sull’uscita Z che quindi risulta asincrona 26 Monoimpulsore C D D !Q FFD Clock CK Q Z Qui la rete è di tipo Mealy e quindi con ingresso asincrono è possibile che vi sia uscita asincrona Z Q D Clock Anche qui l’ingresso asincrono D agisce direttamente sull’uscita Z che quindi risulta asincrona Si noti che se l’ingresso oscilla, una volta che il FF ha campionato un 1 e fino a quando non campiona uno 0 , l’uscita oscilla 27 Considerazioni sui monoimpulsori A, B e C Il diagramma degli stati corrispondente al funzionamento reale dei due monoimpulsori B e C NON può essere tracciato perché di fatto le due reti (di tipo Mealy) NON sono sincrone. Infatti il diagramma di circuiti sincroni prevede implicitamente un comportamento sincrono anche degli ingressi, fatto non verificato nei casi B e C La cosa non vale per il monoimpulsore A in quanto pur essendo l’ingresso asincrono l’uscita (rete di tipo Moore) dipende solo dagli stati. In altre parole il comportamento della rete rende intrinsecamente sincroni ingressi fisicamente asincroni Il diagramma degli stati che riflette il comportamento delle due reti B e C può essere tracciato solo partendo da una analisi asincrona, “aprendo” quindi i FF D inseriti. Ovviamente è possibile progettare le due reti senza l’uso dei FF D partendo da un diagramma degli stati asincrono “tradizionale” A scopo di esercizio si suggerisce la sintesi e la simulazione con Altera dei tre monoimpulsori come reti asincrone. Si tratta di circuiti on due ingressi: Ck e D. 28 Monoimpulsori A-B-C 29 30 Contatori Circuiti senza ingresso (a parte il clock) nella versione più semplice A B C D Z Esempio: contatore binario x 4 con decodifica del 3 00,0 !Q0 D0 FFD CK U0 Q0 01,0 1 M U 0 X 10,0 !Q1 D1 FFD CK 11,1 Q1 OUT U1 Q1 cambia stato quando Q0 è a 1 e passa a 0 (Il clock è spesso sottinteso nei circuiti sincroni) 31 Contatore x 4 con decodifica del 3 CK u1 u0 OUT (0) (1) (2) (3) (0) (1) (2) (3) Contatori binari in base non potenza di 2 !Q0 D0 FFD CK Q0 A B C D E 000 001 010 011 100 1 M U 0 X !Q1 D1 CK FFD 1 Q1 1 M U 0 X Contatore binario per 5 !Q2 D FFD CK Q2 Questo conta x8: ma per contare x5, arrivati a 4 bisogna ritornare a 0 !!! 33 Contatore x 5 !Q0 D0 FFD CK Q0 1 M U 0 X D1 !Q1 FFD CK “4” A B C Q1 1 M U 0 X D2 !Q2 FFD CK Q2 “3” Decoder La decodifica del 4 porta a zero l’uscita del decodificatore e quindi a 0 tutte le uscite degli AND rosa e al successivo fronte positivo del clock i tre FF campionano uno “0”. Per esercizio sintetizzare un contatore x 100 partendo dalla sintesi di un contatore decimale ovvero di un contatore x10 (da sintetizzare). Quanti FF per un contatore decimale ? I contatori decimali si trovano integrati in Altera 34 Contatori con ingressi di controllo EN CK D0 D1 D2 D3 LD Q0 Q1 Q2 Ex. Contatore integrato x 16 con Load e Enable Q3 • Il contatore conta per 16 (0-15) se il segnale EN è a 1. Allorchè il segnale LD va a 1 il dato presente sugli ingressi D è inserito nei 4 FF (l’ingresso può essere sincrono o asincrono). Nel caso precedente il decodificatore del “3” (uscita vera va portato) all’ingresso LD con tutti i Di a zero. • In generale il contatore fornisce anche un’uscita “carry” che va a 1 quando il contatore raggiunge il valore FF. Questa uscita può essere connessa all’enable di un contatore a valle per ottenere un contatore per 256 così via. (Progettarlo come esercizio) EN CK D0 D1 D2 D3 Q0 Q1 Q2 Q3 CY LD • Esistono contatori UP/DOWN nei quali un ingresso (U/!D) seleziona se il conteggio deve avvenire avanti o indietro. Nel caso sia selezionata la modalità “indietro” il carry si attiva quando si raggiunge il valore “tutti zeri”. • Esiste una molteplicità di contatori ciascuno con le proprie specifiche peculiarità; con o senza RESET (che normalmente agisce in modo asincrono) , U/!D, con o senza LD etc. etc. NB: qualunque circuito sincrono (con sequenza non binaria) riconducibile al diagramma degli stati di un contatore è sempre un contatore 101 010 000 111 110 Contatore x 5 non binario 35 Contatore binario x 8 e glitches 74163: contatore reale x 16 con Load, Reset e Enable (T e P) I segnali di controllo sono sincroni ovvero agiscono sul fronte positivo del clock (rising edge) 74138: decoder 3:8 con uscite negate se G2A e G2B entrambi a zero e G1 a 1. Altrimenti tutte uscite alte Direttorio Counter Glitch 36 Glitch !!! Simulazione timing NB: la presenza e la durata del glitch dipende dalle caratteristiche elettriche dei dispositivi, dalla loro tecnologia etc. Nel caso dei dispositivi Altera dipende dal tipo di dispositivo sul quale è realizzato il circuito. Analogamente la sensibilità di eventuali ingressi di clock collegati all’uscita con il glitch dipende dalle caratteristiche del dispositivo. Se ad esempio nel dispositivo Altera utilizzato si collega all’uscita Y6 il clock di un FFD non si ha commutazione del FF ma questo non è vero in assoluto !!!! 37 Cosa succede al contatore X5 progettato precedentemente se all’accensione, non disponendo di un segnale di RESET i FF si portano in uno stato non facente parte del ciclo. NB La condizione all’accensione è del tutto casuale e dipende unicamente dalle condizioni elettriche di realizzazione. E’ impredicibile Supponiamo che i FF si portino al valore 110 (il numero 6, fuori dal ciclo). Analizziamo il comportamento 000 !Q0 D0 FFD CK 001 Q0 010 1 M U 0 X 011 D1 !Q1 FFD CK “4” Q1 100 110 1 M U 0 X 111 D2 !Q2 FFD CK Q2 A B C In questo caso ci si riporta nella situazione di conteggio regolare (verificare con la tabella degli stati !) ma il comportamento in generale dipende dalla realizzazione e in altre realizzazione i due stati potrebbero essere separati dal ciclo principale che quindi non verrebbe mai raggiunto. Ecco la 38 funzione del RESET Solo come esempio (da non utilizzare !!!!!!) a scopo didattico vediamo la tabella delle transizioni di un contatore per 6 Up/!Down con comando di Reset. I segnali di ingresso cambiano in modo asincrono ma hanno effetto in modo sincrono Up/!Down Res Up/!Down Res 00 01 00 01 000 101 000 000 001 000 101 000 000 001 001 000 000 000 010 001 000 000 000 010 010 001 000 000 011 010 001 000 000 011 011 010 000 000 100 011 010 000 000 100 100 011 000 000 101 100 011 000 000 101 101 100 000 000 000 101 100 000 000 000 110 ? ? ? ? 110 000 000 000 000 111 ? ? ? ? 111 000 000 000 000 y3 y2 y1 11 10 y3 y2 y1 Per compensare all’accensione 11 10 Sintetizzare e simulare. Come dovrebbe essere modificato lo schema in Altera per permettere di “presettare” in modo asincrono il contatore a un particolare valore di ingresso ? 39 Sintesi di y2 in modo “diretto” Up/!Down Res y3 y2 y1 000 00 01 11 10 101 000 000 001 UP/!Down 001 000 000 000 010 010 001 000 000 011 011 010 000 000 100 100 011 000 000 101 101 100 000 000 000 110 000 000 000 000 111 000 000 000 000 “1” y3 y2 y1 D E C “2” 11 D0 “3” “4” y2 FFD Q0 00 Clock CK 40 Cassaforte … Disponendo di un contatore per 8 (ma anche per 16 etc.) con reset sincrono e sempre abilitato al conteggio come potrei realizzare il circuito di apertura della cassaforte (sequenza X1X2 00-01-01-10) con modello Moore ? RES CK Cx8 Q0 Q1 Q2 RES= !(“0”!X1!X2 + “1” !X1X2 + “2” !X1X2 + “3” X1 X2) Z = “4” (“0”,”1”,”2”,”3”,”4” sono le decodifiche binarie delle tre uscite del contatore) Il contatore si resetta ogni volta che non si presenta l’ingresso giusto relativo al particolare stato Ilcontatore quindi si resetta e rimane resettato se non nelle condizioni espresse dalla funzione RES Il contatore arrivato a 4 (Z=1) si resetta comunque al successivo fronte del clock Le reti sincrone si progettano sempre come combinazione di blocchi disponibili e logica “random” RES CK Cx8 X2 X1 Q0 Q1 Q2 A “0” B “1” C “2” “3” “4” RL AND-OR RES Z 41 Contatori • Attenzione !!! Consideriamo il contatore di figura (questa volta con RESET asincrono) e supponiamo di utilizzarlo per contare per 5. (N.B. per il Reset si usa il “5” in questo caso…. glitch..) “1” RESET EN CY CK “5” Perché questo schema è sbagliato ? Q0 Q1 Q2 Q3 A B C D • Perché presenta una corsa critica !! Nel momento in cui anche uno solo dei FF si resetta (e non tutti nello stesso istante) viene a mancare la configurazione “4” sul decoder e quindi alcuni FF potrebbero non fare in tempo a resettarsi. E allora ? “1” EN CY CK Y S “5” R “0” RESET Q0 Q1 Q2 Q3 A B C D • Così facendo il “4” attiva il SET e il FF NON si resetta fino a quando non è stato raggiunto la “0”. NB lo schema “sbagliato” si può usare solo se si è certi della rapidità di reset dei FF del contatore • Verificare con Altera 42 Sintesi cassaforte con moduli Altera Cassaforte sincrona con moduli Rete di controllo Contatore con Reset asincrono e Load sincrono NB In questo progetto la sintesi è stata condotta in modo “diretto” ovvero senza passare per la sintesi formale e utilizzando componenti disponibili e ……. materia grigia. La sintesi dei circuiti sincroni si fa sempre e unicamente così 43 Simulazione funzionale (no timing) 00 01 01 10 N.B. I segnali di ingresso sono campionati SOLO sul fronte positivo del clock anche se si presentano asincroni !! Il segnale di uscita si attiva al clock successivo al riconoscimento della sequenza. La posizione di “riposo” del contatore è il valore 4. I segnali Yi sono le decodifiche dei segnali di di ingresso X1 e X2 44 Simulazione timing 45 N.B. Si è scelto di utilizzare SOLO gli ingressi SINCRONI del contatore per semplicità. Il contatore rimane al valore 100 fino a quando non si presenta all’ingresso il valore 00. Se la sequenza è esatta il contatore continua a contare in avanti fino alla generazione dell’uscita (valore 11 del contatore) altrimenti si riporta al valore 100 ovvero Qc=1). Il segnale GN (Gate Not) è quello che abilita il conteggio. Il sistema riamane stabile a 000 per una sequenza lunga a piacere di X1=0 e X2=0 e si sposta quando dopo 00 si ha 01. Come si evince dalla simulazione se la sequenza non è corretta o è interrotta il contatore si riporta sempre a 100 X2 X1 00 01 11 10 000 000 001 000 000 0 001 000 010 100 100 0 010 000 100 100 011 0 011 100 100 100 100 1 100 000 100 100 100 0 101 000 100 100 100 0 110 000 100 100 100 0 111 000 100 100 100 0 NB: la tabella delle transizioni derivata della rete realizzata NON ha ovviamente condizioni di indifferenza 46 Progettare un contatore packed BCD up/down a 8 bit (due digit) 47 Generazione di forme d’onda • E’ possibile generare forme d’onda periodiche mediante circuiti sincroni di periodo sottomultiplo intero del clock Esempio 1:Divisore di frequenza per 2 Q D0..k Q0..k !Q D CK Clock CK Esempio 2: generare una forma d’onda periodica con periodo 5T (ove T sia il periodo del clock) in cui in un semiperiodo 3T l’uscita sia alta e nell’altro semiperiodo 2T l’uscita sia bassa Cx5 CK Q0 Q1 Q2 3T 3T 2T C B A 0 1 2 3 4 Z Z T Clock Decoder/Demux NB: una rete logica è in grado di effettuare delle divisioni di frequenza e mai delle moltiplicazioni di frequenza (che si possono ottenere solo con circuiti analogici non lineari) 48 Di che circuito si tratta ? D0..k D0 CK CK Q0..k !Q0 D0..k D1 CK CK Q0..k !Q1 D0..k D2 CK CK Q0..k !Q2 NB: il segnale di clock non è in comune Clock !Q2 !Q1 !Q0 Clock E’ un contatore binario ma non sincrono. Infatti i vari FF NON utilizzano lo stesso clock e questo porta a un piccolo disallineamento sulle uscite. Non è sintetizzabile come una rete sincrona e una sintesi formale sarebbe possibile solo trattando il circuito come asincrono ovvero “aprendo” i FF. Sarebbe possibile trasformarlo in un contatore x6 mantenendo la stessa impostazione ? Sintetizzare e simulare con Altera 49 7493 50 Contatore asincrono Altera Contatore asincrono 51 Simulazione timing 52 Come può essere utilizzato un FFD per catturare un impulso più breve di un periodo ? Monoimpulsore di tipo A “rivisto” “1” D0 CK CL FFD Q00 !Q0 D1 Q1 FFD CK !Q1 D2 Q2 FFD CK !Q2 Z Clock L’impulso breve viene catturato dal FF 0 (purché di larghezza sufficiente per la tecnologia del FF) - che quindi agisce come integratore – la cui uscita alimenta il monoimpulsore di tipo A. L’attivazione del FF 1 resetta il FF 0 (supponendo che il segnale di CL sia “positive”true”) Ci può essere un problema se il CL agisce in modo asincrono ? NB: questo circuito e quello del lucido precedente evidenziano il fatto che nella realtà nessuna rete è solo sincrona ma bensì è pressoché sempre necessario utilizzare reti di natura diversa anche perché vi è sempre una interazione fra reti con clock diversi e/o con segnali provenienti dal mondo esterno NON sincronizzati con il clock 53 Shift register (registri a traslazione o scorrimento) • Uno shift register a sinistra (a destra) è un registro composto da FFD che ad ogni clock trasferisce il valore del FF a destra (a sinistra) di ciascun FF nel FF stesso. Nel FF più a destra (sinistra) viene immesso uno “0”. Questi tipi di registri shift si chiamano “logici” Q0..kQ n D0..k CK Dn CK Q0..kQ D0..k n-1 CK Dn-1 CK Q0..kQ D0..k n-2 CK Dn-2 CK Q0..kQ 0 D0..k CK “0” D0 CK Shift register a sinistra • Anche per i registri a traslazione esistono diverse versioni: con ingresso parallelo e uscita seriale, con ingresso seriale e uscita parallela, con reset, con load etc. etc. • Si noti che uno shift register è anche un contatore. Si immagini per esempio che dopo un reset siano inseriti degli uni a partire da destra. Lo shift register si riempie progressivamente di uni e quindi la posizione in cui è arrivato l’uno indica il valore del conteggio in base a un codice “uno su n” (un codice decodificato) • Spesso uno stesso registro può traslare a destra o a sinistra in funzione di una segnale di controllo. Ovviamente questo si ottiene premettendo a ogni ingresso Di un MUX a due vie che preleva in funzione del segnale di controllo Qì+1 o Qì-1. Con questa configurazione lo shift register diventa anche un contatore avanti/indietro 54 Registro a scorrimento (shift-register) a 3 bit. OUT0 IN D Q FFD R* A_RESET* CK D Q FFD Q* OUT2 OUT1 R* D Q FFD Q* A_RESET* R* Q* A_RESET* Registro a scorrimento (shift-register) a 3 bit. CK IN A_RESET OUT2 OUT1 OUT0 Esempio: 74164 (serial In parallel OUT) • In questo registro a traslazione, ad ogni fronte positivo del clock i dati sono traslati a destra (Q0 -> Q1, Q1->Q2 etc). Il registro è dotato in un Master Reset (vero negato) e il dato inserito nel FF Q0 è dato dall’AND dei due ingressi Dsa e Dsb • Si noti che l’operazione di shift corrisponde aritmeticamente alle operazioni di divisione e moltiplicazione per 2. Si supponga che in Q0 vi sia il bit meno significativo e in Q7 il meno significativo 101011002 = 21610 010101102 = 10810 NB: nel dispositivo i bit sono posti in ordine invertito e quindi un shift left del numero corrisponde a uno shift right sul dispositivo 001010112 = 5910 0 1 1 0 1 0 1 0 57 Shift aritmetico • Esistono anche i registri a traslazione “aritmetici”. In questi shift register a destra anziché fare entrare nel FF più a sinistra lo “0” viene immesso sempre ripetutamente il suo valore logico. D7 D6 D5 D4 D3 D2 D1 D0 LD CK I Esempio Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 SRA 11001010 C2 001101102=5410 11100101 interpretato in complemento a 2 C2 000110112=2710 • Lo shift aritmetico a destra effettua una divisione per 2 mantenendo il segno !! 58 Rotazione Nei computer è sovente necessario utilizzare una rotazione a destra o a sinistra del contenuto dei FF. La cosa si ottiene retroazionando uno shift register Q0..kQ n D0..k CK Dn CK Q0..kQ D0..k n-1 CK Dn-1 CK Q0..kQ D0..k n-2 CK Dn-2 CK Q0..kQ 0 D0..k CK D0 CK Molto spesso nei computer è necessario utilizzare una rotazione a destra o a sinistra del contenuto dei FF. La cosa si ottiene retroazionando uno shift register con direzione programmabile. In questo caso su D0, ad esempio, può essere avviato o Q1 o Qn 59 Contatori con shift register – Contatore retroazionato EX-OR D Shift right 3 bit Q0 100 110 111 011 Q1 Q2 101 010 001 000 Diagramma degli stati disgiunto !! Uno shift register con n FF retroazionato con un EX-OR (scelta degli ingressi variabile) è un contatore NON binario che conta per 2n-1 (purché presettato a un valore diverso da tutti zeri) 60 Contatore di Johnson (riempimento e svuotamento) OUT0 D Q FFD R* D Q FFD Q* A_RESET* OUT2 OUT1 R* D Q FFD Q* A_RESET* R* Q* A_RESET* CK 000->100->110->111->011->001->000->... Stati isolati: 101->010->101..>1 Poiché configurazioni adiacenti del codice Johnson differiscono di un solo bit, il contatore può essere utilizzato per generare forme d’onda prive di alee. 61 Contatore ad anello con un solo 1 (ovvero che genera direttamente il codice 1su n) OUT0 D Q FFD R* D Q FFD Q* RESET* OUT2 OUT1 R* D Q FFD Q* RESET* R* Q* RESET* OUT3 D Q FFD PR* Q* RESET* CK 0001->1000->0100->0010->0010 n FF per contare per n (mentre con i contatori binari il numero dei FF è il log2m ove m è il primo intero maggiore o uguale a n) 62 Barrel shifter (rotore) Un barrel shifter è uno shift register in grado di traslare di “n” posizioni in un solo clock il contenuto dei suoi FF. In figura è riportato il barrel shifter della Altera. Gli ingressi A-H in presenza dell’attivazione del segnale LDST, al primo fronte positivo del clock sono depositati nei FF. Quando LDST è 0 ad ogni fronte positivo del clock i bit di uscita sono ruotati di n posizioni in senso antiorario (ovvero l’uscita H diventa la G, la G diventa la F…e l’uscita A diventa la H) ove n è il valore binario indicato dai segnali S0, S1 e S2. Si noti che il circuito in questione è di fatto un registro con 8 FF all’ingresso di ciascuno dei quali è previsto un MUX a 8 vie che pilotato dai segnali S0, S1 e S2 che seleziona uno degli 8 uscite del dispositivo. La struttura interna può essere osservata “clikkando” due volte sul dispositivo nello schema di Altera. 63 Barrel shifter 64 65 65 Simulazione timing 66 • Utilizzando il sistema Altera progettare un orologio con secondi, minuti, ora, partendo da un oscillatore a quarzo con frequenza 500 KHz. • E se si volesse proseguire e realizzare anche un datario (giorno, mese e anno ) ? • Come potrebbe essere integrato con una sveglia. Si ricordi che l’orologio deve essere anche essere “presettato”. • Quali circuiti utilizzare per la visualizzazione ? 67 Reti sincrone con EPROM Z0..m X0..n Y0..k EPROM Q0..k y0..k D0..k CK CK FFD0..k Clock Al posto delle EPROM si utilizzano ora dei PLA ovvero dispositivi nei quali si nei quali le funzioni combinatorie sono ottimizzate ma il principio è assolutamente il medesimo 68 Progettare con Altera una rete logica sincrona che utilizzando registri 374, ALU 74181, un contatore e altri dispositivi ritenuti necessari, permetta di eseguire in sequenza la somma di due dati di 4 bit senza segno ingresso, esegua il complemento a 2, inverta la parte bassa con la parte alta del risultato e infine moltiplichi il tutto logicamente per 2. La soluzione è sempre decomponibile in tre sottosistemi: il controllo con la sua decodifica (unità di controllo), il percorso dei dati con le unità che li trasformano (datapath) e i registri di deposito e di ingresso dei dati. Questa è la struttura base di qualunque unità centrale di qualunque computer. La differenza consiste solo nel fatto che anziché avere una sequenza fissa di operazioni ne viene generata una volta a volta che dipende appunto dalla istruzione che deve essere eseguita. Come si vedrà approfonditamente nel corso di Calcolatori T del II anno (prof. Neri e Mattoccia). Arrivederci al corso di Calcolatori T del II anno (sapendo perfettamente le reti logiche ……) !!! 69

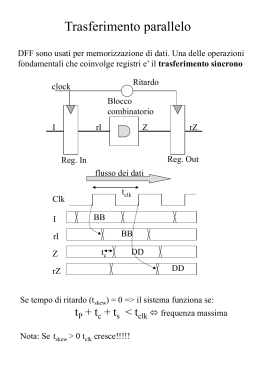

Scaricare