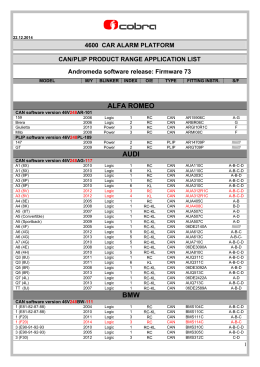

Dispositivi e sistemi logici Sistemi Elettronici Programmabili 2.1 Small Scale of Integration (SSI) Part Name Function *74*00 Quad 2-Input NAND Gates *74*01 Quad 2-Input NAND Gates Open Collector *74*02 Quad 2-Input NOR Gates .. *74*04 .. Hex Inverter .. *74*10 .. Triple 3-Input NAND Gates .. *74*20 .. Dual 4-Input NAND Gates .. *74*137 .. 3 to 8 Decoder Multiplexer .. *74*169 .. Sync. Up/Down Binary Counter .. *74*175 .. *74*1244 .. Quad D Flip-Flop .. Octal Bus/Line Driver 2.2 Progettazione SSI 1 2 3 4 1 2 U1A 3 6 A U2A 1 2 A 4 5 74AC00MTC DM74ALS21AN U3A CLK CLR 2 1 CLK 3 Instance Name 4 A U2B DM74ALS02N Sub-Part Name U4 6 5 B B 9 C 1 9 U3C 8 74AC00MTC 10 5 DM74ALS02N 8 10 D 4 9 U2C VCC 12 74AC00MTC 13 8 CLR CLK D1 D2 D3 D4 U3B VCC 16 5 4 6 Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 2 3 7 6 10 11 15 14 DM74ALS02N VCC 1 GND 9 7 10 1 2 U3D 11 E 13 Part Name 12 DM74ALS02N C 9 10 U5A U6 74AC00MTC CLK 3 4 5 6 U1B 8 12 13 8 LD ENP ENT U/D CLK A B C D 3 VCC RCO 16 B 2 RCO 74AC00MTC 15 OUT[0..3] QA QB QC QD 14 13 12 11 OUT0 OUT1 OUT2 OUT3 C GND DM74ALS169BN DM74ALS21AN Title D Size Number Revision D A3 Date: File: 1 2 25/09/2003 C:\Inetpub\..\74xx.SchDoc 3 Sheet of Drawn By : 4 2.3 Scheda PGC (risoluzione 640x480 256 colori) 74ASxxx (~250 chip) 2.4 Very Large Scale of Integration (Non Riprogrammabili) Full Custom Standard Cell Gate Array Vengono disegnate tutte le maschere Costi di progetto elevatissimi Costi di realizzazione elevatissimi Basata su celle predisegnate Costi di progetto Elevati Costi di realizzazione elevati Vengono Disegnate le sole interconnessioni Costi di progetto Elevati Costi di realizzazione meno bassi (Non Riprogrammabili) 3 – Input NAND 2.5 Logic Devices ASIC (Application Specific Integrated Circuit) • Standard Cell • Gate Array Programmate durante la produzione nella Fab PLD (Programmable Logic Devices) • SPLD (Simple PLD) • PLA (Programmable Logic Array) • PAL (Programmable Array Logic) • GAL (Generic Array Logic) • CPLD (Complex PLD) • FPGA Re/Programmabili sul campo Re/Programmabili nel circuito 2.6 Prime Strutture PLD INn INn IN3 IN2 IN3 IN2 IN1 IN1 OUT1 OUTm OUT3 OUT2 OUT1 Programmable Logic Array (PLA) OUTm Programmable Array Logic (PAL) 2.7 PLA: Simbologia a) Z Z = A1CD1 a) Z A B C D .. 2.8 Programmable Array Logic (PAL) 2.9 PAL: Architettura della GAL16LV8 Output Logic Macro Cell 2.10 Sistema Digitale Elementare OUT IN Logic CLK 2.11 Sistema Digitale Complesso IN OUT Logic OUT Logic IN CLK 2.12 PAL: Programmable Array Logic 2.13 Sistemi di Programmazione Giunzione di tipo AntiFuse Giunzione di tipo Fuse 2.14 OLMC: Configurazione Registered Mode, Registered Configuration 2.15 Complex Programmable Logic Devices 2.16

Scaricare