Università degli studi di Pavia

Facoltà di Ingegneria

Corso di Laurea Specialistica in Ingegneria Elettronica

INTERFACCIA I2C PER LA LETTURA

E LA PROGRAMMAZIONE DEL CIRCUITO

INTEGRATO DI CONTROLLO DI UNA MATRICE DI

SENSORI DI GAS

Relatore:

Chiar.mo Prof. Piero Malcovati

Correlatori:

Dott. Ing. Marco Grassi

Ing. Fabrizio Conso

Tesi di Laurea di

Claudio De Berti

Anno Accademico 2010/2011

Indice

Elenco delle figure

5

Elenco delle tabelle

7

Introduzione

9

1

2

3

Descrizione del Sistema

1.1 Matrice di sensori . . . . . . . . . . . . . .

1.2 Interfaccia di controllo e lettura dei sensori

1.2.1 Circuito per la lettura dei sensori . .

1.2.2 Interfaccia seriale . . . . . . . . . .

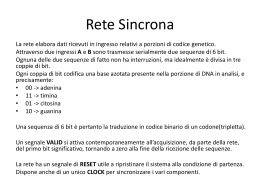

Linguaggi HDL

2.1 VHDL . . . . . . . . . . . .

2.1.1 Livelli di astrazione .

2.2 Verilog . . . . . . . . . . . .

2.3 Macchina a stati finiti . . . .

2.3.1 FSM adottata . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

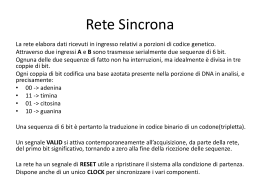

Interfaccia seriale

3.1 Protocollo I2 C . . . . . . . . . . . . . . .

3.1.1 Regole di comunicazione . . . . .

3.1.2 Temporizzazioni . . . . . . . . .

3.2 Registri . . . . . . . . . . . . . . . . . .

3.2.1 Registri di controllo . . . . . . .

3.2.2 Registri di lettura . . . . . . . . .

3.3 Realizzazione dell’interfaccia . . . . . . .

3.3.1 Sequenze di trasmissione . . . . .

3.3.2 Schema a blocchi dell’interfaccia

3.3.3 Sistema descritto in VHDL . . . .

3.3.4 Simulazioni . . . . . . . . . . . .

Claudio De Berti

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

11

11

13

13

15

.

.

.

.

.

17

17

18

19

19

20

.

.

.

.

.

.

.

.

.

.

.

23

23

24

25

26

28

31

32

32

34

34

37

3

INDICE

4

5

Sintesi e Place and Route

4.1 Sintesi . . . . . . . . . . . . . .

4.1.1 Esecuzione della sintesi

4.1.2 Risultati della sintesi . .

4.1.3 Simulazioni post-sintesi

4.2 Place and Route . . . . . . . . .

4.2.1 Realizzazione del layout

4.2.2 Simulazioni post-layout

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Simulazioni in Cadence Virtuoso

5.1 Simulazioni con segnali misti . . . . . . . . .

5.2 Programmazione del master I2 C . . . . . . .

5.3 Test Bench per l’interfaccia I2 C . . . . . . . .

5.3.1 Simulazioni . . . . . . . . . . . . . .

5.3.2 Valutazione dei consumi . . . . . . .

5.4 Inserimento dell’interfaccia nel microsistema

5.4.1 Simulazione dell’intero sistema . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

45

45

46

46

48

50

51

54

.

.

.

.

.

.

.

59

59

60

60

61

61

63

63

Conclusioni

67

Bibliografia

69

Ringraziamenti

71

A Codici HDL

A.1 Codici VHDL . . . . . . . . . . . . . . . .

A.1.1 Descrizione dell’interfaccia . . . .

A.1.2 Test Bench . . . . . . . . . . . . .

A.1.3 Package . . . . . . . . . . . . . . .

A.2 Codici Verilog . . . . . . . . . . . . . . . .

A.2.1 Descrizione della cella master . . .

A.2.2 Descrizione della cella altri segnali

.

.

.

.

.

.

.

73

73

73

81

87

92

92

96

B Script

B.1 Script per l’esecuzione della sintesi . . . . . . . . . . . . . . . . . . . . .

B.2 Script per la realizzazione del layout . . . . . . . . . . . . . . . . . . . .

99

99

99

4

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Claudio De Berti

Elenco delle figure

1.1

1.2

1.3

1.4

Schema semplificato della griglia di sensori di gas . . . . . . . . . . . .

Schema a blocchi del circuito di lettura e di controllo della temperatura

Schematico semplificato del circuito di misura di resistenza . . . . . . .

Schema a blocchi del microsistema con interfaccia I2 C . . . . . . . . .

.

.

.

.

12

13

14

16

2.1

Diagramma a bolle di una FSM . . . . . . . . . . . . . . . . . . . . . . .

20

3.1

3.2

3.3

3.4

24

24

25

3.6

3.7

3.8

3.9

3.10

3.11

3.12

3.13

3.14

3.15

3.16

3.17

3.18

Condizione di Start e condizione di Stop . . . . . . . . . . . . . . . . . .

Trasferimento di un bit . . . . . . . . . . . . . . . . . . . . . . . . . . .

Invio di un byte sul bus . . . . . . . . . . . . . . . . . . . . . . . . . . .

Sequenza di scrittura di un singolo registro (sopra) e di registri con indirizzi consecutivi (sotto) . . . . . . . . . . . . . . . . . . . . . . . . . . .

Sequenza di lettura di un singolo registro (sopra) e di registri con indirizzi

consecutivi (sotto) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Temporizzazioni del protocollo . . . . . . . . . . . . . . . . . . . . . . .

Sequenza di trasmissione per la lettura dei registri OUT REG . . . . . . .

Sequenza di trasmissione per la lettura dei registri CTRL REG . . . . . .

Sequenza di trasmissione per la scrittura dei registri CTRL REG . . . . .

Schema a blocchi dell’algoritmo per l’interfaccia . . . . . . . . . . . . .

Il processo rilevatore condizioni . . . . . . . . . . . . . . . . . . . . . .

Il processo registri lettura . . . . . . . . . . . . . . . . . . . . . . . . . .

Il processo FSM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Buffer linea SDA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Il processo registri scrittura . . . . . . . . . . . . . . . . . . . . . . . . .

Sistema digitale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Simulazione della lettura della misura di default . . . . . . . . . . . . . .

Simulazione della scrittura dei registri di controllo . . . . . . . . . . . . .

26

27

33

33

33

35

36

37

38

38

38

39

41

42

4.1

4.2

4.3

4.4

4.5

4.6

Schematico generato da Encounter

Un dettaglio dello schematico . .

Floorplanning del circuito . . . . .

Layout delle alimentazioni . . . .

Posizionamento delle celle . . . .

Layout completato . . . . . . . .

47

47

51

52

53

53

3.5

Claudio De Berti

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

26

5

ELENCO DELLE FIGURE

6

4.7

4.8

4.9

Simulazione con annotazione SDF, prima parte . . . . . . . . . . . . . .

Simulazione con annotazione SDF, seconda parte . . . . . . . . . . . . .

Simulazione con annotazione SDF, terza parte . . . . . . . . . . . . . . .

55

56

57

5.1

5.2

5.3

5.4

Cella master . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Schematico del Test Bench . . . . . . . . . . . . . . . . . . . . . . . . .

Schematico del sistema . . . . . . . . . . . . . . . . . . . . . . . . . . .

Segnale di controllo e oscillazioni generate dal circuito di misura (sopra)

- Lettura della misura e scrittura dei registri di controllo (sotto) . . . . . .

60

62

64

65

Claudio De Berti

Elenco delle tabelle

3.1

3.2

3.3

3.4

3.5

3.6

3.7

3.8

3.9

Specifiche di temporizzazione dei segnali . .

Set di registri . . . . . . . . . . . . . . . . .

Bit del registro SET REG1 . . . . . . . . . .

Bit del registro SET REG2 . . . . . . . . . .

Bit dei registri TEMP REGx . . . . . . . . .

Bit del registro CTRL REG1 . . . . . . . . .

Bit del registro CTRL REG2 . . . . . . . . .

Bit dei registri OUT REGx . . . . . . . . . .

Bit dei registri OUT TEMP1 e OUT TEMP2

Claudio De Berti

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

27

28

28

29

30

30

30

31

32

7

Introduzione

Il progetto di tesi è stato realizzato nel laboratorio di Sensori e Microsistemi (SMS)

dell’Università degli Studi di Pavia. L’attività si è svolta all’interno del Programma di

ricerca di Rilevante Interesse Nazionale (PRIN) 20085AJSEB intitolato “Nuova metodologia per la rivelazione di gas basata su una griglia bidimensionale di microsensori

interconnessi”. L’attività è finanziata dal Ministero dell’Istruzione, dell’Università e della

Ricerca della Repubblica Italiana.

I sensori per la rivelazione di gas sono ampiamente utilizzati in diverse applicazioni,

ad esempio per il monitoraggio della qualità dell’aria o il controllo di processi industriali.

Recenti direttive del Parlamento Europeo, volte alla protezione della salute umana, mirano

a collocare un maggior numero di punti di campionamento sul territorio per una migliore

valutazione della qualità dell’aria e prevedono anche il monitoraggio delle aree rurali per

la protezione della vegetazione e degli ecosistemi naturali [1]. Queste sono alcune delle

ragioni per cui è divenuto molto importante lo sviluppo di sistemi per il rilevamento di

gas caratterizzati da dimensioni contenute, consumi ridotti, un’alta efficienza e un basso

costo di produzione. Per raggiungere questi obiettivi, è possibile adottare soluzioni tecnologiche tipiche della fabbricazione dei circuiti integrati. Tale scelta progettuale permette

la miniaturizzazione dei sensori e l’abbattimento dei costi di produzione.

I microsistemi per il rilevamento di gas, oggetto di continuo sviluppo da parte dei ricercatori, sono costituiti principalmente da tre componenti: una serie di sensori di gas, un

circuito elettronico di lettura e un elaboratore digitale delle misure acquisite. L’innovazione di questo progetto consiste nell’utilizzo di una matrice di microsensori interconnessi,

soluzione mai adottata prima nel campo dei rivelatori di gas.

Per semplificare il futuro utilizzo del microsistema in sistemi embedded, si è deciso di

implementare al suo interno un’interfaccia seriale con protocollo I2 C , attraverso la quale

poter leggere e programmare il circuito di controllo del sensore. Il progetto di tesi ha

avuto come obiettivo la realizzazione della suddetta interfaccia seriale.

Nella presente tesi si andranno ad esporre le fasi che hanno caratterizzato il conseguimento dei risultati richiesti dal progetto. Lo scritto è cosı̀ strutturato:

• Il Capitolo 1 è dedicato alla descrizione dei componenti del microsistema. In particolare, viene approfondita la struttura del circuito d’interfaccia della matrice di

sensori. Il circuito è in sviluppo nel laboratorio SMS dell’Università di Pavia.

Claudio De Berti

9

INTRODUZIONE

• Il Capitolo 2 è dedicato all’illustrazione dei linguaggi di descrizione hardware che

sono stati adottati nella realizzazione del progetto di tesi.

• Nel Capitolo 3, il primo paragrafo è dedicato allo studio del protocollo I2 C. Nel secondo paragrafo vengono definiti i registri ideati per leggere e controllare il sistema.

Nel terzo paragrafo viene illustrato il lavoro svolto per la descrizione comportamentale dell’interfaccia seriale.

• La prima sezione del Capitolo 4 è dedicata alla sintesi in standard cells della descrizione hardware programmata. La seconda parte del capito è dedicata alla realizzazione del layout del circuito ottenuto dalla sintesi.

• Il Capitolo 5 è dedicato alle simulazioni dell’interfaccia progettata in ambiente

Cadence Virtuoso.

10

Claudio De Berti

Capitolo 1

Descrizione del Sistema

Il progetto PRIN 20085AJSEB, finanziato dal Governo Italiano, prevede lo sviluppo di

una nuova metodologia a basso costo per la rivelazione di gas basata su un microsistema

integrato. Esso è composto da una matrice di sensori di gas, da un circuito integrato

di lettura della matrice, che include anche il circuito di controllo della temperatura dei

sensori, e infine da algoritmi di elaborazione dei dati raccolti. Sono tre le unità di ricerca

a partecipare al progetto: lo studio e la realizzazione della matrice di sensori di gas è stato

assegnato al CNR di Lecce; l’Università degli Studi di Pavia si occupa della progettazione

dell’interfaccia di lettura per la matrice, nonché del circuito di controllo della temperatura;

all’Università degli Studi di Roma “Tor Vergata” spetta la programmazione di algoritmi

per l’elaborazione dei dati acquisiti.

1.1

Matrice di sensori

In natura sono diffuse strutture ricettive in cui selettività e sensibilità elevate sono ottenute

con l’interconnessione di elementi di per sé poco sensibili o selettivi. Ad esempio, il senso del gusto nell’essere umano ha come recettori funzionali migliaia di gemme gustative;

ognuna di queste è in grado di distinguere una delle cinque sensazioni gustative [2]. Di

conseguenza, il senso del gusto dipende dalla percezione sinergica di cinque gusti fondamentali. Una matrice di sensori di gas interconnessi può quindi considerarsi un dispositivo

“bio-ispirato”.

L’unità di Lecce ha sviluppato una matrice 5 × 5, per un totale di 25 sensori. La

schematizzazione della matrice è rappresentata in Figura 1.1. I sensori di gas sono di

tipo resistivo e vengono realizzati con micromembrane in silicio; su ogni membrana viene deposto un materiale sensibile a particolari concentrazioni di gas che viene contattato

tramite quattro elettrodi. Ogni sensore è dotato di un riscaldatore, realizzato con una resistenza in platino (indicata con la lettera H nello schema), ed è dotato di un sensore di

temperatura, anch’esso realizzato con una resistenza in platino (indicata con la lettera T

nello schema). Gli elettrodi di ciascuna micromembrana sono direttamente connessi agli

elettrodi delle micromembrane adiacenti, andando cosı̀ a creare la struttura matriciale. Le

micromembrane posizionate ai bordi della griglia presentano uno o due elettrodi connessi

Claudio De Berti

11

CAPITOLO 1. DESCRIZIONE DEL SISTEMA

Figura 1.1: Schema semplificato della griglia di sensori di gas

direttamente ai terminali del dispositivo. Ciascuna riga della matrice presenta le resistenze del riscaldatore e del sensore di temperatura delle cinque micromembrane connesse

in serie, permettendo cosı̀ di controllare indipendentemente la temperatura di lavoro di

ciascuna riga. Il dispositivo è quindi in grado di rispondere in modo diverso ai gas da

rilevare non solo per l’utilizzo di differenti strati sensibili applicati ai sensori, ma anche

grazie al funzionamento a temperature differenti.

È possibile utilizzare come materiale sensibile, da deporre su una micromembrana,

sia un composto inorganico, sia un composto organico. Per quel che riguarda i materiali

inorganici si adoperano i seguenti ossidi metallici:

• Ossido di stagno (SnO2 );

• Ossido di stagno drogato (SnO2 /X);

• Ossido di indio (In3 O3 );

• Ossido di tungsteno (WO3 ).

Gli ossidi di metallo vengono sintetizzati mediante opportuni metodi chimici che consentono di ottenere nanopolveri del materiale. Queste polveri vengono utilizzate nella

preparazione delle paste serigrafiche che in seguito sono deposte per drop-coating sulle

aree sensibili della matrice. Il processo di deposizione viene concluso sottoponendo il

dispositivo a trattamenti termici.

Per quel che riguarda i materiali organici si possono prendere in considerazione:

• Polimeri conduttori;

12

Claudio De Berti

1.2. INTERFACCIA DI CONTROLLO E LETTURA DEI SENSORI

Figura 1.2: Schema a blocchi del circuito di lettura e di controllo della temperatura

• Materiali molecolari basati su ftalocianine e porfirine.

La deposizione dei materiali organici avviene con tecniche standard come lo spray casting

o con tecniche più avanzate basate su ink-jet. Lo studio della deposizione dei materiali

organici è affinato all’unità di ricerca di Roma.

1.2

Interfaccia di controllo e lettura dei sensori

Lo schema a blocchi del circuito integrato di controllo e lettura per la matrice, realizzato

dall’unità di Pavia, è mostrato in Figura 1.2. Il blocco digitale (Digital Control) è finalizzato al controllo della sequenza di misure; in particolare agisce sui multiplexer (Mux)

che permettono di selezionare i terminali della matrice da utilizzare per ogni singola misura. I multiplexer connettono i terminali selezionati del dispositivo al circuito di lettura

vero e proprio. All’interno del sistema è presente anche un blocco per il controllo della

temperatura, effettuato separatamente per ogni riga della matrice di sensori.

1.2.1

Circuito per la lettura dei sensori

I sensori di gas considerati si comportano elettricamente come resistenze di valore variabile con la concentrazione del misurando [3]. Il circuito integrato di interfaccia per

sensori deve essere in grado di leggere il valore di resistenza tra qualunque coppia di

terminali della griglia. Questa resistenza è data dalla combinazione delle resistenze dei

sensori interconnessi e il suo valore dipende dal misurando e dalla coppia di terminali

scelti per la misura, in quanto la resistenza presente tra ciascuna coppia di terminali è data

da una diversa combinazione di sensori con diversi strati sensibili e funzionanti a temperatura diversa. La matrice presenta in tutto 20 terminali, quindi le coppie di terminali

che si ottengono sono 20 × 19 = 380; siccome la resistenza equivalente tra due terminali

dipende anche dal verso di misurazione, in tutto le resistenze da considerare sono 380.

Ne deriva che per ogni composto chimico da rilevare si può contare su un insieme di 380

Claudio De Berti

13

CAPITOLO 1. DESCRIZIONE DEL SISTEMA

Figura 1.3: Schematico semplificato del circuito di misura di resistenza

misure individuali. Ogni singolo valore di resistenza (R sens ) è dato dalla combinazione di

tre variabili indipendenti: la prima è la resistenza di base Rbl che dipende dalla tecnologia

di fabbricazione utilizzata; la seconda è la variazione della resistenza di base ∆Rbl che è in

funzione sia della temperatura di utilizzo, sia delle alterazioni del dispositivo dovute all’invecchiamento o al processo produttivo; la terza è la resistenza ∆Rgas che è in funzione

della concentrazione di gas sotto esame ed ha una dinamica di un paio di decadi. Quindi

la i-esimia resistenza tra due terminali, con i = [0 ÷ 379], vale:

R sens,i = Rbl + ∆Rbl + ∆Rgas

(1.1)

La resistenza equivalente R sens che si ottiene dalla (1.1) ha un range dinamico estremamente elevato, con valori che possono variare da 1 kΩ a 1 GΩ. Questo implica che il

circuito di lettura deve avere una dinamica operativa di almeno 5 decadi.

L’unità di Pavia ha progettato un circuito di interfaccia basato su un oscillatore controllato in corrente, il cui periodo di oscillazione dipende in maniera direttamente proporzionale dalla resistenza del sensore [4]. L’architettura, mostrata in Figura 1.3 nel caso di

un singolo sensore, presenta una tensione costante Vre f applicata alla resistenza R sens in

modo da garantire il corretto funzionamento del dispositivo. La corrente che si ottiene

(I sens = Vre f /R sens ) viene specchiata e in seguito iniettata, con verso positivo o negativo,

in un integratore sigle-ended. L’uscita dell’integratore è mantenuta in un intervallo di

tensione ∆V = VH − VL grazie ai due comparatori. Essa viene quindi squadrata tramite dei flip-flop set-reset dotati di due uscite, l’una l’inverso dell’altra. Le forme d’onda

quadra ottenute (CT RH e CT RL ) pilotano gli interruttori dello specchio che determinano il verso della corrente applicata all’integratore. Come risultato si ottiene, all’uscita

dell’integratore, un’onda triangolare con periodo dato da:

T=

14

2 · ∆V · R sens

Vre f

(1.2)

Claudio De Berti

1.2. INTERFACCIA DI CONTROLLO E LETTURA DEI SENSORI

I componenti del circuito sono stati dimensionati per ottenere il miglior trade-off tra

velocità di conversione e consumo di potenza; ne risulta una frequenza di oscillazione

dell’onda compresa tra 2.5 MHz e 2.5 Hz.

La conversione in digitale del valore di R sens si ottiene dal rapporto trapl’uscita di un

fmin · fmax =

contatore di riferimento, operante ad una frequenza intermedia fmind =

2.5 kHz, e l’uscita di un contatore operante alla frequenza di oscillazione del circuito

[5]. La conversione termina quando il più lento dei due contatori giunge a un valore

N ∗ assegnato, sufficiente all’ottenimento dell’accuratezza necessaria (con N ∗ = 256 si

ottiene una precisione equivalente a 8 bit per decade). Il valore di resistenza misurato

Rmeas è quindi dato da:

Nre f

+β

(1.3)

Rmeas = α · Rmid ·

Nosc

Nella (1.3) Nre f indica il valore dell’uscita del contatore di riferimento a fine conversione, mentre Nosc indica il valore dell’uscita del contatore pilotato dall’oscillatore, sempre

calcolato a fine conversione. La resistenza Rmid è il valore centrale della scala logaritmica, mentre α e β rappresentano il guadagno e l’offset del circuito di interfaccia. Non è

necessario compensare questi due coefficienti perché non alterano la linearità della conversione; la conoscenza esatta del valore della resistenza equivalente è superflua al fine di

valutare la concentrazione di gas. Il minimo numero di bit necessario per ogni contatore

è dato da:

!

!

1GΩ

∗ Rmax

≈ log2 256 ·

> 18

(1.4)

Nbit > log2 N ·

Rmid

1MΩ

Di conseguenza, ogni misura effettuata viene espressa da 19 bit, ottenendo una precisione

intorno al 0.5%. Il tempo massimo di conversione, per ogni singolo sensore, vale 256 ·

T max ≈ 102.4 s, quindi la conversione completa della matrice, ottenuta effettuando 380

singole conversioni, richiederebbe un tempo inaccettabile (più di 10 ore). Per ovviare a

questo problema, il circuito è dotato di un sistema per ridurre di un fattore 100 il tempo

di conversione dei valori di resistenza più elevati; in pratica il circuito esegue una prima

conversione a bassa risoluzione che impiega al massimo 12.8 ms (corrispondenti a 32

periodi del clock di riferimento). Se il risultato della conversione rapida satura verso valori

alti, la capacità dell’integratore viene diminuita, andando cosı̀ ad aumentare la frequenza

di oscillazione.

Il circuito è stato progettato in tecnologia CMOS da 0.35 µm con una tensione di alimentazione nominale di 3.3 V. L’utilizzo di una tecnologia diversa da quella impiegata

per la realizzazione della matrice di sensori permette di abbattere i costi di produzione e di aumentare l’efficienza del sistema. Questo soluzione è nota come “approccio

micromodulare”.

1.2.2

Interfaccia seriale

L’obiettivo di questo lavoro di tesi è la progettazione e simulazione di un’interfaccia seriale I2 C da inserire all’interno del sistema appena descritto (Figura 1.4). La lettura e il

controllo del sensore dall’esterno avverrebbero quindi secondo le regole del protocollo

Claudio De Berti

15

CAPITOLO 1. DESCRIZIONE DEL SISTEMA

MATRICE DI

SENSORI

CIRCUITO DI

CONTROLLO

SDA

REGISTRI

I2C

SCL

Figura 1.4: Schema a blocchi del microsistema con interfaccia I2 C

I2 C, da anni utilizzato come standard di comunicazione in molti microsensori commerciali [6]; esso viene inoltre utilizzato spesso per la configurazione e il controllo di microsistemi integrati di elevata complessità [7]. L’adozione di un protocollo seriale consente

la riduzione dei costi di produzione legati al packaging, infatti l’interfaccia I2 C utilizza

solo due pin oltre alle alimentazioni. Alla progettazione dell’interfaccia seriale è associata anche la realizzazione di un set di registri, nei quali vengono raggruppati tutti i segnali

necessari al funzionamento e alla programmazione del circuito di controllo e lettura della

matrice di sensori.

16

Claudio De Berti

Capitolo 2

Linguaggi HDL

Alla fine degli anni ’70 i circuiti integrati digitali iniziarono ad avere un livello di complessità tale da evidenziare l’inadeguatezza degli strumenti di progetto a livello di porte

logiche (gate-level). Questo fatto diede inizio agli studi di linguaggi descrittivi astratti,

in grado di aumentare l’efficienza nella progettazione di sistemi digitali complessi. Gli

HDL (Hardware Description Languages) sono linguaggi usati per descrivere un sistema

in forma testuale. Rispetto al disegno schematico, gli HDL permettono di utilizzare livelli

di astrazione più alti, estremamente utili nei progetti complessi.

Il primo HDL è stato PALASM (PAL ASseMbler) che serviva a specificare reti logiche per dispositivi programmabili tipo PAL. Un linguaggio simile è ABEL (Advanced

Boolean Equation Language). Questi linguaggi permettono di descrivere il sistema attraverso equazioni logiche, tabelle della verità e diagrammi a stati (in forma testuale).

Tra gli HDL, quelli considerati di alto livello, principalmente VHDL e Verilog, permettono anche rappresentazioni astratte del sistema, e descrizioni algoritmiche simili a quelle

dei linguaggi di programmazione software. Sia VHDL che Verilog sono linguaggi di

descrizione dell’hardware adatti a modellizzare sistemi digitali sia per scopi di sola simulazione, che per scopi di sintesi e successiva implementazione su dispositivi reali. La loro

principale caratteristica è l’indipendenza dalla tecnologia, ovvero la capacità di descrivere qualsiasi sistema digitale senza vincolare la descrizione ad una specifica tecnologia di

integrazione. Questa è la base per costruire codice portabile e riutilizzabile permettendo

una progettazione più efficiente.

2.1

VHDL

Il linguaggio VHDL viene utilizzato per la descrizione di sistemi hardware digitali. È

simile ai linguaggi di programmazione per la costruzione di programmi software, ma è

dotato di caratteristiche particolari, necessarie alla diversa natura dell’oggetto da descrivere. La prima versione standard del VHDL fu definita nel 1987 da IEEE (Institute of

Electrical and Electronics Engineers) con il nome IEEE-1076-1987. Nel 1993 è stata aggiornata in IEEE-1076-1993. Le due versioni principali del linguaggio definite da questi

standard sono pubblicate nel Language Reference Manual (LRM).

Claudio De Berti

17

CAPITOLO 2. LINGUAGGI HDL

Il principio su cui si basa il VHDL è che un sistema hardware di qualsiasi livello

di complessità può essere schematizzato come un dispositivo che riceve degli ingressi

(input), li elabora secondo precise operazioni e produce delle uscite (output) legate alle

operazioni svolte. Inoltre, ogni sistema può essere scomposto in più sottosistemi, ognuno

schematizzabile nel modo precedentemente descritto.

In VHDL il modello di un sottosistema è detto design entity ed è costituito da due

parti: una entity (che descrive l’interfaccia esterna) ed una architecture (che descrive il

funzionamento interno). Per descrivere un sistema si devono, quindi, definire:

• la sua interfaccia esterna, ovvero gli ingressi e le uscite che mettono in comunicazioni l’entity con l’esterno;

• il suo funzionamento interno, ovvero le operazioni che l’entity deve svolgere sui

segnali di ingresso per generare i segnali d’uscita.

Nella descrizione hanno un ruolo fondamentale i segnali che mettono in comunicazione

parti diverse del sistema. Le porte sono segnali particolari poiché permettono ai dati

l’ingresso e l’uscita dall’entity. Package e library sono parole chiave che permettono di

creare dei contenitori di porzioni di codice. Questa tecnica è usata sia per isolare porzioni

di codice dal resto della descrizione sia per riutilizzarle in più ambiti.

2.1.1

Livelli di astrazione

Una descrizione più astratta si limita ad indicare cosa debba fare il sistema senza specificare come, ed è quindi più vicina alle esigenze descrittive del progettista. Una descrizione

meno astratta invece contiene dettagli implementativi e specifica come è effettivamente

costituito il sistema. Il VHDL supporta tre livelli di astrazione:

• il livello di astrazione più basso è la Descrizione Strutturale: il sistema viene rappresentato direttamente nella sua struttura come rete di porte logiche. Si indicano

i componenti del sistema e le interconnessioni tra di essi. Questa descrizione è

l’equivalente testuale di un disegno schematico;

• la Descrizione Funzionale o Comportamentale (behavioural) è il livello di astrazione più alto. Il progettista tramite il linguaggio VHDL definisce come il dispositivo

debba agire. Nel definire cosa il sistema debba fare, il progettista utilizza descrizioni algoritmiche tramite istruzioni simili a quelle dei linguaggi di programmazione

software;

• ad un livello intermedio di astrazione troviamo la Descrizione Dataflow, che contiene una rappresentazione del flusso dei dati: per mezzo di equazioni logiche si

descrive l’effetto sui segnali in uscita di un flusso di segnali in ingresso.

Efficacia ed efficienza sono due aspetti contrapposti da valutare per la scelta del livello

di astrazione da utilizzare. L’efficacia rappresenta esigenza che il modello possa essere

18

Claudio De Berti

2.2. VERILOG

interpretato correttamente dallo strumento di sviluppo in fase di sintesi, mentre l’efficienza rappresenta l’esigenza del progettista di poter utilizzare un linguaggio descrittivo il più

possibile vicino alla propria visione del sistema da modellizzare.

Nella fase di programmazione le istruzioni vengono spesso scritte in sequenza, ma, a

differenza di quanto accade per i linguaggi di programmazione software, in VHDL questo

non implica che esse agiranno in sequenza. I concetti di concorrenzialità e sequenzialità

vengono in aiuto: più elementi si definiscono concorrenti quando la loro esecuzione è

parallela o contemporanea, si dicono invece sequenziali se la loro esecuzione avviene un

elemento dopo l’altro, ossia in serie. I processi raggruppano un insieme di istruzioni e

sono concorrenti fra loro; il loro scopo è quello di contenere istruzioni sequenziali per la

descrizione del sistema.

2.2

Verilog

Il linguaggio Verilog attualmente si spartisce con il VHDL il mercato dei linguaggi destinati alla progettazione e simulazione digitale.

Lo sviluppo del linguaggio Verilog venne avviato nel 1984 nei laboratori della Gateway Design Automation Inc. Venne ideato ispirandosi alle funzionalità dei linguaggi

HDL al tempo più diffusi e alle caratteristiche di linguaggi di programmazione tradizionali, come il C. Essendo un linguaggio proprietario, il Verilog non venne subito standardizzato e subı̀ diverse modifiche in occasione delle numerose revisioni effettuate fino alla

fine degli anni ’80. Nel 1990 Cadence Design System, tutt’oggi il principale produttore

di software per la progettazione hardware, acquisı̀ la Gateway Design Automation Inc.,

divenendo cosı̀ proprietaria del linguaggio Verilog. Cadence riconobbe che se il Verilog

fosse rimasto un linguaggio proprietario chiuso, le altre aziende di progettazione hardware

avrebbero utilizzato un linguaggio più flessibile, come il VHDL. Di conseguenza Cadence

creò l’Open Verilog International (OVI) e nel 1991 fornı̀ la documentazione del Verilog,

evento che sancı̀ “l’apertura” del linguaggio di descrizione hardware. Il linguaggio venne

poi standardizzato nel 1995 con il nome IEEE-1364.

Il linguaggio verilog è in grado di descrivere un sistema digitale come un insieme di

moduli (modules). Ogni modulo è dotato di un’interfaccia con altri moduli in base alla

descrizione del suo contenuto. Un modulo rappresenta un’unità logica che può essere

descritta sia specificando la sua struttura logica interna, sia descrivendo il suo comportamento logico con un linguaggio più simile alla programmazione informatica. Nel primo

caso, la descrizione permette la sintesi a livello di gate del sistema digitale, nel secondo caso ci si concentra sul comportamento che il sistema deve avere [8]. I moduli sono

interconnessi con delle nets che ne permettono la comunicazione.

2.3

Macchina a stati finiti

Se il sistema da descrivere ha una certa complessità, l’utilizzo di macchine a stati finiti (FSM) permette di semplificare dal punto di vista logico la programmazione. Una

Claudio De Berti

19

CAPITOLO 2. LINGUAGGI HDL

et

res

START

X=go_mid

X=go_start

MIDDLE

X=go_stop

STOP

Figura 2.1: Diagramma a bolle di una FSM

macchina a stati finiti consiste in un insieme di stati e di direzioni di evoluzione degli stati. Il funzionamento di questi sistemi, sensibili ad un segnale di temporizzazione

(clock ), si basa sulla valutazione degli ingressi che determinano l’evoluzione degli stati

della macchina.

Esistono due tipologie di FSM [9]: la macchina di Moore e la macchina di Mealy.

Nella macchina di Moore ad ogni istante il valore delle uscite dipende esclusivamente

dallo stato attuale. Nella macchina di Mealy ad ogni istante il valore delle uscite dipende sia dallo stato attuale che dall’attuale valore degli ingressi. Durante la permanenza

in uno stato, una variazione dell’ingresso di una macchina di Mealy può ripercuotersi

immediatamente sull’uscita.

La macchina a stati viene a formarsi dall’unione di un processo sequenziale e di uno o

più combinatori; il processo combinatorio ha il compito di valutare i segnali in ingresso e

in base a questi gestire il segnale che indica il prossimo stato (stato futuro) della macchina;

il processo sequenziale dovrà occuparsi di far commutare lo stato presente nello stato

futuro, permettendo l’avanzamento di stato.

2.3.1

FSM adottata

La struttura della macchina a stati utilizzata in questo lavoro di tesi viene definita come

One ‘State’ Process [10]. Il codice VHDL basilare di una macchina di tale tipologia è

riportato qui di seguito:

1

2

3

4

20

FSM FF : p r o c e s s (CLK, RESET )

begin

i f RESET= ’1 ’ t h e n

STATE <= START ;

Claudio De Berti

2.3. MACCHINA A STATI FINITI

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

e l s i f CLK’ e v e n t and CLK= ’1 ’ t h e n

c a s e STATE i s

when START

=> i f X=GO MID t h e n

STATE <= MIDDLE ;

end i f ;

when MIDDLE => i f X=GO STOP t h e n

STATE <= STOP ;

end i f ;

when STOP

=> i f X=GO START t h e n

STATE <= START ;

end i f ;

when o t h e r s => STATE <= START ;

end c a s e ;

end i f ;

end p r o c e s s FSM FF ;

Il comportamento del codice è mostrato nel diagramma a bolle di Figura 2.1: se la

condizione associata alla freccia è vera in corrispondenza di un fronte positivo di clock,

la macchina cambia di stato. Il comportamento è quindi sincrono con il clock. Solo il reset agisce in modo asincrono e, se attivo, riporta la macchina allo stato iniziale

immediatamente.

Claudio De Berti

21

Capitolo 3

Interfaccia seriale

La fase iniziale del progetto di tesi è stata caratterizzata dalla programmazione in VHDL

dell’interfaccia seriale con cui il sensore sarà in grado di fornire informazioni verso l’esterno. Nell’interfaccia progettata non solo si rispettano le regole del protocollo I2 C, ma

si sono adottate soluzioni comportamentali specifiche per il corretto controllo del dispositivo, che verranno esposte in dettaglio nei paragrafi seguenti. Inoltre, in questa fase di

progettazione, si sono definiti, in numero e in tipologia, i registri necessari al controllo e

alla lettura del circuito d’interfaccia della matrice.

3.1

Protocollo I2C

Il sistema di comunicazione seriale I2 C, acronimo di Inter Integrated Circuit, è stato sviluppato dalla Philips come interfaccia seriale utilizzata nei propri circuiti integrati. Il

rilascio della prima versione del protocollo risale al 1992. Nel corso degli anni essa ha

subito diversi aggiornamenti e dall’Ottobre del 2006 può essere usato liberamente.

L’I2 C è un sistema di comunicazione seriale bifiliare che permette l’interconnessione

con più dispositivi, quindi si può definire un bus di comunicazione. Trattandosi di un

protocollo seriale, ha il vantaggio di utilizzare solo due linee, ovvero occupa solo due

pin del package, mentre ha come svantaggio una limitata velocità di comunicazione. La

velocità di trasferimento dati previsto dallo Standard-Mode, utilizzato in questo progetto,

ha un bitrate massimo di 100 Kbit/s. Le linee seriali sono:

• SDA (Serial Data Line) che viene utilizzata per la trasmissione dei dati;

• SCL (Serial Clock Line) che viene utilizzata per il segnale di clock di trasmissione.

La trasmissione del clock rende il sistema un bus sincrono.

Entrambe le linee devono essere connesse all’alimentazione tramite resistenze di pullup [11]. Un bus I2 C è composto da almeno un master ed uno slave; un dispositivo di tipo

master emette il segnale di clock, mentre un dispositivo di tipo slave si sincronizza sul

segnale di clock senza poterlo controllare. Ogni dispositivo collegato al bus è identificato

da un indirizzo univoco a 7 bit.

Claudio De Berti

23

CAPITOLO 3. INTERFACCIA SERIALE

Figura 3.1: Condizione di Start e condizione di Stop

Figura 3.2: Trasferimento di un bit

L’interfaccia I2 C realizzata in questa tesi è di tipo slave, dato che si vorrà leggere e

controllare il sensore tramite un dispositivo master, soluzione universalmente adottata per

tutti i sensori che utilizzano tale protocollo.

3.1.1

Regole di comunicazione

Il protocollo prevede una condizione di inizio trasmissione ed una di fine della stessa

(Figura 3.1):

• condizione di Start: con SCL alto, SDA passa dallo stato alto a quello basso;

• condizione di Stop: con SCL alto, SDA passa dallo stato basso a quello alto.

Un bit, per essere valido, deve essere tale da mantenere la linea SDA stabile per l’intera

durata del periodo positivo di SCL (Figura 3.2). I dati sulle linee SDA e SCL vengono

trasmessi un byte alla volta Ad ogni byte trasmesso segue sul bus una conferma di avvenuta ricezione da parte del dispositivo interessato; in pratica vengono trasmessi otto bit

di dati, mentre il nono ha la funzione di acknowledgement (Figura 3.3). Durante il “bit

di acknowledge”, il trasmittente lascia la linea SDA alta ed il ricevente l’abbassa in caso

di avvenuta ricezione o la lascia alta in caso contrario. Un mancato acknowledge può

avvenire, quindi, nel caso in cui il byte immediatamente precedente non sia stato ricevuto

correttamente: questo può essere un byte di dati effettivo, l’indirizzo di un registro in cui

scrivere o leggere il dato, oppure l’indirizzo stesso del dispositivo. Nel caso di mancato

acknowledgement, è necessario ripetere la trasmissione.

24

Claudio De Berti

3.1. PROTOCOLLO I2 C

Figura 3.3: Invio di un byte sul bus

Sequenze di lettura e scrittura dei registri

L’indirizzo slave a 7 bit viene completato a 8 bit con l’aggiunta del bit di lettura/scrittura

che va ad occupare la posizione meno significativa nel byte:

• il bit “0” determina la scrittura (W) da parte del master sullo slave;

• il bit “1” determina la lettura (R) da parte del master dallo slave.

L’indirizzo dello slave con il bit di scrittura viene inviato dopo la condizione di Start (ST).

Se la ricezione avviene con successo, lo slave invia il bit di acknowledgement (SAK). Si

può quindi passare all’invio dell’indirizzo del registro (SUB) in cui si vuole andare a

scrivere/leggere. I registri, di cui si parlerà in dettaglio più avanti, hanno indirizzi a 6 bit

e vengono completati a 8 bit con l’aggiunta di due bit più significativi (MSB):

• se i due bit MSB sono “00” si potrà leggere/scrivere solo nel registro associato

all’indirizzo;

• se i due bit MSB sono “10”, l’indirizzo verrà automaticamente incrementato permettendo di leggere/scrivere in più registri consecutivi.

Per poter leggere il contenuto di un registro è necessario effettuare, dopo l’invio del

suo indirizzo, una condizione di Start ripetuta (SR): con SCL alto, SDA passa dallo

stato alto a quello basso. A questa condizione segue l’invio dell’indirizzo dello slave con

il bit di lettura (R). In lettura è il master a inviare il bit di acknowledgement (MAK)

in risposta ad ogni byte ricevuto. Per fermare l’invio di byte da parte dello slave, il

master non effettua l’invio del bit di acknowledgement (NMAK). Sia la lettura che la

scrittura terminano con la condizione di Stop (SP). Le procedure appena descritte sono

schematizzate nella Figura 3.4 per la scrittura e nella Figura 3.5 per la lettura.

3.1.2

Temporizzazioni

L’interfaccia I2 C deve rispettare i valori di temporizzazione imposti dal protocollo. Per

la realizzazione del progetto si è scelto di adottare il modello standard del bus di comunicazione, dato che per la lettura e il controllo del sensore la velocità offerta da tale

Claudio De Berti

25

CAPITOLO 3. INTERFACCIA SERIALE

Master

Slave

ST

Master

Slave

ST

SAD + W

SUB

DATA

SAK

SP

SAK

SAD + W

SUB

SAK

DATA

SAK

DATA

SAK

SAK

SP

SAK

Figura 3.4: Sequenza di scrittura di un singolo registro (sopra) e di registri con indirizzi

consecutivi (sotto)

Master

Slave

ST

Master

Slave

ST

SAD + W

SUB

SAK

SAD + W

SR

SUB

SAK

SAD + R

SAK

SR

SAK

NMAK

SAK

SP

DATA

SAD + R

MAK

SAK

DATA

NMAK

SP

DATA

Figura 3.5: Sequenza di lettura di un singolo registro (sopra) e di registri con indirizzi

consecutivi (sotto)

soluzione è più che sufficiente. In fase progettuale è necessario adottare soluzioni tali da

poter garantire il rispetto totale delle regole di temporizzazione imposte dal protocollo; in

particolare, durante le simulazioni, si andrà a valutare il comportamento dell’interfaccia

in presenza di segnali caratterizzati da temporizzazioni corrispondenti al limite teorico

di velocità imposto dal protocollo. Le specifiche di temporizzazione sono riportate nella

Tabella 3.1 e fanno riferimento alla Figura 3.6.

3.2

Registri

Per poter interagire con il circuito d’interfaccia del sensore, si è creato un set di registri

accessibile dall’esterno tramite il bus I2 C. Un registro di un dispositivo slave può essere di

sola lettura (r), di sola scrittura (w), oppure di lettura/scrittura (rw). Per il controllo dell’interfaccia del sensore è risultato necessario l’utilizzo di 10 registri, mentre per fornire

le misure di gas e temperatura ne sono stati utilizzati altri 5.

Ai registri sono stati assegnati indirizzi a 6 bit, anche se per la loro identificazione

ne basterebbero 4: nell’ipotesi di sviluppi futuri, si è scelto di poter avere la possibilità

di aumentare il numero di registri senza apportare radicali modifiche all’interfaccia I2 C.

L’elenco dei registri è mostrato nella Tabella 3.2. Gli indirizzi dei registri di controllo

hanno valori consecutivi, come pure gli indirizzi dei registri di lettura: questa caratteristica

permette l’utilizzo delle sequenze di lettura o scrittura di più byte di dati mostrate nel

paragrafo precedente.

26

Claudio De Berti

3.2. REGISTRI

REPEATED

START

START

tsu(SR)

tw(SP:SR)

SDA

tf(SDA)

tsu(SDA)

tr(SDA)

START

th(SDA)

tsu(SP)

STOP

SCL

th(ST)

tw(SCLL)

tw(SCLH)

tr(SCL)

tf(SCL)

Figura 3.6: Temporizzazioni del protocollo

Symbol

f(SCL)

Parameter

SCL clock frequency

I2C standard mode

Min

Max

0

100

tw(SCLL)

SCL clock low time

4.7

tw(SCLH)

SCL clock high time

4.0

tsu(SDA)

SDA setup time

250

th(SDA)

SDA data hold time

0

ns

3.45

SDA and SCL rise time

1000

tf(SDA) tf(SCL)

SDA and SCL fall time

300

START condition hold time

4

tsu(SR)

Repeated START condition

setup time

4.7

tsu(SP)

STOP condition setup time

4

tw(SP:SR)

Bus free time between STOP

and START condition

KHz

µs

tr(SDA) tr(SCL)

th(ST)

Unit

µs

ns

µs

4.7

Tabella 3.1: Specifiche di temporizzazione dei segnali

Claudio De Berti

27

CAPITOLO 3. INTERFACCIA SERIALE

Nome del registro

Indirizzo del registro

Tipo

Binario

Esadecimale

TEMP_REG1

w

010000

10

TEMP_REG2

w

010001

11

TEMP_REG3

w

010010

12

TEMP_REG4

w

010011

13

TEMP_REG5

w

010100

14

TEMP_REG6

w

010101

15

SET_REG1

w

010110

16

SET_REG2

w

010111

17

CTRL_REG1

rw

011000

18

CTRL_REG2

rw

011001

19

OUT_REG1

r

110000

30

OUT_REG2

r

110001

31

OUT_REG3

r

110010

32

OUT_TEMP1

r

110011

33

OUT_TEMP2

r

110100

34

Tabella 3.2: Set di registri

3.2.1

Registri di controllo

Variando il contenuto dei registri di controllo, è possibile modificare le modalità operative

del circuito d’interfaccia del sensore; in pratica, i bit dei registri andranno a pilotare le

porte logiche dei blocchi digitali di controllo del circuito. All’accensione del dispositivo

i bit devono assumere valori di default. Le funzionalità di ogni singolo registro verranno

esposte di seguito.

Registro SET REG1

GRE

VEL

res

res

res

TM2

TM1

TM0

Tabella 3.3: Bit del registro SET REG1

• GRE: bit che permette di selezionare la modalità di conversione delle misure di gas

effettuate dalla matrice.

1. “0”: modalità di conversione con risoluzione massima;

2. “1”: modalità di conversione grezza, ovvero a bassa risoluzione.

28

Claudio De Berti

3.2. REGISTRI

Il valore di default assegnato al bit GRE è “0”.

• VEL: bit che permette di selezionare la velocità con cui effettuare la conversione

1. “0”: velocità di conversione normale;

2. “1”: conversione in modalità rapida.

Anche per il bit VEL il valore di default è “0”.

• TM0, TM1 e TM3: bit utilizzati per selezionare, pilotando un multiplexer, un

valore di temperatura sui cinque rilevati dal circuito, ognuno corrispondente a una

riga di sensori della matrice. Il valore selezionato viene cosı̀ reso disponibile nei

registri d’uscita dedicati alla temperatura.

1. “001”: temperatura relativa alla prima riga di sensori;

2. “010”: temperatura relativa alla seconda riga di sensori;

3. “011”: temperatura relativa alla terza riga di sensori;

4. “100”: temperatura relativa alla quarta riga di sensori;

5. “101”: temperatura relativa alla quinta riga di sensori.

I tre bit hanno come valore di default “001”.

• I bit res non assumono alcuna funzione. Potranno essere utilizzati in eventuali

sviluppi futuri.

Registro SET REG2

SW7

SW6

SW5

SW4

SW3

SW2

SW1

SW0

Tabella 3.4: Bit del registro SET REG2

Ogni bit del registro SET REG2 può essere utilizzato per pilotare uno switch che

consente di abilitare l’uscita, su pin del package, di tensioni analogiche provenienti dal

circuito d’interfaccia del sensore. Le tensioni che si vorranno avere in uscita verranno

decise nelle fasi finali di progettazione del sistema integrato e serviranno nelle operazione

di test del dispositivo dopo la sua realizzazione.

Registri TEMP REGx

Con i registri TEMP REGx è possibile impostare la temperatura di funzionamento delle cinque serie di riscaldatori della matrice. La temperatura che si vuole ottenere dai

riscaldatori è espressa con 9 bit di risoluzione.

• Bit da TE1 8 a TE1 0: temperatura dei riscaldatori della prima riga di sensori.

Claudio De Berti

29

CAPITOLO 3. INTERFACCIA SERIALE

TEMP_REG1:

res

res

res

TE5_8

TE5_7

TE5_6

TE5_5

TE5_4

TE5_1

TE5_0

TE4_8

TE4_7

TE4_6

TE4_5

TE4_2

TE4_1

TE4_0

TE3_8

TE3_7

TE3_6

TE3_3

TE3_2

TE3_1

TE3_0

TE2_8

TE2_7

TE2_4

TE2_3

TE2_2

TE2_1

TE2_0

TE1_8

TE1_5

TE1_4

TE1_3

TE1_2

TE1_1

TE1_0

TEMP_REG2:

TE5_3

TE5_2

TEMP_REG3:

TE4_4

TE4_3

TEMP_REG4:

TE3_5

TE3_4

TEMP_REG5:

TE2_6

TE2_5

TEMP_REG6:

TE1_7

TE1_6

Tabella 3.5: Bit dei registri TEMP REGx

• Bit da TE2 8 a TE2 0: temperatura dei riscaldatori della seconda riga di sensori.

• Bit da TE3 8 a TE3 0: temperatura dei riscaldatori della terza riga di sensori.

• Bit da TE4 8 a TE4 0: temperatura dei riscaldatori della quarta riga di sensori.

• Bit da TE5 8 a TE5 0: temperatura dei riscaldatori della quinta riga di sensori.

I valori di default verranno assegnati nelle fasi finali di progettazione del microsistema.

Registri CTRL REG1 e CTRL REG2

I registri CTRL REG1 e CTRL REG2 sono gli unici due registri che possono essere sia

scritti che letti.

MC8

MC7

MC6

MC5

MC4

MC3

MC2

RM1

Tabella 3.6: Bit del registro CTRL REG1

MC1

MC0

res

res

res

res

res

RM2

Tabella 3.7: Bit del registro CTRL REG2

30

Claudio De Berti

3.2. REGISTRI

• Bit da MC8 a MC0: il contenuto di questi 9 bit permette di scegliere una tra le

380 misure effettuabili con la matrice di sensori di gas. Il valore scritto nei registri

viene inviato al blocco digitale di controllo del circuito d’interfaccia del sensore; il

blocco, in base al valore ricevuto, andrà a pilotare i multiplexer che consentono la

selezione dei terminali della matrice. Il valore di default di questi bit corrisponde

alla prima misura effettuata in automatico all’accensione del dispositivo.

• Bit RM1 e RM2: questi due bit determinano l’avvio di una nuova procedura di

misurazione di gas:

1. se entrambi sono a “1”, il circuito di interfaccia inizia ad effettuare la misura

selezionata dai bit MC;

2. se entrambi sono a “0”, una nuova misura di concentrazione di gas è disponibile nei registri di lettura.

I due bit sono di default a “1” e vengono abbassati a “0” quando la misura è terminata; una nuova procedura di misura non verrà avviata finché i due bit saranno reimpostati a “1” attraverso la scrittura di entrambi i registri con un’idonea trasmissione

sul bus I2 C.

3.2.2

Registri di lettura

I registri di lettura permettono l’acquisizione dall’esterno di tutte le misure effettuate dal

sistema; il loro contenuto viene letto dal dispositivo master che stabilisce la connessione

I2 C con il sensore.

Registri OUT REG1, OUT REG2 e OUT REG3

OUT_REG1:

CNT

res

res

res

res

GM18

GM17

GM16

GM14

GM13

GM12

GM11

GM10

GM9

GM8

GM6

GM5

GM4

GM3

GM2

GM1

GM0

OUT_REG2:

GM15

OUT_REG3:

GM7

Tabella 3.8: Bit dei registri OUT REGx

• Bit da MC18 a MC0: rappresentano il valore della concentrazione di gas rivelata dal sensore, relativa alla misura effettuata secondo il contenuto dei registri di

controllo.

Claudio De Berti

31

CAPITOLO 3. INTERFACCIA SERIALE

• Bit CNT: la sua lettura permette di conoscere quale dei due contatori è stato utilizzato per determinare il risultato della conversione A/D.

1. “0”: è stato utilizzato il risultato del contatore operante alla frequenza intermedia di riferimento;

2. “1”: è stato utilizzato il risultato del contatore operante alla frequenza di

oscillazione del circuito.

Registri OUT TEMP1 e OUT TEMP2

I registri OUT TEMP1 e OUT TEMP2 offrono in uscita dal sistema la temperatura

di funzionamento della riga di sensori selezionata dai registri di controllo. Il valore è

espresso con una risoluzione di 9 bit (da OT8 a OT0).

OUT_TEMP1:

res

res

res

res

res

OT6

OT5

OT4

OT3

res

res

OT8

OT1

OT0

OUT_TEMP2:

OT7

OT2

Tabella 3.9: Bit dei registri OUT TEMP1 e OUT TEMP2

3.3

Realizzazione dell’interfaccia

L’interfaccia I2 C di tipo slave e la gestione dei registri che si vogliono implementare

nel microsistema integrato sono stati descritti in VHDL. La scrittura dei codici e la loro

simulazione è stata effettuata utilizzando il programma ModelSim della Mentor Graphics.

3.3.1

Sequenze di trasmissione

Prima della scrittura del codice, si è stabilito quali debbano essere le sequenze di trasmissione che un generico dispositivo master dovrà generare per dialogare con il dispositivo

slave che si vuole progettare.

Lettura della misura di default

All’accensione del sistema, viene effettuata in automatico da parte del sensore la misura

selezionata dal valore di default dei registri di controllo. Un dispositivo I2 C master ha due

opzioni:

1. attendere, dall’accessione del sensore, per almeno il tempo massimo necessario al

completamento della conversione del valore di concentrazione di gas e, in seguito,

andare a leggere il contenuto dei registri d’uscita;

32

Claudio De Berti

3.3. REALIZZAZIONE DELL’INTERFACCIA

Master

Slave

ST

SAD + W

SUB

SAK

SR SAD + R

SAK

MAK

SAK

OUT_REG1

MAK

OUT_REG2

NMAK SP

OUT_REG2

Figura 3.7: Sequenza di trasmissione per la lettura dei registri OUT REG

Master

Slave

ST

SAD + W

SUB

SAK

SR

SAD + R

SAK

MAK

SAK

CTRL_REG1

NMAK

SP

CTRL_REG2

Figura 3.8: Sequenza di trasmissione per la lettura dei registri CTRL REG

2. leggere ripetutamente il contenuto dei registri CTRL REG; quando i due bit RM1

e RM2 passano da “1” a “0”, si potrà andare a leggere il contenuto dei registri

d’uscita.

Durante le fasi di misurazione e conversione, la lettura dei registri d’uscita OUT REGx

è interdetta, come anche la scrittura dei registri di controllo. Questo permette di non

acquisire valori di gas che non corrispondono alla misurazione desiderata. La sequenza

di trasmissione che si avrà sul bus I2 C per il primo caso è mostrata nella Figura 3.7. Nel

secondo caso, verrà ripetuta la sequenza della Figura 3.8 fino all’abbassamento dei due

bit; seguirà poi la sequenza mostrata per il primo caso.

Scrittura dei registri di controllo

Completata la prima misura di default, è possibile andare a modificare il contenuto di

tutti i registri di controllo. Condizione necessaria e sufficiente per avviare una nuova

misurazione, è la scrittura dei registri CTRL REG1 e CTRL REG2 (Figura 3.9) che

permette di riportare a “1” i bit RM1 e RM2. La scrittura di registri di controllo con

indirizzi consecutivi ha una sequenza di trasmissione analoga.

Master

Slave

ST

SAD + W

CTRL_REG1

SUB

SAK

SAK

CTRL_REG2

SAK

SP

SAK

Figura 3.9: Sequenza di trasmissione per la scrittura dei registri CTRL REG

Lettura della misura effuttuata

Effettuata la scrittura dei registri di controllo CTRL REG1 e CTRL REG2, una nuova

procedura di misurazione viene avviata da parte dell’interfaccia del sensore. Per la lettura

dei valori ottenuti, si ha una sequenza di trasmissione identica a quella illustrata per la

misura di default.

Claudio De Berti

33

CAPITOLO 3. INTERFACCIA SERIALE

Lettura della temperatura

La lettura dei registri OUT TEMP può essere effettuata in qualsiasi momento dal completamento della misurazione di default. La sequenza di trasmissione sul bus è analoga a

quella della lettura dei registri OUT REG, basta cambiare l’indirizzo del primo registro

in cui leggere (SUB).

3.3.2

Schema a blocchi dell’interfaccia

Le sequenze di trasmissioni sul bus I2 C, descritte nel paragrafo precedente, devono essere

interpretate e rispettate dal dispositivo slave che si vuole andare a programmare. Si è

quindi pensato ad un algoritmo per l’interfaccia che il codice VHDL dovrà descrivere; il

suo schema a blocchi è mostrato in Figura 3.10. Nel disegno si è omesso il comportamento dello slave nel caso di ricezione della sequenza di stop: se si presenta, in qualsiasi

momento, tale condizione sul bus, l’interfaccia deve ritornare nella fase di ‘attesa condizione start’. Inoltre, nella fase in cui si stabilisce se l’indirizzo del registro ricevuto è

corretto, si deve tener conto anche dei permessi di lettura e scrittura dei registri che dipendono dall’esecuzione della conversione della misura di gas: se un dispositivo master non

rispetta le sequenze di trasmissioni descritte precedentemente, lo slave deve interrompere

la trasmissione non inviando l’acknowledge.

3.3.3

Sistema descritto in VHDL

Il sistema digitale è stato descritto con una entity al cui interno sono stati creati quattro

processi paralleli. Tutti i processi utilizzano un clock con frequenza di 1 MHz e sono

dotati di un reset attivo basso. Nella Figura 3.16 viene mostrata l’entity dello slave. Le

porte dell’entity sono le seguenti:

• clock e reset sono segnali in ingresso che verranno generati all’interno del microsistema integrato;

• sda e scl sono le porte per i segnali del bus e verranno direttamente connesse ai pin

del package; il primo è un segnale di tipo inout, mentre scl è solo d’ingresso.

• data ready è una porta connessa al circuito d’interfaccia della matrice e ha in ingresso un segnale che viene alzato quando la conversione della misura di gas è

terminata;

• le porte da 8 bit OUT REGx e OUT TEMPx vengono connesse alla parte digitale

del circuito d’interfaccia per acquisire i valori da inserire negli omonimi registri di

lettura; essi sono segnali in ingresso all’entity;

• le porte da 8 bit TEMP REGx, SET REGx e CTRL REGx vengono anch’esse connesse alla parte digitale del circuito d’interfaccia e i loro segnali corrispondono al

contenuto dei registri di controllo; essi sono segnali in uscita dall’entity.

34

Claudio De Berti

3.3. REALIZZAZIONE DELL’INTERFACCIA

ACCENSIONE SLAVE

ATTESA CONDIZIONE

START

START RILEVATA?

NO

SI

LETTURA INDIRIZZO

SLAVE

INDIRIZZO

CORRETTO?

NO

SI

INVIO SAK

LETTURA INDIRIZZO

REGISTRO

INDIRIZZO

CORRETTO?

NO

SI

INVIO SAK

LETTURA BYTE

NO

NO

MASTER VUOLE

LEGGERE?

ATTESA CONDIZIONE

START

SI

START RILEVATA?

BYTE RICEVUTO?

NO

SI

SI

LETTURA INDIRIZZO

SLAVE

INVIO SAK

INDIRIZZO

CORRETTO?

NO

SI

INVIO SAK

INVIO BYTE

SI

NACK RICEVUTO?

NO

Figura 3.10: Schema a blocchi dell’algoritmo per l’interfaccia

Claudio De Berti

35

CAPITOLO 3. INTERFACCIA SERIALE

Nelle porte da 8 bit, quelle che corrispondono a dei bit res non andranno connesse a

nessun’altra porta. Per la consultazione del codice scritto si rimanda alla lettura dell’appendice A, invece di seguito viene descritto il comportamento di ogni processo.

Processi dell’entity

Il processo rilevatore condizioni (Figura 3.11) ha lo scopo di analizzare l’andamento

temporale dei sagnali SDA e SCL che ha in ingresso; l’analisi fornisce in uscita cinque

segnali:

rilevatore_condizioni

sda

start_cnd

scl

stop_cnd

scl_f

clock

reset

scl_r

sda_d

Figura 3.11: Il processo rilevatore condizioni

1. start cnd: viene alzato per un periodo di clock quando il processo rileva una

condizione di start trasmessa sul bus;

2. stop cnd: iene alzato per un periodo di clock quando il processo rileva una condizione di stop trasmessa sul bus;

3. scl f: segnale tenuto alto per un periodo di clock quando viene rivelato un fronte

negativo del segnale SCL;

4. scl r:segnale tenuto alto per un periodo di clock quando viene rivelato un fronte

positivo del segnale SCL;

5. sda q: fornisce il segnale della linea SDA sincronizzato con i fronti di clock del

sistema.

Il processo registri lettura (Figura 3.12) gestisce e fornisce il contenuto dei registri di

lettura all’interfaccia I2 C. Il segnale register adr, ovvero l’indirizzo espresso su 6 bit di

un registro, seleziona il contenuto del corrispondente registro e lo rende disponibile sul

segnale in uscita byte out.

Il processo registri scrittura (Figura 3.15) consente la scrittura dei registri da parte

dell’interfaccia I2 C. Il segnale byte in contiene il byte ricevuto dal master e viene scritto

36

Claudio De Berti

3.3. REALIZZAZIONE DELL’INTERFACCIA

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

6 bit

registri_lettura

OUT_REG1

OUT_REG2

OUT_REG3

OUT_TEMP1

OUT_TEMP2

byte_out

8 bit

CTRL_REG1

CTRL_REG2

register_adr

clock

reset

8 bit

Figura 3.12: Il processo registri lettura

nel registro selezionato dal segnale register adr. In uscita dal processo si ha il contenuto

dei registri di controllo che all’accensione del dispositivo avranno i valori di default. Il

segnale in uscita mis ended si abbassa quando viene ricevuta la condizione di fine conversione sul segnale data ready e ritorna alto quando viene effettuata la scrittura corretta

dei registri CTRL REG1 e CTRL REG2.

Il processo FSM (Figura 3.13) è il “cuore” dell’entity descritta. È caratterizzato da

un macchina a stati finiti che permette di controllare le fasi di trasmissione sul bus secondo le regole del protocollo I2 C, seguendo la logica mostrata nel diagramma a blocchi

di Figura 3.10. Per regolare le fasi della trasmissione, esso utilizza i segnali provenienti dal processo rilevatore condizioni e il segnale mis ended generato dal processo registri scrittura. In uscita offre l’indirizzo del registro su cui si sta operando e, in caso di

scrittura da parte del master, il byte ricevuto. Per la lettura dei bit trasmessi sul bus esso

utilizza il segnale sda q.

Il blocco logico controllo sda (Figura 3.14) permette il controllo della linea di trasmissione da parte dello slave: si tratta di un buffer tri-state. In pratica lo slave accede

alla linea sda solo quando deve inviare sul bus un livello logico basso attivando il buffer

tri-state [12]. Quando il buffer non è attivo, offre in uscita un valore d’alta impedenza,

consentendo l’utilizzo della linea da parte di un altro dispositivo (in questo caso il master).

3.3.4

Simulazioni

Le simulazioni sono state eseguite utilizzando un Test bench appositamente scritto per il

sistema descritto in VHDL. Il Test bench ha il compito di simulare sia il comportamento

di un dispositivo I2 C master, sia i segnali che proverrebbero dal microsistema integrato.

Claudio De Berti

37

CAPITOLO 3. INTERFACCIA SERIALE

FSM

8 bit

byte_out

register_adr

start_cnd

byte_in

6 bit

8 bit

stop_cnd

scl_f

sda_out

scl_r

sda_ack

sda_d

clock

reset

mis_ended

Figura 3.13: Il processo FSM

controllo_sda

sda_out

sda

scl_ack

Figura 3.14: Buffer linea SDA

registri_scrittura

TEMP_REG1

TEMP_REG2

8 bit

byte_in

TEMP_REG3

TEMP_REG4

6 bit

register_adr

TEMP_REG5

TEMP_REG6

SET_REG1

data_ready

SET_REG2

CTRL_REG1

clock

reset

CTRL_REG2

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

mis_ended

Figura 3.15: Il processo registri scrittura

38

Claudio De Berti

3.3. REALIZZAZIONE DELL’INTERFACCIA

OUT_TEMP2

reset

OUT_TEMP1

byte_out

registri_lettura

OUT_REG1

OUT_REG2

OUT_REG3

OUT_TEMP1

OUT_TEMP2

8 bit

8 bit

FSM

6 bit

8 bit

8 bit

6 bit

sda

mis_ended

CTRL_REG2

CTRL_REG1

SET_REG2

SET_REG1

TEMP_REG6

TEMP_REG5

TEMP_REG4

TEMP_REG3

TEMP_REG2

TEMP_REG1

registri_scrittura

byte_in

register_adr

data_ready

clock

sda_out

byte_in

scl_ack

register_adr

sda_out

controllo_sda

sda_ack

byte_out

data_ready

start_cnd

stop_cnd

scl_f

sda_d

scl_r

clock

mis_ended

reset

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

CTRL_REG1

CTRL_REG2

reset

8 bit

6 bit

clock

register_adr

stop_cnd

start_cnd

rilevatore_condizioni

sda

scl

scl_f

scl_r

sda_d

reset

OUT_REG1

clock

reset

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

8 bit

TEMP_REG1

TEMP_REG2

TEMP_REG3

TEMP_REG4

TEMP_REG5

TEMP_REG6

SET_REG1

SET_REG2

CTRL_REG2

CTRL_REG1

39

Claudio De Berti

sda

scl

clock

OUT_REG3

OUT_REG2

Figura 3.16: Sistema digitale

CAPITOLO 3. INTERFACCIA SERIALE

Per la simulazione delle sequenze di trasmissione del master, è stato realizzato un

apposito Package VHDL che viene richiamato all’inizio del Test bench. Il Package racchiude al suo interno delle procedure che applicano le varie condizioni del protocollo ai

segnali SDA e SCL. In base alla trasmissione che si vuole simulare, si richiamano nel Test

bench le procedure da utilizzare. La soluzione adottata rende flessibile la programmazione del Test bench, permettendo rapide modifiche del codice in funzione alla trasmissione

che si vuole simulare. I codici del Test bench e del Package sono riportati nell’appendice

A.

Simulazioni delle sequenze di trasmissione

In questo paragrafo vengono riportate le simulazioni svolte relative alle “sequenze di

trasmissione”, descritte precedentemente nel capitolo.

La prima simulazione effettuata è relativa alla lettura della misura svolta di default

all’accensione del sensore. Il Test bench è in grado di stampare alcune informazioni utili

alla verifica della simulazione:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

#

#

#

#

#

#

#

#

#

#

#

#

#

#

#

#

#

#

#

#

** Note :

Time :

** Note :

Time :

** Note :

Time :

** Note :

Time :

** Note :

Time :

** Note :

Time :

** Note :

Time :