UNIVERSITÀ DEGLI STUDI DI SIENA

FACOLTÀ DI INGEGNERIA

CORSO DI LAUREA IN INGEGNERIA INFORMATICA

MODULO PROFESSIONALIZZANTE

"TECNOLOGIE PER IL KNOWLEDGE MANAGEMENT"

A.A. 2005/2006

DISPENSE DI

CALCOLATORI ELETTRONICI 1

Hanno collaborato alla stesura delle dispense:

Sara Belloni

Paolo Bennati

Riccardo Brogi

Elena Caini

Saverio Carito

Matteo Carletti

Ilaria Castelli

Ludovico Ciacci

Paolo Cini

Manuela Cippitelli

Elena Clementi

Matteo Collini

Andrea Corsi

Andrea Corsoni

Luca Daveri

Mauro De Biasi

Lucia Di Noi

Alessandra Di Tella

Pierluigi Failla

Valentina Fambrini

Samuele Forconi

Lucia Gentili

Roberto Giorgi

Annamaria Giovannoni

Francesco Gnarra

Ciro Guariglia

Mirko Leommanni

Michele Moramarco

Riccardo Nieto

Giacomo Novembri

Davide Pallassini

Carlo Alberto Pascucci

Erik Peruzzi

Gabriele Petri

Marcello Piliego

Nicola Pisu

Claudio Rocchi

Laura Romano

Francesco Russo

Fabrizio Simi

Carlo Snickars

Martina Tiribocchi

Andrea Tommasi

Francesco Vivi

Matilda Xheladini

Matteo Zampi

La dispensa e' rilasciata per uso dei soli studenti

del Corso di Calcolatori Elettronici 1

del Corso di Laurea di Ingegneria Informatica

della Facoltà di Ingegneria

Università degli Studi di Siena

Copyright notice

All figures from Computer Organization and Design: The Hardware/Software Approach, Second Edition, by David Patterson and

John Hennessy, are copyrighted material. (COPYRIGHT 1998 MORGAN KAUFMANN PUBLISHERS, INC. ALL RIGHTS

RESERVED.)

Figures may be reproduced only for classroom or personal educational use in conjunction with the book and only when the above

copyright line is included. They may not be otherwise reproduced, distributed, or incorporated into other works without the

prior written consent of the publisher.

INDICE

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

Lezione

1:

2:

3:

4:

5:

6:

7:

8:

9:

10:

11:

12:

13:

14:

15:

16:

17:

18:

19:

20:

Introduzione

Assembly MIPS (parte prima)

Assembly MIPS (parte seconda)

Valutazione delle prestazioni (parte prima)

Valutazione delle prestazioni (parte seconda)

Valutazione delle prestazioni (parte terza)

Standard IEEE-754 per le operazioni floating point

Assembly MIPS

Interrupt

Implementazione di semplice CPU MIPS

BUS

BUS PCI, SCSI e USB

Tecniche di pilotaggio dei dispositivi I/O

Esempi di dispositivi di I/O: il timer e la porta seriale

Hard disk

Introduzione al sottosistema di memoria

Introduzione alla memoria cache (parte prima)

Introduzione alla memoria cache (parte seconda)

Memoria virtuale

Pipeline

LEZIONE 1

Introduzione

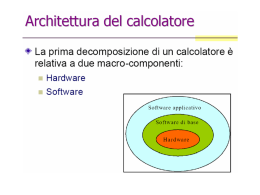

1.1 INTRODUZIONE

Queste dispense sono state raccolte con lo scopo di fornire un riferimento sintetico alla

materia trattata nel Corso di Calcolatori Elettronici 1 presso la Facolta’ di Ingegneria

dell’Universita’ di Siena. Per gli approfondimenti (molti!) alla materia si rimanda ai Testi di

Riferimento del corso [1], [2], [3], [4], [5], [6], [7] e ai Riferimenti Bibliografici posti al

termine di ognuna delle venti lezioni. Gli argomenti di una lezione vengono tipicamente trattati

in circa due ore. Accompagnano il materiale didattico del corso, gli esercizi proposti nelle

prove di esame e i simulatori architetturali (disponibili sul sito web del corso [8]).

1.1.1 Prerequisiti del Corso

Per affrontare il corso di Calcolatori Elettronici 1 è opportuno aver acquisito alcune

conoscenze di base dai corsi precedenti, con particolare riferimento a:

• struttura base della macchina (macchina di Von Neumann, ciclo fetch-execute);

• lettura e scrittura di programmi C;

• passi per eseguire il programma (compilazione, collegamento, caricamento, esecuzione);

• progetto logico di un circuito (componenti logici, macchine a stati finiti,).

1.2 STRUTTURA DEL CORSO

I tre

•

•

•

principali obiettivi che il corso si propone di raggiungere sono:

imparare a misurare e analizzare le prestazioni di un Calcolatore;

capire l’architettura di un Calcolatore;

individuare possibili ottimizzazioni per migliorare le potenzialità di un Calcolatore.

1.2.1 Analisi delle prestazioni

Per poter valutare la bontà di un Calcolatore è necessario innanzitutto mettersi d’ accordo su

come misurarne le prestazioni relativamente allo scopo che si vuole adibire a quella macchina.

L’obiettivo della prima parte del corso è quindi quello di analizzare i fattori che influenzano le

prestazioni, capire come effettuare un’analisi quantitativa di essi e discutere di come questi

siano influenzati dall’architettura scelta. Gli argomenti affrontati in questa prima parte sono:

• definizione “software” della macchina (lezioni 2,3);

• metriche e benchmark per la valutazione delle prestazioni (lezioni 4,5,6);

• influenza dei criteri prestazionali sulla definizione “software” (lezioni 7,8,9).

1.2.2 Analisi dell’architettura

Per comprendere l’architettura dei moderni Calcolatori si analizzera’ l’organizzazione interna

dei principali elementi della macchina cosi’ come sono oggi realizzati: processore, memoria,

sottosistema di input/output (I/O). I principali argomenti trattati in questa parte sono:

• struttura del processore: parte di controllo e datapath (lezione 10);

• reti di interconnessione e interfacciamento (lezioni 11,12);

• sottosistema di Input/Output (lezioni 13,14,15);

• memoria (lezione 16).

1.2.3 Meccanismi architetturali per il miglioramento delle performance

Parti “accessorie” del Calcolatore ma ormai quasi universlamente utilizzate sono:

• memoria cache (lezioni 17,18);

• memoria virtuale (lezione 19);

• pipeline (lezione 20).

1.1

1.3 EVOLUZIONE DEI CALCOLATORI

1.3.1 La legge di Moore

Il forte sviluppo dei Calcolatori Elettronici dipende in gran parte dai progressi della

Tecnologia Elettronica e in particolare dei Circuiti Integrati la cui capacita’, in termini di

numero di transistor e quindi di funzionalita’ ha seguito per oltre 40 anni la Legge di Moore:

“Il numero di transistor su singolo chip raddoppia ogni 18 mesi”

Nel 1965, Gordon Moore (che successivamente nel 1968 fondo’ con R. Noyce la ditta Intel)

osservo’ l’evoluzione dell’industria elettronica nei 6 anni precedenti (1959-1965) e gli sembro’

ragionevole una proiezione [9] secondo cui il numero di “componenti a minimo costo” in un

circuito integrato sarebbe raddoppiato ogni 12 mesi; questa supposizione si rivelò corretta “al

90%” fino al 1975. Osservando invece, il numero di transistor nei processori Intel da meta’ del

1971 (anno di introduzione del processore 4004, con 2300 transistor) a fine del 2000 (anno di

introduzione del processore Pentium-4, con 43 milioni di transistor) si puo’ osservare un

raddoppio dei transistor solo ogni 24 mesi (in parte questo è contemplato in [9]). Altri (non

Moore) hanno fatto si’ che quella formulata sopra sia la versione “popolarmente acclamata

della Legge di Moore”.

Pent 4

Pent III

Pent II

Pent Pro

Pent.

Migliaia di Transistor

10000

486SL

486

286

100

8086

8080

4004

1

1972

1976

1980

1984

1988

1992

1996

2000

Figura 1.1: La legge di Moore.

A prescindere dalle diverse interpretazioni, resta comunque il dato di fatto di uno

stupefacente incremento, che non ha eguali in nessun altro settore industriale. Simili

incrementi si possono altresi’ registare per altri componenti dell’Architettura del Calcolatore:

• Processore: Porte logiche:

+30%/anno

Velocità clock:

+20%/anno

• Memoria:

Dimensione:

+60%/anno

Velocità:

+9%/anno

Costo per bit:

+25%/anno

• I/O (Disco): Dimensione:

+60%/anno

1.3.2 I tipi di Calcolatori Elettronici

Si puo’ dire che agli inizi del terzo millennio le tipologie di Calcolatori esistenti sono

sostanzialmente tre (v. anche figura 1.2):

• Sistemi Desktop (principalmente analizzati in questo corso);

• Sistemi Server (Network of Workstation, Supercomputer, Parallel Computers);

• Sistemi Embedded (dai telefonini ai palmari e ai sistemi di controllo industriale).

1.2

Mainframe

Massively

Parallel Processors

Vector

Supercomputer

Minicomputer

Portable

Computers

Networks of Workstations/PCs

Figura 1.2: Computer Food Chain.

Altre tipologie introdotte agli albori dell’introduzione dei “Calcolatori a programma

memorizzato” sono ormai scomparse (Mainframe, MiniComputer) o prevalentemente confluite

(Vector Supercomputer, Massively Parallel Processor) in altre tipologie.

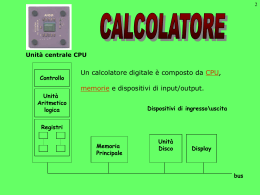

1.4 ARCHITETTURA DI UN CALCOLATORE DESKTOP

Un Calcolatore di tipo desktop può essere visto come un elettrodomestico componibile. Al suo

interno sono presenti infatti molti componenti che consentono di mettere in piedi l’intera

macchina in maniera abbastanza semplice e modulare. Una tipica organizzazione di un

Calcolatore Desktop e’ riportata in Figura 1.3. Tale organizzazione si discosta pochissimo

dall’originaria impostazione presentata da Von Neumann [10] nel 1946.

CPU

Cache

Bus

Memoria

Adattatore

(bridge)

Disco

Dispostivi di I/O: Display

Tastiera

Controller

Scheda di rete

INTERNET

Figura 1.3: Organizzazione a blocchi.

1.3

1.4.1 Limiti dovuti alla dimensione del chip

Sabbene sia teoricamente conveniente avere chip “grossi” per ottenere un numero elevato di

transistor (e quindi di funzionalita’) sullo stesso, cio’ non viene attuato nella realta’ perche’

“il costo di un chip è proporzionale a circa il cubo della sua area. “

E’ infatti possibile calcolare il costo del chip (o ‘die’) con la seguente formula:

C DIE =

CWAFER

N DIE ⋅ YWAFER

dove: CDIE = Costo del die

CWAFER = Costo del wafer

NDIE = Numero di die in un wafer

YWAFER = ‘Yield’ o Resa del wafer (numero ‘die’ per unita’ di sup.)

Il numero di die all’interno di un wafer e la resa del wafer stesso dipendono dall’area del die,

come si vede dalle seguenti formule:

2

N DIE

π ⋅ ⎛⎜ DWAFER 2 ⎞⎟

AWAFER

⎠ − π ⋅ DWAFER − N

= ⎝

TEST ≅

ADIE

ADIE

2 ⋅ ADIE

YWAFER =

1

2

1 + (F ⋅ ADIE 2)

dove: DWAFER = Diametro del wafer

ADIE = Area del ‘die’=⋅π(DWAFER/2)2

AWAFER = Area del wafer

NTEST = Numero di ‘die’ usati per test

F

= Difetti per unita’ di superfice

1.4.2 Limiti dovuti al consumo di potenza

Il consumo di potenza di un calcolatore elettronico è un altro degli aspetti fondamentali che

limita il numero di componenti che e’ possibile integrare sul chip. Inolre, questo problema

risulta essere maggiormente pressante con l’avvento di CPU sempre più complesse.

Il consumo di potenza è influenzato dalla densità con cui sono costruiti i chip; chip più densi,

che significano quindi sistemi più complessi, richiedono un maggiore consumo di potenza per

unità di superficie. Per un Calcolatore Desktop il limite “a braccio” che viene utilizzato per la

potenza totale dissipata (Total Dissipated Power o TDP) e’ intorno ai 100W.

1.5 DEFINIZIONE DI “ARCHITETTURA DI UN CALCOLATORE”

L’Architettura di un Calcolatore e’ “...l’insieme dell’insieme degli attributi visibili al

programmatore, ovvero la struttura concettuale e il comportamento funzionale, distinti

dall’organizzazione del flusso dei dati e del controllo, dagli elementi logici e

dall’implementazione fisica” (tradotto dalla definizione originale che compare in [12]).

Per definire un’architettura si dovrà specificare come organizzare i dispositivi di

memorizzazione, definire quali siano i tipi di dato e le strutture dati, stabilire l’insieme delle

istruzioni ed il loro formato, fissare un metodo di indirizzamento della memoria e di accesso

ai dati e alle istruzioni ed, infine, essere in grado di gestire le eccezioni.

In altri termini, l’Architettura del Calcolatore e’ l’interfaccia tra cio’ che viene fornito

dall’Hardware e cio’ che viene richiesto dal Software.

1.4

Un termine vicino ma distinto e’ Microarchitettura, che viene usato per definire le risorse ed i

metodi per implementare una data Architettura [13] di un Calcolatore ovvero la

Microarchitettrura e’ l’implementazione di una Architettura e fornisce a sua volta la specifica

da utilizzare per il progetto logico (e successivamente elettrico e fisico).

1.6 RIFERIMENTI BIBLIOGRAFICI

[1] D.A. Patterson, J.L. Hennessy, "Struttura e Progetto dei Calcolatori" 2a edizione ITALIANA

(traduzione della 3a edizione inglese), Zanichelli, Luglio 2006, ISBN 978-88-08-09145-1.

[2] G. Bucci, "Architettura dei Calcolatori Elettronici", McGraw-Hill, 2001, ISBN 88-386-0889-X.

[3] P. Corsini, G. Frosini, "Architettura dei calcolatori", McGraw Hill, 1997, ISBN 88-386-0735-4.

[4] A. S. Tanenbaum, "Structured computer organization", 4th ed., Prentice-Hall International, 1999,

ISBN 0130959901.

[5] V.P. Heuring, "Computer Systems Design and Architecture" 2ed, Pearson/Prentice Hall, 2004,

ISBN 0-13-191156-2.

[6] S. Furber, "ARM System-on-chip architecture", 2ed, Pearson/Addison Wesley, 2000, ISBN 0-20167519-6.

[7] W. Stallings, "Architettura e organizzazione dei calcolatori", Jackson Libri, 2000, ISBN 88-2561836-0.

[8] Sito Web del Corso.

http://www.dii.unisi.it/~giorgi/didattica/calel

[9] G. E. Moore, “Cramming more components onto integrated circuits”, Electronics Magazine (1965)

(ftp://download.intel.com/museum/Moores_Law/Articles-Press_Releases/Gordon_Moore_1965_Article.pdf).

[10] J. von Neumann, “First Draft of a Report on the EDVAC” (anche disponibile al sito:

http://www.virtualtravelog.net/entries/2003-08-TheFirstDraft.pdf).

[11] Intel, Microprocessor Quick Reference Guide,

http://www.intel.com/pressroom/kits/quickrefyr.htm

[12] G. M. Amdahl, G.A. Blaauw, F.P. Brooks, (1964), “Architecture of the IBM System/360”, IBM J.

Research and Development 8. Reprinted (2000) loc.cit. 44 21-37.

(http://www.research.ibm.com/journal/rd/441/amdahl.pdf)

[13] B. Shriver and B. Smith. The Anatomy of a High-Performance Microprocessor, A Systems

Perspective. IEEE Computer Society Press, July 1998.

1.5

LEZIONE 2

Assembly MIPS (parte prima)

.

2.1 INTRODUZIONE

I calcolatori, per loro natura, comprendono segnali composti da due soli elementi, che

rappresentano lo stato di on e off, identificati nei numeri 0 e 1 e il linguaggio formato da

questo alfabeto è detto linguaggio macchina. I programmatori anziché il linguaggio macchina

utilizzano il linguaggio assembly che associa alle sequenze binarie del linguaggio macchina una

rappresentazione simbolica più comprensibile. Tutti i comandi che vengono impartiti ai

calcolatori sono detti “istruzioni”, ossia sequenze di 0 e 1 che il calcolatore è in grado di

comprendere. Un programma assemblatore traduce la notazione simbolica, quindi in linguaggio

assembly, di un’istruzione, nella corrispondente notazione binaria, ovvero in linguaggio

macchina.

Ad esempio:

add $so, $s1, $s2

000000 10010 10011 10001 00000 100000

(linguaggio assembly MIPS)

(linguaggio macchina MIPS)

L’ istruzione nell’esempio dice al calcolatore di sommare due numeri.

Il linguaggio macchina ha una diretta implementazione in termini circuitali. Sopra al linguaggio

assembly si costruiscono dei linguaggi ad alto livello che includono delle istruzioni più vicine al

linguaggio naturale in quanto permettono la programmatore di non specificare certi tipi di

dettagli implementativi della macchina ed inoltre sono più flessibili rispetto all’assembly.

Alcuni dei più famosi linguaggi ad alto livello sono il Java, il C++, il C e il Pascal. I programmi

che utilizzano tali linguaggi si chiamano compilatori e consentono al programmatore di scrivere

espressioni del tipo:

C = A + B;

che il compilatore tradurrà in istruzione assembly

(linguaggio ad alto livello C)

add $so, $s1, $s2.

Dove la variabile A è associata al contenuto del registro $s1, la variabile B a quello del

registro $s2 e la variabile C al registro $s0.

2.2 ISTRUZIONI ASSEMBLY

Per poter gestire l’hardware di un calcolatore bisogna saper parlare il suo linguaggio; le parole

del linguaggio del calcolatore si chiamano istruzioni e il vocabolario è il set di istruzioni. Il set

di istruzioni prescelto proviene dal processore MIPS, usato fra gli altri da NEC, Nintendo,

Sylicon Graphics e Sony. L’architettura dei processori MIPS appartiene alla famiglia delle

architetture RISC (Reduced Instruction Set Computer) sviluppate dal 1980 in poi. I

principali obiettivi delle architetture RISC sono la semplificazione della progettazione

dell'hardware e del compilatore, la massimizzazione delle prestazioni e la minimizzazione dei

costi. Gli operandi delle istruzioni non possono essere variabili in memoria ma devono essere

scelti fra i registri interni al microprocessore. Fanno eccezione solo le istruzioni load e store

che fanno riferimento a variabili in memoria. Un processore possiede un numero limitato di

registri ad esempio il processore MIPS possiede 32 registri composti da 32-bit (word). In

tutti i casi in cui è possibile i registri sono associati alle variabili di un programma dal

compilatore. Inoltre se i registri non fossero sufficienti per rappresentare le variabili che

vogliamo, possiamo ricorrere alla memoria, ma questo metodo non si usa sempre dato che

2.1

l’accesso alla memoria è più lento di quello ai registri, argomento che sarà affrontato in

dettaglio nella lezione 16. Per identificare i registri si usano nomi simbolici preceduti da $, ad

esempio: $s0, $s1 oppure possono essere anche indicati direttamente mediante il loro

numero (0, …, 31) preceduto sempre da $. I nomi simbolici e i numeri per i registri vengono

assegnati attraverso questa convenzione:

Tabella 2.1: Convenzione per i registri MIPS

Numero registro

0

2-3

4-7

8-15

16-23

24-25

26-27

28

29

30

31

Uso

Valore costante 0

Valore dei risultati e valutazione di espressione

Parametri

Variabili temporanee

Variabili salvate

Altre variabili temporanee

Riservato al kernel

Global pointer

Stack pointer

Frame pointer

Indirizzo di ritorno

Nome

$zero

$v0-$v1

$a0-$a3

$to-$t7

$s0-$s7

$t8-$t9

$k0-$k1

$gp

$sp

$fp

$ra

Le istruzioni del linguaggio assembly MIPS possono essere divise nelle seguenti categorie:

• Istruzioni ARITMETICO-LOGICHE

• Istruzioni LOAD and STORE (trasferimento da/verso memoria)

• Istruzioni di salto condizionato e non condizionato per il controllo del flusso di

programma

Il linguaggio assembly fornisce anche delle pseudoistruzioni che costituiscono un modo più

“comodo” per scrivere istruzioni assembly o brevi sequenze di istruzioni assembly. Queste

sono istruzioni fornite dall’assembler ma non implementate in hardware.

Ad esempio:

move $t0, $t1

esiste solo in assembly in quanto l’assemblatore traduce usando

add $t0, $t1, $zero

Nel registro t0 viene messo il risultato della somma del contenuto di t1 e di zero, ovvero

viene spostato il contenuto di t1 in t0.

2.2.1 Istruzioni aritmetiche

In MIPS, un’istruzione aritmetico-logica possiede tre operandi che sono sempre e solo

registri: i due registri contenenti i valori da elaborare (registri sorgente) e il registro

contenente il risultato (registro destinazione). L’ordine degli operandi è fisso: prima il

registro contenente il risultato dell’operazione e poi i due operandi.

Istruzione add

L’istruzione add serve per sommare il contenuto di due registri sorgente s1 e s2 e mettere il

risultato in s0.

2.2

Esempio:

Codice C: R = A + B

Codice MIPS: add $s0, $s1, $s2

Dove la variabile R è associata al registro $s0, la variabile A al registro $s1 e la variabile

B a $s2.

Nella traduzione da linguaggio ad alto livello a linguaggio assembly, le variabili sono associate

ai registri dal compilatore Quando dobbiamo svolgere operazioni con un numero di operandi

maggiore di tre queste possono essere effettuate scomponendole in operazioni più semplici, in

quanto ciascuna delle istruzioni MIPS può eseguire una sola operazione.

Ad esempio, per eseguire la somma delle variabili B, C , D ed E nella variabile A servono tre

istruzioni:

Codice C:

A=B+C+D+E

Codice MIPS: add $t0, $s1, $s2

add $t0, $t0, $s3

add $s0, $t0, $s4

# il registro $t0 contiene B+C

# il registro $t0 contiene B+C+D

# il registro $s0 contiene B+C+D+E

Dove la variabile A è associata al registro $s0, la variabile B al registro $s1, la

variabile C a $s2, la variabile D a $s3 e la variabile E a $s4. Il registro $t0 è utilizzato

per memorizzare temporaneamente il risultato.

Istruzione sub

L’istruzione sub serve per sottrarre il contenuto di due registri sorgente s1 e s2 e mette il

risultato in s0.

Esempio:

Codice C:

R=A-B

Codice MIPS: sub $s0 ,$s1, $s2

Dove la variabile R è associata al registro $s0, la variabile A al registro $s1 e la variabile

B a $s2.

2.2.2 Istruzioni di trasferimento

Gli operandi delle istruzioni aritmetiche devono risiedere nei registri che, come abbiamo già

detto, nel nostro processore MIPS sono 32. Se abbiamo programmi i cui dati richiedono più di

32 registri, ovvero hanno moltissime variabili, alcuni di questi risiedono nella memoria.

L’allocazione in memoria di alcune variabili è detto spilling (riversamento). A questo proposito

servono specifiche istruzioni atte a trasferire i dati dalla memoria ai registri e viceversa;

queste possono solo leggere o scrivere un operando ma non possono eseguire nessuna

operazione su di esso. Le operazioni base di questo tipo sono due la load e la store

rispettivamente.

Breve richiamo sulla struttura della memoria

La memoria può essere vista come un unico grande array uni-dimensionale con gli indirizzi che

rappresentano l’indice del vettore a partire da 0. Dato che i byte, composti da 8 bit, sono

utilizzati da molti programmi, la maggior parte delle architetture indirizza il singolo byte ma

per ragioni di efficienza i microprocessori trasferiscono più byte in un colpo solo (come ad

2.3

esempio un microprocessore a 32 bit). Quindi dato che i programmi utilizzano l’indirizzamento

al byte e le istruzioni sono a 32 bit (quindi comprendono 4 byte) il loro indirizzo è sempre a

multipli di quattro, così parole adiacenti hanno indirizzi che differiscono di un fattore di

quattro. All’interno di una parola i byte possono essere ordinati facendo corrispondere

all’indirizzo al byte (es. 0x00000000) il byte più significativo di una parola a 4 byte; si parla in

questo caso di disposizione big-endian (v. figura 2.1). Se invece si fa corrispondere

all’indirizzo al byte (es. 0x00000000) il byte meno significativo si parla di disposizione littleendian (v. figura 2.1).

Vogliamo andare alla parola 0 con questa sequenza di byte numerati da 0 a 3 le due

disposizioni sono:

Disposizione big-endian

0

1

2

3

Disposizione little-endian

3

2

1

0

Fgura 2.1: Disposizione dei bit per big-endian e little-endian. Nel caso big-endian la memorizzazione inizia

dal byte più significativo per finire col meno significativo; nel caso little-endian la memorizzazione inizia dal

byte meno significativo per finire col più significativo.

Istruzione load

L’istruzione LOAD serve per trasferire un dato dalla memoria in un registro. Il nome

convenzionale di questa istruzione nel linguaggio MIPS è lw, che significa load word (carica

una parola). L’istruzione lw ha tre argomenti: il registro di destinazione in cui caricare la

parola letta dalla memoria, una costante che rappresenta l’offset (o spiazzamento) e un

registro sorgente che contiene il valore dell’indirizzo base da sommare alla costante. Quindi

l’indirizzo effettivo della parola di memoria da caricare nel registro di destinazione viene

calcolato sommando un valore base, contenuto nel registro sorgente e un offset direttamente

specificato all’interno dell’istruzione.

$s 3

(BASE)

4*k

(OFFSET)

Figura 2.2: Schema di funzionamento dell’istruzione di LOAD.

Esempio:

Codice C: g = h + A[8]

Codice MIPS: lw $t0, 32($s3)

add $s1, $s2, $t0

# il registro $t0 assume il valore A[8]

# g = h + A[8]

2.4

In cui la variabile g è associata al registro $s1, la variabile h al registro $s2, A a $s3

(registro base), 8 rappresenta il nono elemento del vettore di indirizzamento a 32 bit,

ossia l’offset 8 × 4=32.

Istruzione store

L’istruzione STORE è la complementare della load, infatti serve per trasferire il contenuto di

un registro verso la memoria. Il nome convenzionale in linguaggio MIPS è sw, che significa

store word (memorizza una parola). Il suo formato è analogo a quello della load: per primo

viene messo il nome del registro che contiene il dato da trasferire in memoria, poi l’offset e in

fine il registro base. Nell’istruzione store il registro destinazione è l’ultimo operando.

Esempio:

Codice C:

A[12] = h + A[8]

Codice MIPS: lw $t0, 32($s3)

add $t0, $s2, $t0

sw $t0, 48($s3)

# il registro t0 assume il valore A[8]

# il registro $t0 assume il valore h + A[8]

# memorizza h + A[8] in A[12]

In cui la variabile h è associata al registro $s2, A a $s3 (registro base), 8 rappresenta il

nono elemento del vettore di indirizzamento a 32 bit, ossia l’offset 8 × 4=32, ugualmente

12 che ha un offset di 12 × 4=48.

2.2.3 Istruzioni di salto condizionato e non condizionato

Le istruzioni di salto condizionato e non condizionato sono rese necessarie dalla struttura del

calcolatore. L'unità di controllo fa funzionare l’elaboratore che da quando viene acceso a

quando viene spento esegue di continuo il ciclo di prelievo / decodifica / esecuzione (fetch /

decode / execute ), la cui struttura è schematizzata nella seguente tabella.

Tabella 2.2: Il ciclo Fecth-Decode-Execute.

Passo 1.

Carica un'istruzione dalla memoria puntata da un registro speciale chiamato “program counter” (PC), e la

assegna a un registro interno chiamato IR.

Passo 2.

Cambia PC con l'indirizzo successivo in memoria (PC=PC+4).

Passo 3.

Determina il tipo di istruzione appena caricata nel registro delle istruzioni in base al suo opcode (Codice

Operativo).

Passo 4.

Si chiede se l'istruzione utilizza una parola in memoria. In tal caso determina l’effettivo indirizzo

dell’operando in memoria (base + offset).

Passo 5.

Se necessario, carica la parola residente in memoria in un registro della cpu.

Passo 6.

Esegue l'istruzione.

Passo 7.

Torna all'inizio, al 1 passo, ed esegue la prossima istruzione.

Il ciclo descritto in tabella può essere così sintetizzato:

• Operazione di FETCH

2.5

Passi 1 2

• Operazione di DECODE

Passo 3

• Operazione di EXECUTE

Passo 4, 5, 6.

Istruzioni particolari possono alterare il prelievo delle istruzioni da celle consecutive come ad

esempio le istruzioni di salto.

Le istruzioni di salto condizionato e non condizionato prendono il nome anche di istruzioni di

decisione in quanto alterano il flusso principale del programma, ovvero cambiano la “prossima”

istruzione da eseguire. Le istruzioni di salto condizionato utilizzano un campo offset di 16 bit

(con segno); possono quindi saltare a una locazione posta nell’intervallo [-215-1; 215].

Le istruzioni di salto incondizionato contengono invece un campo di 26 bit per specificare

l’indirizzo, anche se il calcolo dell’indirizzo effettivo è diverso a seconda del tipo di istruzione,

come vedremo nel capitolo 2. I salti condizionati si dividono in beq (branch if equal), bne

(branch if not equal) e slt (set on less than) mentre quelli incondizionati vengono effettuati

con l’istruzione j (jump) e jal (jump and link).

Istruzioni di salto condizionato

Le istruzioni di salto sono effettuate attraverso le operazioni di branch che cambiano il

flusso del programma creando diramazioni. L’istruzione beq trasferisce il flusso di controllo

(PC) all’istruzione etichettata con Label se e, solo se, il valore contenuto nel registro t0 è

uguale al valore del registro t1:

beq $t0, $t1, Label

Esempio:

Codice C:

if (i= =j)

f = g + h;

f =f –i;

Codice MIPS:

beq $s3, $s4, L1

add $s0, $s1, $s2

L1: sub $s0, $s0, $s3

# va a L1 se i = j

# f = g + h ( si salta se i = j )

# f = f – i ( eseguita sempre)

Dove la variabile i è associata al registro $s3, la variabile j al registro $s4, la variabile f

a $s0, la variabile g a $s1 e la variabile h a $s2.

L’istruzione bne indirizza all’istruzione etichettata con Label se e, solo se, il valore contenuto

nel registro t0 non è uguale al valore del registro t1.

bne $t0, $t1, Label

E’ opportuno chiedersi a questo punto quale istruzione utilizzare nel caso vogliamo fare

confronti di disuguaglianza ( <, ≤ , >, ≥ ) fra due variabili. A questo proposito viene utilizzata

l’istruzione slt che serve per verificare se la variabile corrispondente al registro s0 è minore

della variabile corrispondente al registro s1. Il registro t0 diventa uguale a 1 se s0 < s1 0

altrimenti.

Quindi il test finale è realizzato da un’istruzione bne che confronta i registri t0 e zero,

oppure da un’istruzione beq che confronta i registri t0 e la costante 1.

2.6

slt $t0, $s0, $s1

Esempio:

Codice C:

if A<B;

then C=1;

else C=0;

Codice MIPS: slt $t0, $s1, $s2

La variabile A è associata al registro $s1, la variabile B a $s2, e la variabile C a $t0.

Istruzioni di salto non condizionato

L’istruzione di salto non condizionato è j ed indica all’elaboratore di eseguire sempre il salto;

l’indirizzo di destinazione del salto è un indirizzo assoluto di memoria.

Esempio:

Codice C:

if (i = = j) f = g + h;

else f = g – h;

Codice MIPS: beq $s3, $s4, L1

L1:add $s0, $s1, $s2

bne $s3, $s4, L2

L2: sub $s0, $s1, $s2

j esci

# va a L1 se i = j

# f = g + h ( si salta se i = j )

# va a L2 se i ≠ j

# f = g -h

# vai a esci

La variabile i è associata al registro $s3, la variabile j al registro $s4, la variabile f al

registro $s0, e le variabili g e h rispettivamente a $s1 e $s2.

L’istruzione di salto non condizionato jal richiede un’analisi più approfondita che sarà

affrontata nella lezione 3.

2.2.4 Esempi di programmi assembly

Implementazione ciclo “while”

Codice C: while (A[i]==k)

i=i+j;

Codice MIPS:

Ciclo: add $t1, $s3, $s3

add $t1, $t1, $t1

add $t1, St1, $s6

lw $t0, 0($t1)

bne $t0, $s5, esci

add $s3, $s3, $s4

j ciclo

Esci:

# il registro temporaneo $t1 è uguale a 2 × i

# il registro temporaneo $t1 è uguale a 4 × i

# $t1 è uguale all’indirizzo di A[i]

#il registro temporaneo $t0 è uguale a A[i]

# vai ad esci se A[i]=k

# i=i+j

# vai a ciclo

Si assuma che le variabili i, j e k corrispondano ai registri $s3, $s4 e $s5 rispettivamente e

che $s6 contenga l’indirizzo di base del vettore A.

Implementazione ciclo “do while”

Codice C: do

2.7

g = g+A[i];

i=i+j;

while (i!=h)

Codice MIPS:

Ciclo: add $t1, $s3, $s3

add $t1, $t1, $t1

add $t1, St1, $s5

lw $t0, 0($t1)

add $s1, $s1, $t0

add $s3, $s3, $s4

bne $s3, $s2, ciclo

# il registro temporaneo $t1 è uguale a 2 × i

# il registro temporaneo $t1 è uguale a 4 × i

# $t1 è uguale all’indirizzo di A[i]

# il registro temporaneo $t0 è uguale a A[i]

# g=g+A[i]

# i=i+j

# se i ≠ h vai a ciclo

Si suppone che le variabili g e h siano associate a $s1 e $s2, i e j associate a $s3, $s4 e che

$s5 contenga l’indirizzo di base di A.

2.3 LINGUAGGIO MACCHINA

Tutte le istruzioni MIPS hanno la stessa dimensione (32 bit). I 32 bit hanno un significato

diverso a seconda del formato (o tipo) di istruzione. Tutte le istruzioni scritte dal

programmatore in linguaggio assembly vengono passate al calcolatore come una sequenza finita

di bit scritta in base 2. Il tipo di istruzione è riconosciuto in base al valore dei 6 bit più

significativi che compongono il codice operativo (OPCODE, OP) mentre i rimanenti 26 bit sono

suddivisi diversamente in base al formato in cui l’istruzione è scritta. Esistono tre tipi di

formati:

• Tipo R (register)

• Tipo I (immediate)

• Tipo J (jump)

2.3.1 Formato di tipo R

Con il formato di tipo R vengono descritte le funzioni aritmetico-logiche. A ciascuno dei campi

delle istruzioni MIPS viene associato un nome, per poter fare più agevolmente gli opportuni

riferimenti.

opcode

6 bit

rs

5 bit

rt

5 bit

rd

5 bit

shamt

5 bit

funct

6 bit

Ogni campo in cui è suddivisa l’istruzione ha un preciso significato:

• Op (opcode) identifica il tipo di operazione è chiamato anche codice operativo

• Rs primo operando sorgente

• Rt secondo operando sorgente

• Rd registro di destinazione che contiene il risultato dell’operazione

• Shamt questo termine contiene il valore dello scorrimento (shift amount che verrà

discussa successivamente)

• Funct funzione. Seleziona una variante specifica dell’operazione base descritta nel

campo op, è chiamato “codice funzione”.

Esempio:

2.8

Add $t0, $s1, $s2

0

17

18

8

0

32

000000

10001

10010

01000

00000

100000

Esempio istruzione formato R:

Nome campo

Dimensione

Add $s1,$s2,$s3

Op

6 bit

000000

Rs

5 bit

10010

Rt

5 bit

10011

Rd

5 bit

10001

Shamt

5 bit

00000

Funct

6 bit

100000

2.3.2 Formato di tipo I

Il formato di tipo I nasce dall’esigenza di specificare operandi immediati (costanti)

direttamente nelle istruzioni. In generale servirebbero 32 bit ma fortunatamente nella

maggioranza dei software le costanti utilizzate sono piccole, quindi con 16 bit si risolve già la

stragrande maggioranza dei casi. Infatti quando si vuole rappresentare un’istruzione di

trasferimento con il formato R possono nascere dei problemi in quanto questa necessita di

campi di dimensioni maggiori rispetto a quelli sopra specificati. Ad esempio l’istruzione load

deve specificare due registri e una costante; se la costante dovesse essere specificata in uno

dei campi da cinque bit, sarebbe limitata al valore di 25, cioè 32, ma poiché questa serve per

indirizzare all’interno di vettori di grandi dimensioni spesso assume valori maggiori. Per far

rimanere la lunghezza delle istruzioni sempre di 32 bit il compromesso è quello di creare

formati diversi per le diverse istruzioni.

Per le istruzioni di trasferimento utilizziamo il tipo I che ha la seguente struttura:

opcode

6 bits

rs

5 bits

rt

5bits

In questo caso i campi hanno il seguente significato:

• opcode identifica il tipo di istruzione

• rs indica il registro base

• rt indica il registro destinazione dell’istruzione di caricamento

• address riporta lo costante (in alcuni casi offset)

2.9

address

16 bits

Esempio:

lw $t0, 32($s3)

35

19

8

32

100011

10011

01000

0000000000100000

Esempio istruzione formato I:

Nome campo

Dimensione

Lw $t0, 32($s3)

Op

6 bit

100011

Rs

5 bit

10011

Rt

5 bit

01000

Address

16 bit

0000 0000 0010 0000

Con il formato I oltre che alle istruzioni di trasferimento vengono descritte anche tutte le

istruzioni con operandi immediati e operazioni di salto condizionato. Quest’ultime possono

avere un offset maggiore dei 16 bit, che consente il formato I, quindi una valida alternativa

consiste nello specificare un registro il cui valore deve essere sommato all’indirizzo di salto

permettendo così di raggiungere 32 bit. Il registro da usare è il program counter che

contiene l’indirizzo dell’istruzione corrente e quindi può saltare fino a una distanza di ± 215

istruzioni rispetto alle istruzioni in esecuzione. Siccome in quasi tutti i cicli e i costrutti di if,

in cui i salti condizionati vengono usati, l’etichetta a cui salto è tipicamente un numero di

istruzioni minore di 216 parole, il program counter è la scelta ideale.

2.2 3 Formato di tipo J

Il terzo tipo di formato di istruzioni (formato J) è il formato usato per le istruzioni di salto

incondizionato.

Op

6 bit

Address

26 bit

In questo caso i campi hanno il seguente significato:

• Op indica il tipo di operazione

• Address riporta una parte (26 bit su 32) dell’indirizzo assoluto di destinazione del

salto

L’assemblatore sostituisce l’etichetta con i 28 bit meno significativi traslati a destra di 2

(divisione per 4 per calcolare l’indirizzo di parola) per ottenere 26 bit; in pratica elimina i due

zero finali e si amplia lo spazio di salto tra zero e 228 byte (ossia 226 word). I 26 bit del campo

indirizzo rappresentano un indirizzo di parola. Quindi corrispondono a un indirizzo di byte

composto da 28 bit; poiché il registro PC è composto da 32 bit si verifica che l’istruzione jump

rimpiazza solo i 28 bit meno significati del PC lasciando inalterati i rimanenti quattro bit più

significativi.

2.10

Nome campo

Dimensione

j 32

Op

6 bit

000010

Address

26 bit

00 0000 0000 0000 0000 0000 1000

2.11

LEZIONE 3

Assembly MIPS (parte seconda)

3.1 LA MOLTIPLICAZIONE

Come è noto effettuando l’operazione di moltiplicazione tra due numeri binari rappresentati

su n bit, in generale sono necessari 2n bit per rappresentare il risultato [1].

Nel MIPS tutti i registri utilizzati hanno una dimensione di 32 bit; moltiplicando il contenuto

di due registri da 32 bit per rappresentare correttamente il risultato sono quindi necessari

64 bit.

Il risultato della moltiplicazione viene posto sempre in due registri dedicati (special porpouse)

da 32 bit ciascuno, denominati Hi e Lo in grado di contenere il prodotto su 64 bit.

L’istruzione MIPS per effettuare la moltiplicazione è mult (multiply).

Esempio:

mult $2, $3

#calcola il prodotto tra il contenuto dei registri $2 e $3 e il risultato si

trova nei registri Hi e Lo.

In particolare il registro Hi contiene i 32 bit più significativi del prodotto, Lo i 32 bit

meno significativi (Figura 3.1).

$2

HI

LO

mult

$3

64 bit

32 bit

Figura 3.1. L’istruzione mult.

Per eseguire la moltiplicazione tra numeri senza segno possiamo utilizzare multu (multiply

unsigned).

Il prodotto inserito nei registri Hi e Lo può essere recuperato con le istruzioni mfhi (move

from hi) e mflo (move from lo).

Esempio:

mfhi $4

mfhi $5

#trasferisce nel registro $4 il contenuto di Hi.

#trasferisce nel registro $5 il contenuto di Lo (Figura 3.2).

HI

LO

$4

$5

Figura 3.2. Le istruzioni mfhi e mflo.

3.1

3.2 LA DIVISIONE

LA DIVISIONE TRA DUE NUMERI PUÒ ESSERE EFFETTUATA IN MIPS UTILIZZANDO

L’ISTRUZIONE DIV (DIVIDE) .

Dividendo e divisore sono contenuti in registri da 32 bit e, analogamente a quanto accade per

la moltiplicazione, dopo l’esecuzione dell’istruzione div il risultato della divisione si trova in due

registri Hi e Lo che contengono rispettivamente il resto e il quoziente.

Esempio:

div $2,$3

#effettua la divisione tra il contenuto del registro $2 e il contenuto del

registro $3; il quoziente si trova nel registro Lo, il resto nel registro Hi

(Figura 3.3).

$2

%

$4

/

32 bit

HI

LO

32 bit

Figura 3.3. L’istruzione div.

Il contenuto dei registri Hi e Lo può essere recuperato in modo analogo a quanto abbiamo

visto per la moltiplicazione.

3.3 LE COSTANTI

L’utilizzo delle costanti ricorre spesso nelle operazioni usate comunemente in MIPS [1].

Utilizzando le sole istruzioni che abbiamo incontrato fino ad adesso tutte le volte che

abbiamo bisogno di una piccola costante dovremmo fare un ulteriore accesso alla memoria.

La costante zero viene utilizzata molto frequentemente, quindi ad essa è addirittura riservato

un registro indicato con $zero.

Per evitare ulteriori accessi alla memoria possiamo inserire le costanti direttamente nelle

istruzioni e velocizzare così la loro esecuzione.

Per inserire le costanti all’interno dell’istruzione è necessario utilizzare il formato-I (vedi

capitolo 2); come abbiamo già visto in questo tipo di formato sono disponibili 16 bit per

memorizzare la costante.

Istruzioni che contengono costanti al loro interno vengono dette immediate.

Esempio:

addi $t1, $t1, 5

#addizione immediata tra in contenuto di $t1 e la costante 5.

3.2

A questa istruzione corrisponde il seguente codice macchina:

op

rs

rt

immediate

8

9

9

5

6 bit

5 bit

5 bit

16 bit

001000

01001

01001 0000 0000 0000 0101

Figura 3.4. Esempio di istruzione addi.

Altri esempi di istruzioni immediate sono:

slti $t0, $s0, 3

andi $s0, $s1, 10

ori $s0, $s1, 4

#confronto tra il contenuto di $s0 e la costante 3;

#and logico tra $s1 e 10;

#or logico tra $s1 e 4.

Se le costanti assumono valori elevati e non possono essere rappresentate su 16 bit possiamo

caricare costanti di 32 bit nei registri utilizzando la combinazione di due diverse istruzioni.

Esempio:

Vogliamo caricare la costante 521.499 corrispondente al

00000000000001111111010100011011. Usiamo le istruzioni lui e ori:

codice

lui $t0, 0000 0000 0000 0111

binario

#load upper immediate carica i 16 bit più significativi

della costante nel registro $t0 e mette a zero i 16

bit meno significativi;

ori $t0, 1111 0101 0001 1011 #or immediate permette di caricare i 16 bit meno

significativi della costante nel registro lasciando

inalterati i 16 bit più significativi.

$t0 0000 0000 0000 0111 0000 0000 0000 0000 lui

0000 0000 0000 0111 1111 0101 0001 1011

$t0 0000 0000 0000 0111 1111 0101 0001 1011 ori

Figura 3.5. Le istruzioni lui e ori.

3.3

3.4 ISTRUZIONI PER LA MANIPOLAZIONE DI STRINGHE

Nella maggior parte dei calcolatori i caratteri vengono rappresentati su 8 bit (1 byte)

attraverso la codifica ASCII [1]. Poiché l’elaborazione dei caratteri è un’operazione

ricorrente, il MIPS prevede due istruzioni per trattare i byte: lb (load byte) che preleva dalla

memoria un byte e lo salva negli 8 bit meno significativi di un registro, e sb (store byte) che

prende gli 8 bit meno significativi di un registro e li mette in memoria.

Esempio:

Supponiamo di avere in memoria una word di 32 bit memorizzata a partire dall’indirizzo

che si trova in $4; ricordando che una variabile di tipo char occupa 1byte, utilizzando lb

e sb otteniamo:

0

$

1

an

a n-1

a n-2

a n-3

………

…

a1

a0

Figura 3.6. Le istruzioni lb e sb.

Solitamente i caratteri sono raggruppati in stringhe. Una stringa può essere rappresentata in

vari modi:

1) la lunghezza della stringa può essere indicata dal primo elemento;

N

Stringa

2) alla stringa possono essere associate due variabili: una che contiene la stringa stessa, e

una variabile di appoggio che ne contiene la lunghezza;

Stringa

N

3) l’ultimo elemento della stringa può essere un carattere particolare che ne indica la

fine.

Stringa

0

Il linguaggio C utilizza quest’ultimo metodo utilizzando come carattere di fine stringa un byte

di valore 0.

3.4

3.5 ISTRUZIONI LOGICHE

Tabella 3.1. Le istruzioni logiche.

Istruzione

Esempio

Significato

Commento

Formato

and

and $1, $2, $3

$1 = $2 & $3

AND logico

R

or

or $1, $2, $3

$1 = $2 | $3

OR logico

R

xor

xor $1, $2, $3

$1 = $2 ⊕ $3

XOR logico

R

nor

nor $1, $2, $3

$1 = ~($2 | $3) NOR logico

R

and immediate

andi $1, $2, 10

$1 = $2 & 10

AND logico con costante

I

or immediate

ori $1, $2, 10

$1 = $2 | 10

Or logico con constante

I

xor immediate

xori $1, $2, 10

$1 = ~$2 & ~10

XOR logico con costante

I

$1 = $2 << 10

Shift logico sx di una quantità costante

I

$1 = $2 >> 10

Shift logico dx di una quantità costante

Shift aritmetico dx di una quantità

costante

I

Shift logico sx di una quantità variabile

R

Shift logico dx di una quantità variabile

Shiftr aritmetico dx di una quantità

variabile

R

shift left logical sll $1, $2, 10

shift

right

logical

srl $1, $2, 10

shift

right

arithm.

sra $1, $2, 10

$1 = $2 >> 10

shift left logical sllv $1, $2, $3 $1 = $2 << $3

shift

right

logical

srlv $1, $2, $3 $1 = $2 >> $3

shift

right

arithm.

srav $1, $2, $3 $1 = $2 >> $3

I

R

Lo shift logico (destro/sinistro) coinvolge tutti i bit, mentre lo shift aritmetico lascia

inalterato il bit più significativo.

Esempio:

srl $1, $1, 1

0

$

1

an

#effettua lo shift logico a destra (1 posizione) del contenuto del

registro $1; il bit meno significativo si perde.

a n-1

a n-2

a n-3

………

…

a1

a0

Figura 3.7. Funzionamento dello shift logico a destra.

In generale shiftando verso destra di n posizioni, vengono persi gli n bit meno significativi.

Esempio:

sll $1,$1,1

#effettua lo shift logico a sinistra (1posizione) del contenuto del

registro $1; il bit più significativo viene perso.

3.5

$

1

an

a n-1

a n-2

a n-3

………

…

a1

0

a0

Figura 3.8. Funzionamento dello shift logico a sinistra.

Effettuando lo shift logico a sinistra di n posizioni, gli n meno significativi vengono posti a

zero, mentre gli n bit più significativi si perdono.

Esempio:

sra $1,$1,1

$

1

an

#effettua lo shift aritmetico a destra (1 posizione) del contenuto del

registro $1, lasciando inalterato il bit più significativo; anche in questo

caso il bit meno significativo si perde.

a n-1

a n-2

a n-3

………

…

a1

a0

Figura 3.9. Funzionamento dello shift aritmetico a destra.

Lo shift aritmetico a sinistra non viene utilizzato, perchè coincide con lo shift logico (sll).

3.6 ISTRUZIONI CHE TRADUCONO I PUNTATORI DEL C

Analizziamo un semplice programma C che fa uso di puntatori e il codice MIPS corrispondente.

Supponiamo che alle variabili siano associati i seguenti registri: zÆ$7, pÆ$8, cÆ$9.

typedef struct tabletag {

int i;

char *cp, c;

}table;

table z[20] ;

table *p ;

char c ;

p= &z[4]

..............

..............

c= p->c ;

..............

Il programma C definisce la struttura " table" i cui

campi

sono: un intero (32 bit), un puntatore a char (32 bit) e

un char (8 bit).

Un elemento di tipo table occupa quindi in totale 9

byte.

addi $1, $7, 36 #calcola l’indirizzo di z[4] (base + offset)

sw $1, 0($8) #salva l’indirizzo calcolato

lb $2, 8($8) #preleva il campo c (1 byte) dalla struttura puntata da p

sb $2, 0($9) #salva il campo prelevato nel registro corrispondente a c

3.6

3.7 MODI DI INDIRIZZAMENTO MIPS

I diversi modi con cui si può esprimere un indirizzo di memoria vengono chiamati modi di

indirizzamento [1][7]. Elenchiamo di seguito i modi di indirizzamento utilizzati in MIPS.

Nel seguito indicheremo con A l’indirizzo effettivo di memoria a cui ci riferiamo poiché, come

vedremo, questo può essere diverso dall’indirizzo che troviamo nell’istruzione.

Il modo in cui A viene calcolato differenzia un modo di indirizzamento dall’altro.

3.7.1 Register Addressing

Nel Register Addressing (indirizzamento tramite registro) gli operandi si trovano nei

registri; questo modo di indirizzamento è usato dalle istruzioni in formato-R.

L’indirizzo effettivo è dato da:

A = $(rs)

dove rs indica il numero del registro all’interno del set di registri.

op

rs

rt

rd

shamt

funct

Registro

Figura 3.10. Register addressing.

Istruzioni:

add, addu, sub, subu, mult, multu, div, divu, and, or, sll, slt, sltu, mfhi, mflo, jr.

3.7.2 Immediate Addressing

Nel modo di indirizzamento immediato l’operando è una costante specificata nell’istruzione,

come abbiamo già visto nel paragrafo dedicato alle costanti.

Il modo di indirizzamento immediato è utilizzato nelle istruzioni in formato-I.

In questo caso l’indirizzo effettivo sarà quindi uguale a quello scritto nel campo address

dell’istruzione in formato-I:

A = I (dove I è il contenuto del campo address)

op

rs

rt

immediate

Figura 3.11. Immediate addressing.

Istruzioni:

addi, addiu, andi, ori, slti, sltiu, lui.

3.7.3 Base Addressing

Nell’indirizzamento tramite base, l’operando si trova in una locazione di memoria individuata

dalla somma del contenuto di un registro e di una costante specificata nell’istruzione.

L’indirizzo effettivo è:

3.7

A = I + <contenuto del registro indicato in rs>

Il registro da utilizzare viene indicato nell’istruzione stessa.

Questo modo di indirizzamento è usato per esempio nelle istruzioni lw e sw, in cui l’indirizzo

degli operandi è dato dalla somma tra l’indirizzo di base e l’offset; per esempio lw $t0

32($s2) indica che l’indirizzo di base è contenuto nel registro $s2 e l’offset da sommare è 32

(contenuto nel campo address). L’offset è rappresentato in complemento a due (e varia tra –

32.768 e 32767).

op

rs

rt

Memoria

address

+

Registro

byte

halfword

word

Figura 3.12. Base addressing.

Istruzioni:

lw, lh, lb, lbu, sw, sh, sb.

3.7.4 PC-relative Addressing (base + index)

Il modo di indirizzamento relativo al program counter è stato introdotto per ovviare ad un

problema relativo all’ istruzione di salto condizionato (Branch).

L’istruzione Branch fa uso del formato-I, riservando quindi 16 bit al campo indirizzo.

In base a questa considerazione nessun programma potrebbe avere una lunghezza superiore a

216 poiché in caso contrario l’indirizzo a cui si deve “saltare” nella Branch non potrebbe essere

contenuto nel campo di 16 bit.

Poiché questa condizione è molto restrittiva possiamo usare un’alternativa che consiste

nell’utilizzo di un registro il cui valore deve essere sommato all’indirizzo specificato

nell’istruzione di salto.

A questo scopo viene utilizzato il registro PC (program counter) che contiene l’indirizzo

dell’istruzione corrente. Solitamente nei salti condizionati ci si sposta ad istruzioni vicine;

utilizzando il PC siamo in grado di spostarci fino ad una distanza di ±215 istruzioni rispetto

all’istruzione corrente.

Solitamente si fa in modo che il PC punti all’istruzione successiva a quella in esecuzione;

ricordando che le istruzioni sono tutte a 32 bit e quindi si trovano in memoria ad indirizzi

sempre multipli di 4, l’istruzione successiva a quella in esecuzione si trova all’indirizzo PC+4.

Quindi l’indirizzo effettivo di salto sarà dato da:

A = PC + 4 + I’ = PC + 4 + 4*I

dove I è il contenuto del campo address dell’istruzione (che può essere positivo o negativo) e

rappresenta la distanza dell’indirizzo a cui si deve saltare in termini di word. L’indirizzo PCrelative indica cioè il numero di parole che separano l’istruzione successiva a quella corrente

3.8

dall’istruzione a cui si salta. Nell’espressione I’ rappresenta questa stessa distanza in termini

di byte.

Poiché I è rappresentato su 16 bit, I’ sarà rappresentato su 18 bit, quindi il campo effettivo in

cui possiamo spostarci sarà 218.

op

rs

rt

Memoria

address

x4

+

PC + 4

Word

Figura 3.13. PC-relative addressing.

Istruzioni:

beq, bne.

3.7.5 Pseudodirect Addressing

Se dobbiamo effettuare salti su un campo più ampio di 218 possiamo utilizzare l’istruzione

Jump.

Consideriamo quindi l’istruzione di salto non condizionato Jump: essa utilizza il formato-J in

cui 6 bit vengono impiegati per il codice operativo e i restanti 26 per il campo indirizzo.

Il modo di indirizzamento pseudo-diretto viene utilizzato per impiegare al meglio i 26 bit

riservati all’indirizzo.

In questo caso l’indirizzo effettivo di salto è dato da:

A = (PC<31…28> , 0<27...0>) + I’ = (PC<31…28> , 0<27...0>) + 4*I

Anche in questo caso il campo address viene in pratica esteso di 2 bit, poiché I’ è

rappresentato su 28 bit. L’ampiezza massima del salto sarà quindi 228.

L’indirizzo effettivo viene ottenuto concatenando I’ con i 4 bit più significativi del program

counter.

op

00

address

Memoria

28 bit

31…2

8

32 bit

Memoria

Word

PC

4 bit

Figura 3.14. Pseudodirect addressing.

Istruzioni:

j,jal.

3.9

3.8 LINGUAGGIO ASSEMBLY E LINGUAGGIO MACCHINA

Il linguaggio Assembly fornisce una rappresentazione simbolica della codifica binaria usata dal

calcolatore, detta linguaggio macchina; l’Assembly è più semplice da leggere e da scrivere

rispetto al linguaggio macchina poiché utilizza simboli invece di bit [reference 1].

Inoltre l’Assembly permette di utilizzare pseudoistruzioni, ovvero istruzioni che non fanno

propriamente parte del linguaggio simbolico, ma che facilitano la scrittura dei programmi.

Come abbiamo visto nel corso della trattazione, vi sono differenze tra le istruzioni scritte in

Assembly e le corrispondenti stringhe di bit in linguaggio macchina.

Esempio:

Analizziamo l’istruzione add e il relativo codice macchina.

add $t2, $t0, $t1

op

rs

rt

rd

shamt

funct

000000

01000

01001

01010

00000

100000

0

8

9

10

0

32

Figura 3.15. Codice macchina relativo all’istruzione add.

In Assembly la destinazione è il primo operando, mentre in linguaggio macchina si trova

nel quarto campo; a livello di linguaggio macchina l’istruzione add viene rappresentata con

il codice operativo 0 e il codice funzione 32.

Un vantaggio che l’Assembly offre rispetto ai linguaggi di alto livello è la possibilità di

velocizzare l’esecuzione e minimizzare l’occupazione di memoria dei programmi. In quest’ottica

di ottimizzazione delle prestazioni è quindi importante sapere quali sono le istruzioni “reali”

che si nascondono dietro al linguaggio simbolico Assembly.

3.9 CONVENZIONI PER I REGISTRI MIPS

Tabella 3.2. I registri MIPS.

0

1

zero

at

costante 0

riservata all'assemblatore

2

3

v0

v1

valori dei risultati e

valutazione di espressioni

4

5

a0

a1

parametri utilizzati nella

chiamata delle procedure

6

7

a2

a3

8

t0

variabili temporanee

…

15

t7

3.10

16

s0

variabili salvate quando

…

23

s7

24

25

t8

t9

altre variabili temporanee

26

27

k0

k1

riservati al sistema operativo

28

29

30

gp

sp

global pointer

stack pointer

fp

frame pointer

31

ra

indirizzo di ritorno

si richiamano procedure

3.10 INTRODUZIONE ALLA CHIAMATA A FUNZIONE

Una procedura è una parte del programma dedicata alla risoluzione di un problema specifico,

uno strumento utilizzato per strutturare i programmi e renderli più facili da comprendere.

Nei successivi paragrafi verrà indicato il protocollo da seguire per implementare la chiamata

ed esecuzione di una funzione.

3.11 STRUTTURA DELLA CHIAMATA E DELL’ESUCUZIONE DI

UNA FUNZIONE

In questo paragrafo sono enunciate le varie fasi di una chiamata a funzione con le

convenzioni e le regole che le contraddistinguono; per ogni fase è riportato a fianco al nome

se questa avviene dal lato chiamante (programma che chiama la procedura) o dal lato chiamato

(procedura chiamata).

3.11.1 Prechiamata (lato chiamante)

Questa prima fase consiste nel preparare i parametri d’ingresso, quelli che servono alla

funzione che verrà successivamente chiamata per poter svolgere le operazioni per cui è stata

progettata.

Per questa operazione il MIPS rende disponibili 4 registri: $a0 - $a3.

In questi 4 registri vengono posti i primi quattro parametri necessari alla funzione; se vi è la

necessità di fornire più di quattro argomenti sarà richiesto l’impiego di uno stack (una coda

del tipo “last in first out”); in particolare per ogni funzione chiamata può essere necessario

allocare una porzione dello stack detto frame, di cui daremo una spiegazione più dettagliata in

seguito nel paragrafo 3.13 “gestione dello stack nell’assembler MIPS”.[1]

3.11.2 Chiamata a funzione (lato chiamante)

Il linguaggio assembly MIPS include un’istruzione apposita per le procedure, che salta ad un

indirizzo e contemporaneamente salva l’indirizzo dell’istruzione successiva nel registro $ra.

L’istruzione in questione è jal (jump and link) che si scrive semplicemente:

jal <etichetta della procedura>

La parte link del nome si riferisce al fatto che viene creato un collegamento (link), che

permette alla procedura di ritornare all’indirizzo corretto nel momento in cui termina; questo

“link” viene memorizzato nell’indirizzo $ra ed è detto indirizzo di ritorno. L’ indirizzo di

ritorno è fondamentale perché la stessa procedura può essere richiamata in più parti del

programma. [1]

Come già descritto nei capitoli precedenti l’indirizzo della prossima istruzione da prelevare è

contenuto in un particolare registro denominato PC (program counter); supponiamo che

l’istruzione puntata da PC sia la jal di Figura 3.16, il valore da salvare in $ra è PC+4 (il valore 4

deriva dal fatto che le istruzioni sono tutte a 32 bit e quindi si trovano in memoria ad indirizzi

sempre multipli di 4).

3.11

Prima dell’esecuzione della jal

Dopo l’esecuzione della jal

indirizzi

indirizzi

“∞”

PC

“∞”

jal proc

jal proc

ra

ra

PC

0

0

Figura 3.16. Meccanismo innescato dall’istruzione jal nella memoria.

3.11.3 Prologo (lato chiamato)

In questa fase si provvede all’allocazione di una parte di memoria che contiene i registri

salvati da una procedura e le variabili locali, questa parte dello stack prende il nome di

activation frame ( o activation record); il software MIPS utilizza un frame pointer per

indirizzare la prima parola del frame di una procedura.(vedere paragrafo 3.13 “gestione dello

stack nell’assembler MIPS”).

Nell’activation frame vanno salvati i registri che il chiamato intende sovrascrivere:

¾ Salvataggio degli argomenti della funzione oltre il quarto; i primi quattro possono

essere memorizzati nei registri $a0 - $a3.

¾ Salvataggio del precedente $ra se la funzione chiama altre funzioni; (vedi

paragrafo 3.14 “procedure annidate”)

¾ Salvataggio dei registri $s0 - $s7 se intendo sovrascriverli perché il chiamante si

aspetta di trovarli intatti.

3.11.4 Corpo (lato chiamato)

Questa fase coinvolge l’esecuzione delle istruzioni che realizzano le funzionalità previste dalla

procedura.

3.11.5 Epilogo (lato chiamato)

Nell’epilogo della funzione vi sono due operazioni fondamentali che devono essere svolte:

¾ Ripristino dei registri di interesse dallo stack: $s0 - $s7, $ra, $fp, $sp.

¾ Se devono essere restituiti dei valori questi devono essere posti nei registri $v0 e

$v1.

3.12

3.11.6 Ritorno al chiamante (lato chiamato)

Il linguaggio assembler MIPS include un’istruzione apposita jr (salto tramite registro) che

permette di ritornare all’indirizzo memorizzato nel registro $ra, cioè permette di tornare

nella procedura chiamante all’indirizzo dell’istruzione successiva a quella di chiamata a

funzione.

Al termine della procedura basterà quindi scrivere:

jr $ra .

Con questa istruzione si restituisce il controllo al chiamante.

Prima dell’esecuzione della jr

Dopo l’esecuzione della jr

indirizzi

indirizzi

“∞”

“∞”

jal proc

ra

jal proc

•••••

(

•••••

PC

•••••

PC

ra

)

•••••

•••••

•••••

Jr $ra

Jr $ra

0

0

Figura 3.17. Meccanismo innescato dall’istruzione jr nella memoria.

3.11.7 Post chiamata (lato chiamante)

Una volta ritornati nella funzione chiamante è possibile utilizzare i risultati forniti dalla

procedura chiamata tramite i registri $v0 e $v1.

3.12 MOTIVI PRINCIPALI DI UTILIZZO DELLO STACK

Come abbiamo visto analizzando le varie fasi di una chiamata a funzione esistono una serie di

situazioni in cui è necessario salvare dei dati in una zona della memoria per evitare che questi

vengano sovrascritti e quindi perduti. Quest’ area della memoria è chiamata stack.

Riassumendo i punti visti fin’ora lo stack deve essere utilizzato nei seguenti casi:

¾ Quando una procedura richiede più registri rispetto ai 4 riservati per il passaggio dei

parametri e ai 2 per la restituzione di valori.

¾ Quando si devono salvare dei registri che una procedura potrebbe modificare, ma che

il programma chiamante ha bisogno di mantenere inalterati.

3.13

¾ Quando si devono salvare delle variabili locali relative ad una procedura.

¾ Quando si devono gestire procedure annidate (procedure che richiamano al loro interno

altre procedure) e procedure ricorsive (procedure che invocano dei cloni di se stesse).

3.13 GESTIONE DELLO STACK NELL’ASSEMBLER MIPS

3.13.1 Descrizione generale dello stack

Lo stack è una coda del tipo “last in first out” e ha bisogno di un puntatore all’indirizzo del

dato introdotto più recentemente, per indicare dove la prossima procedura può memorizzare i

registri da riversare e dove può recuperare i vecchi valori dei registri. Il puntatore dello

stack è aggiornato ogni volta che viene inserito o estratto un valore di un registro; per questo

motivo il software MIPS alloca un altro registro appositamente per lo stack: lo stack pointer,

usato per salvare i registri che servono al programma chiamato. [1]

Lo stack può crescere verso l’alto (grow up) cioè da indirizzi di memoria più bassi a indirizzi di

memoria più alti, oppure verso il basso (grow down) cioè da indirizzi più alti a indirizzi più

bassi, come illustrato in figura 3.18.

Convenzione indirizzi

Grow down

Convenzione

Grow up

indirizzi

“∞”

“∞”

0

0

Figura 3.18. Convenzioni sul verso di crescita degli stack.

Inoltre lo stack si può suddividere in base a cosa punta lo stack pointer: può puntare al

successivo elemento dello stack vuoto (convenzione next empity), oppure può puntare

all’ultimo elemento dello stack pieno (convenzione last full).

3.13.2 Gestione dello stack nel MIPS

Per ragioni storiche nel caso dell’assembler MIPS lo stack adotta la convenzione grow down –

last full, e il registro riservato allo stack pointer è $sp.

Quindi l’inserimento di un dato nello stack avviene decrementando $sp per allocare lo spazio

necessario ed eseguendo l’operazione sw (store word) per inserire il dato; il prelevamento di

un dato dallo stack avviene incrementando $sp per eliminare il dato e riducendo quindi la

dimensione dello stack.

3.14

Esempio:

sw $t0, offset($sp)

lw $t0, offset($sp)

# salvataggio di $t0

# ripristino di $t0

Il segmento dello stack che contiene i registri salvati da una procedura e le variabili locali

prende il nome di activation frame . Il software MIPS utilizza un frame pointer ($fp) per

indirizzare la prima parola del frame di una procedura.

Tutto lo spazio in stack di cui ha bisogno una procedura (activation frame) viene

esplicitamente allocato dal programmatore in una sola volta.

Alla chiamata di una procedura lo spazio nello stack viene allocato sottraendo a $sp il numero

di byte necessari:

Esempio:

sub $sp , $sp, 12

# allocazione di 12 byte nello stack.

Al rientro da una procedura il frame viene rimosso dalla procedura incrementando $sp della

stessa quantità di cui lo si era decrementato alla chiamata:

Esempio:

addi $sp, $sp, 12

# dealloca 12 byte nello stack.

Di seguito è riportato uno schema che illustra la situazione in memoria dopo l’allocazione dello

stack (figura 3.19a) in cui si nota come cresca verso il basso. Nella figura 3.19b si può

osservare come viene utilizzato l’activation frame: il frame pointer ($fp) verrà usato per

l’accesso ai dati contenuti nel frame, lo stack pointer ($sp) è libero di variare e viene

tipicamente usato per inserire nello stack i risultati parziali nel calcolo delle espressioni(se

necessario). Nella figura 3.19c è schematizzata la situazione della memoria dopo che lo stack

è stato deallocato.

3.15

Situazione dopo

l’allocazione

dello stack

indirizzi

MEMORIA

Uso dello spazio

allocato per

l’activation frame

indirizzi

MEMORIA

“∞”

“∞”

fp

Argomento 5

Argomento 6

•••••

Registri

Salvati

Variabili

Salvate

sp

a)

Situazione dopo

la deallocazione

dello stack

indirizzi

MEMORIA

f

r

a

m

e

“∞”

sp

( fp )

Zona utilizzata

per il calcolo di

espressioni

0

b)

0

c)

0

Figura 3.19. Allocazione dello stack e del frame.

3.14 ESEMPIO 1: SOMMA ALGEBRICA

L’esempio in questione si propone di creare una procedura che svolga una somma algebrica; per

comprendere al meglio l’esempio di seguito è riportato il listato in linguaggio C.[1]

Procedura Somma_algebrica

int somma_algebrica (int g, int h, int i, int j)

{

int f;

f = (g + h) - (i + j);

return f;

}

ed ecco il listato MIPS:

#

#

#

#

g,h,i e j associati a $a0, …, $a3;

f associata a $v0

Supponiamo di utilizzare i 3 registi: $s0, $s1, $s2 nel calcolo quindi è necessario salvarne il

contenuto (in stack)

3.16

Somma_algebrica:

addi $sp,$sp,-12

sw $s0, 8($sp)

sw $s1, 4($sp)

sw $s2, 0($sp)

# alloca nello stack lo spazio per i 3 registri

# salvataggio di $s0

# salvataggio di $s1

# salvataggio di $s2

add $s0, $a0, $a1

add $s1, $a2, $a3

sub $s2, $t0, $t1

# $t0 Åg + h

# $t1 Å i + j

# f Å $t0 - $t1

add $v0, $s2, $zero

# restituisce f copiandolo nel reg. di ritorno $v0

# ripristino del vecchio contenuto dei registri estraendolo dallo stack

lw $s2, 0($sp)

# ripristino di $s0

lw $s1, 4($sp)

# ripristino di $t0

lw $s0, 8($sp)

# ripristino di $t1

addi $sp, $sp, 12

# aggiornamento dello stack per eliminare 3 registri

jr $ra

#ritorno al programma chiamante

3.15 PROCEDURE ANNIDATE

All’interno di una procedura ci possono essere delle ulteriori chiamate ad altre procedure o vi

possono essere procedure ricorsive che invocano “cloni di se stesse”; quando queste situazioni

hanno luogo è necessario fare molta attenzione all’uso dei registri. [1]

Si supponga ad esempio che il programma principale chiami la procedura “A” con un parametro

uguale a 3, mettendo il valore 3 nel registro $a0 ed usando l’istruzione jal A. Si supponga poi

che la procedura A chiami la procedura B con l’istruzione jal B passandole il valore 7, anch’esso

posto in $a0; dato che A non ha ancora terminato il proprio compito si verifica un conflitto

nell’uso del registro $a0. In modo analogo c’è un conflitto sull’indirizzo di ritorno dalla

procedura, memorizzato in $ra, perché dopo la chiamata a B esso contiene l’indirizzo di

ritorno a B; se non si adottano misure per prevenire il problema, la procedura A non sarà più in

grado di restituire il controllo al proprio chiamante.

Una soluzione consiste nel salvare nello stack tutti i registri che devono essere preservati. Il

programma chiamante memorizza nello stack i registri argomento ($a0-$a3) o i registri

temporanei ($t0-$t9) di cui ha ancora bisogno dopo la chiamata; il chiamato salva nello stack

il registro di ritorno $ra e gli altri registri ($s0-$s7) che utilizza.

Lo stack pointer $sp è aggiornato per tener conto del numero di registri memorizzati nello

stack; alla fine i registri vengono ripristinati e lo stack riaggiornato.

3.16 ESEMPIO 2: PROCEDURA RICORSIVA PER IL CALCOLO DEL

FATTORIALE

Nell’esempio che segue si mostra una procedura ricorsiva che calcola il fattoriale.[1]

Il segmento di programma può essere descritto attraverso il linguaggio c nel seguente modo:

3.17

int fact (int n)

{

if (n < 1) return (1);

else return(n * fatt (n-1));

}

Il parametro n corrisponde al registro argomento $a0. Il programma inizia con l’etichetta

della procedura, quindi salva nello stack due registri, l’indirizzo di ritorno e $a0:

fatt:

sub

sw

sw

$sp, $sp, 8

$ra, 4($sp)

$a0, 0($sp)

#aggiornamento dello stack per fare spazio a due elementi

#salvataggio del registro di ritorno

#salvataggio del parametro n

La prima volta che la procedura fatt viene chiamata, sw salva un indirizzo interno al

programma chiamante.

Le due istruzioni successive verificano se n è minore di 1, saltando a L1 se n<=1:

slt

beq

$t0, $a0, 1

$t0, $zero, L1

# test per n<1

# se n >=1 salta a L1

se n è minore di 1, fatt restituisce 1 mettendolo in un registro valore: somma 1 a 0 e lo

memorizza in $v0. Quindi ripristina dallo stack i due valori salvati e salta all’indirizzo di

ritorno:

addi

addi

jr

$v0, $zero, 1

$sp, $sp, 8

$ra

# restituisce 1

#aggiornamento dello stack per eliminare due elementi

#ritorno all’istruzione successiva a jal

prima dell’aggiornamento dello stack pointersi sarebbero dovuti ripristinare $a0 e $ra, ma

dato che non cambiano quando n è minore di 1 è possibile saltare queste istruzioni.

Se n non è minore di 1, il parametro n viene decrementato e viene nuovamente chiamata la

procedura fatt passandole tale valore:

L1:

sub

Jal

$a0, $a0, 1

fatt

# n > 1: l’argomento diventa (n-1)

# chiamata a fatt con (n-1)

L’istruzione successiva è quella a cui ritorna la procedura fatt; il vecchio indirizzo di ritorno

ed il vecchio valore del parametro sono ripristinati, oltre ad eseguire l’aggiornamento dello

stack pointer:

lw

lw

addi

$a0, 0($sp) #ritorno da jal: ripristino di n

$ra, 4($sp) #ripristino dell’indirizzo di ritorno

$sp, $sp, 8 #aggiornamento dello stack per eliminare due elementi

3.18

quindi nel registro $v0 viene memorizzato il valore del prodotto del valore corrente per il

vecchio parametro $a0:

mult

$v0, $a0, $v0

# restituzione di n*fatt(n-1)

infine la procedura fatt salta nuovamente all’indirizzo di ritorno:

jr

$ra

#ritorno al programma chiamante

3.17 DIRETTIVE DELL’ ASSEMBLATORE.

I nomi che iniziano con un punto specificano all’assemblatore come tradurre un programma ma

non generano istruzioni macchina. [1][12]

Tabella 3.3. Le direttive dell’assemblatore.

.data [<address>]

.text [<address>]

.globl <symb>

.asciiz <str>

.ascii <str>

.byte <b1>,…,<bn>

.word <w1>,…,<wn>

.float <f1>,…,<fn>

.double <d1>,…,<dn>

.half <h1>,…,<hn>

.space <n>

.align <n>

.extern <sym> [size]

.kdata [<addr>]

.ktext [<addr>]

marca l’inizio di una zona dati; se <address> viene specificato i dati

sono memorizzati a partire da tale indirizzo.

marca l’inizio del codice assembly; se <address> viene specificato i

dati sono memorizzati a partire da tale indirizzo.

dichiara un simbolo <symb> visibile dall’esterno (gli altri sono locali per

default) in modo che possa essere usato da altri file.

mette in memoria la stringa<str>, seguita da un byte ‘0’.

mette in memoria la stringa<str> e non inserisce lo ‘0’ finale.

mette in memoria gli n byte che sono specificati da <b1>,…,<bn>

mette in memoria le n word a 32 bit che sono specificate da

<w1>,..,<wn>

mette in memoria gli n numeri floating point a singola precisione (in

locazioni di memoria contigue).

mette in memoria gli n numeri floating point a doppia precisione (in

locazioni di memoria contigue).

mette in memoria le n quantità a 16 bit (in locazioni di memoria

contigue).

mette in memoria n spazi.

allinea il dato successivo ad un indirizzo multiplo di 2^n.

dichiara che il dato memorizzato all’indirizzo <sym> è un simbolo

globale ed occupa <size> byte di memoria.Questo consente

all’assemblatore di memorizzare il dato in una porzione del segmento

dati a cui si ha accesso tramite il registro $gp.

Marca l’inizio di una zona dati pertinente al kernel. Se è presente il

parametro opzionale <addr>, tali dati sono memorizzati a partire da

tale indirizzo.

Marca l’inizio di una zona contenente il codice del kernel. Se è

presente il parametro opzionale <addr>, tali dati sono memorizzati a

partire da tale indirizzo.

3.19

Esempio di utilizzo di direttive:

# Somma valori in un array

.data

array: .word 1,2,3,4,5,6,7,8,9,10

# dichiarazione array

# (array rappresenta l’indirizzo del primo elemento)

.text

.globl main

main:

li $s0,10