Politecnico di Milano

Metodologia di progetto per la

traduzione di specifiche ad alto livello

in VHDL

Relatore: prof. Fabrizio Ferrandi

Correlatore: Ing. Marco Domenico Santambrogio

Marco Losito - matr.653814

Paola Mussida - matr.650995

Sommario

• Obiettivi

• Definizioni e Teoria

• Descrizione della Metodologia

• Caso di studio: Il Calcolo del Percorso Critico

• Test e Risultati

Luglio 2004

Marco Losito – Paola Mussida

2

Obiettivi

• Definire una metodologia per la traduzione di

specifiche ad alto livello in VHDL

• Creare IP core dalla descrizione in VHDL utilizzabili

all’interno del flusso di sviluppo di sistemi dedicati

della Xilinx

Luglio 2004

Marco Losito – Paola Mussida

3

Le basi teoriche

• Metodologia:

• Macchine a stati finiti;

• Macchine a stati finiti con datapath;

• Diagrammi ASM.

• Caso di studio:

• Grafi con particolare attenzione alle Activity Network

Luglio 2004

Marco Losito – Paola Mussida

4

Macchine a stati finiti con

datapath

Luglio 2004

Marco Losito – Paola Mussida

5

Diagrammi ASM: Box

State Box

Decision Box

Condition Box

Luglio 2004

Marco Losito – Paola Mussida

6

Diagrammi ASM: Blocchi

Luglio 2004

Marco Losito – Paola Mussida

7

Diagrammi ASM: Blocchi

Luglio 2004

Marco Losito – Paola Mussida

8

Diagrammi ASM: Blocchi

Luglio 2004

Marco Losito – Paola Mussida

9

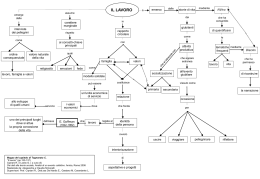

Grafi ed Activity Networks

0

1

2

3

4

5

6

7

8

9

0

-

1

3

1

-

-

-

-

-

-

1

-

-

-

-

3

-

-

-

-

-

2

-

-

-

-

5

-

-

10

-

-

3

-

-

-

-

-

-

-

1

2

-

4

-

-

-

-

-

5

-

-

-

1

5

-

-

-

-

-

-

-

-

-

7

6

-

-

-

-

-

5

-

-

-

-

7

-

-

-

-

-

-

-

-

-

5

8

-

-

-

-

-

-

3

-

-

-

9

-

-

-

-

-

-

-

-

-

-

Luglio 2004

Marco Losito – Paola Mussida

10

Metodologia: Descrizione

Algoritmo

Diagramma ASM

VHDL

Luglio 2004

Marco Losito – Paola Mussida

11

Metodologia:

Algoritmo Diagramma ASM

finchè ( z = 0 ) ripeti

{Codice}

Luglio 2004

Marco Losito – Paola Mussida

12

Metodologia:

Diagrammi ASM VHDL

Datapath1 : process (clk)

begin

if (clk'event AND clk='1') then

case current_state is

when Q0 =>

<codice>

………

when others =>

<codice>

end case;

end if;

end process Datapath1;

Luglio 2004

Marco Losito – Paola Mussida

13

Caso di studio:

Calcolo del percorso critico

•

Studio delle specifiche

•

Descrizione in linguaggio ad alto

livello

•

Stesura di diagrammi ASM

•

Traduzione in VHDL

•

Sintesi

•

Verifica e Simulazione

Luglio 2004

Marco Losito – Paola Mussida

14

Caso di studio:Definizione

• Algoritmo:

• CPM ( N, A, n0, nN, dij, tMin, tMax, LC)

• Input:

• grafo DAG=(N, A);

• nodo origine n0;

• nodo finale nN;

• Durate dij ≥ 0, (i, j) A

• Output:

• Istanti minimo e massimo di accadimento

di ogni evento;

• Lista contenente i nodi critici (LC).

Luglio 2004

Marco Losito – Paola Mussida

15

Caso di studio: Pseudocodice

Luglio 2004

Marco Losito – Paola Mussida

16

Caso di studio: Diagrammi ASM

Luglio 2004

Marco Losito – Paola Mussida

17

Caso di studio: Dagli ASM al VHDL

Luglio 2004

Marco Losito – Paola Mussida

18

Caso di studio:

Verifica e Simulazione

Luglio 2004

Marco Losito – Paola Mussida

19

Caso di studio:

Creazione dell’IP core

Luglio 2004

Marco Losito – Paola Mussida

20

Caso di studio: Dati Sperimentali

• Area

Logic Utilization:

Total Number Slice Registers: 778 out of 9,856

Number used as Flip Flops:

746

Number used as Latches:

32

Number of 4 input LUTs:

820 out of 9,856

7%

8%

Logic Distribution:

Number of occupied Slices:

1,276 out of 4,928 25%

• Tempo

Design statistics:

Minimum period: 9.982ns (Maximum frequency: 100.180MHz)

Luglio 2004

Marco Losito – Paola Mussida

21

Conclusioni

• Metodologia semplice ma efficace

• Esito positivo della validazione mediante caso di

studio

• Buoni risultati ottenuti dai test

Luglio 2004

Marco Losito – Paola Mussida

22

Scarica