POLITECNICO DI MILANO Flusso per la Creazione Automatica di Controllori per la Riconfigurazione Dinamica Andrea Cuoccio : [email protected] Paolo Roberto Grassi : [email protected] Relatore: Prof. Donatella SCIUTO Correlatore: Ing. Marco Domenico SANTAMBROGIO Indice Obiettivi Supporto per la riconfigurazione interna Internal Configuration Access Port Problematiche dei controller attuali DRESD Reconfiguration Controller Definizione del modello del DRC Modellizzazione del buffer e prime relazioni Presentazione del flusso Definizione dei vincoli Comportamento a fronte dei vincoli imposti Risultati sperimentali Conclusioni Sviluppi futuri 2 Obiettivi Definizione del flusso per la creazione automatica di controllori per la riconfigurazione Obiettivi generali Aumento della portabilità del controllore della riconfigurazione interna Identificazione delle metriche che permettono di personalizzare il controllore Obiettivi specifici Creazione di un controller adattabile al contesto Identificazione un modello che descrive in modo parametrico il comportamento del controllore 3 ICAP : Internal Configuration Access Port Porta interna all’FPGA attraverso la quale si può accedere al registro di configurazione del dispositivo Presente sulle FPGA delle famiglie Virtex-II, Virtex-II Pro, Virtex 4 e Virtex 5 Necessita di un controller che gestisca il flusso di dati da e verso il bus di sistema 4 Controller attuali 5 OPB HWICAP ICAP DRESD Interfaccia OPB slave PLB slave Dimensione pacchetti 32 bit 8 bit Protocollo Lettura ,modifica e scrittura Invio diretto del bitstream all’ICAP Memoria 512 Byte usati come cache Non necessita di memoria Problematiche dei controller attuali 6 Caratteristica Svantaggio Una sola interfaccia fissa • Scarsa flessibilità nella scelta del bus • Eventuali ritardi in caso si debba attraversare un bridge Funzionamento a 8-bit dell’ICAP_DRESD Rallentamento nel processo di invio del bitstream Protocollo read-modify-write dell’OPB_HWICAP Processo di scrittura molto rallentato dalle varie operazioni di modifica dei frame Utilizzo di una memoria di tipo e grandezza fissate Scarsa flessibilità nella scelta del tipo di memoria da utilizzare DRESD Reconfiguration Controller Interfacce su bus: PLB slave OPB slave Dimensione pacchetti: 32 bit Protocollo: invio diretto dei bitstream Dimensione memoria variabile Possibilità di scegliere come implementare la memoria: Slice BRAM 7 Definizione del Modello del DRC Il DRC è definito da due parametri: • Throughput di Riconfigurabilità (TDRC) • Occupazione di Area (A) RELAZIONI FONDAMENTALI: Nessuna formula prende in considerazione il throughput dell’ICAP. Secondo queste relazioni, esso può crescere all’infinito. 8 Definizione del Modello del DRC Formula del Throughput definitiva: 9 Flusso Operativo di DRCgen Vincoli Throughput di Riconfigurabilità Occupazione di Area 10 Risultati Sperimentali Occupazione Area Buffer in Slice Dimensione Buffer (Byte) Occupazione Area OPB (Slice) Occupazione Area PLB (Slice) 4 79 95 8 119 130 16 161 179 32 275 300 64 525 543 128 981 990 Buffer in BRAM 11 Dimensione Buffer (Byte) Occupazione Area OPB (Slice) Occupazione Area PLB (Slice) 512 (1 BRAM) 106 120 1024 (2 BRAM) 116 131 2048 (4 BRAM) 120 141 4096 (8 BRAM) 129 144 8192 (16 BRAM) 154 169 Risultati Sperimentali Throughput Throughput Bus (MByte/sec) Dimensione Bitstream (Byte) Dimensione Buffer (Byte) Throughput Simulazione (Mbyte/sec) Throughput Teorico (Mbyte/sec) 50 4000 400 55,7 55,62 50 4000 1000 66,76 66,7 50 8000 400 52,62 52,63 50 8000 2500 72,74 72,72 50 16000 400 51,29 51,28 50 16000 5000 72,74 72,72 50 16000 10000 100 100 Ticap = 100 MByte/Sec 12 Conclusioni Modellizzazione parametrica del DRC Individuazione delle metriche che descrivono lo scenario di riconfigurazione Creazione di un controllore altamente customizzabile Flusso di analisi degli scenari in grado di individuare la configurazione migliore del DRC mediante utilizzo del modello Implementazione software del modello Massimizzazione del rapporto Throughput/Area nello scenario di riconfigurazione 13 Sviluppi futuri Inserimento del DMA nel DRC Aumento del throughput di ingresso Indipendenza dal processore nel trasferimento da memoria dei bitstream Inclusione di BiRF con meccanismo di caching Possibilità di rilocazione dinamica Compressione dei bitstream 14 Domande Grazie per l’attenzione 15

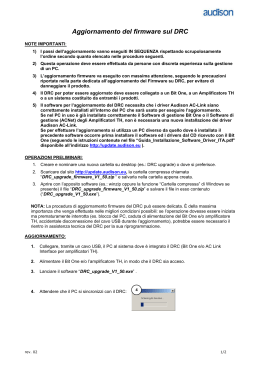

Scarica